芯片的底层就是逻辑门电路组成的,在逻辑门的基础上不断抽象,从而组成了我们使用的计算机。所以,首先我们先了解一下门电路的底层实现。

1. 门电路

1.1 与门

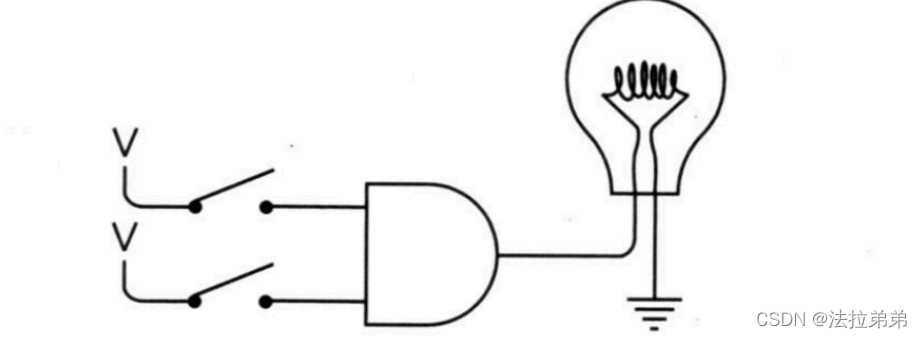

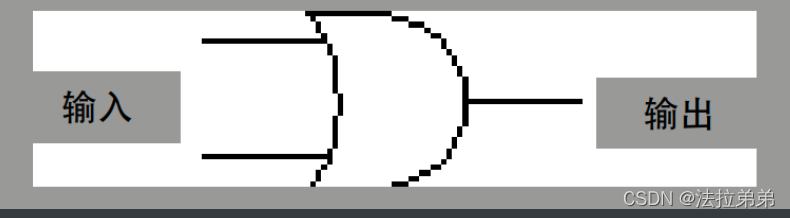

与门是两个输入,一个输出,当两个输入都是1的时候,输出才会是1,其他情况输出为0。下面通过继电器对与门的底层原理进行解释:

![]()

![]()

中学物理我们学过电磁感应,就是在线圈通电的情况下,会产生磁效应。上图中我们可以看到如果两个线圈通电的话,会分别把它们上面的开关吸下来,从而使得开关闭合,那么最终就会导致灯泡通电。

可以看到,连接灯泡的是有一个电源,这个电路上有两个开关,这两个开关是由另外两个电源控制的,所以整个电路中使用了三个电源,

简化之后的电路,是上面这个样子。可以看到,把灯泡本应该有的电源给忽略了,只剩了两个开关电源。

1.2 或门

或门也是两个输入,一个输出,两个输入中只有有至少一个为1,那么输出就是1.

或门是由四个电源组成的,两个电源是直连灯泡的,另外两个电源是连着继电器,每一个继电器控制一个灯泡电源的开关

1.3 非门

非门代表的含义是输出和输入相反,输入如果是1,那么输出就是0,如果输入是0,那么输出就是1。

非门就是继电器电源闭合,把灯泡的电源拉下来,进而灯泡电源断开;若继电器电源断开,则灯泡电源弹上去进而闭合。

1.4 异或门

上面的与或非门是最最基础的门电路,我们可以通过与或非门进行组合,产生新的门电路,比如现在讲的异或门。异或门的含义是两个输入不同的时候,输出为1,两个输入相同的时候输出为0.

2.加法器

学过计算机原理的都知道,早期的计算机的主要计算单元就是加法器,也就是说减法、乘法、除法都可以用加法器完成,那么怎么通过我们上面说的门电路组装出一个加法器呢?

我们知道,计算机的底层是通过二进制完成逻辑计算的,所以我们需要完成的加法器也是要实现二进制的加法。二进制的加法有以下几个场景:0+0=0、0+1=1、1+1=10。能看出什么迹象么?两个值相同时,输出为0,两个值不同时输出为1。是不是想到什么了?对,就是我们上面讲到的异或门的特性。说到加法,就会有进位,对于二进制来说,只有两个输入都是1的情况下,才会有进位,而这个特性刚好符合我们上面讲的与门。所以,二进制的和可以由异或门实现,而进位可以由与门实现,两者结合起来就可以完成两个二进制的加法运算。(该电路可以称为半加器)

下面是通过把半加器在继电器层级的电路画出来了,大家可以看下最基本的电路是怎么实现加法器的,这可能也是很多同学在初学计算机的时候都疑惑的地方:电路是怎么实现当前计算机这么复杂的计算的。这就是最基本的实现原理。

半加器是实现两个一位二进制数加法运算的器件,上图图就可以简化为一个半加器,如果考虑进位,就可以通过两个半加器结合实现,如下图:

3.触发器

3.1 振荡器

继电器可以实现门电路,下面我们再看一个通过继电器实现的比较骚的电路。

我们看到上面的这个电路,接通的电路使电磁铁把金属簧片拉下来,当金属簧片改变位置后,电路不再完整,电磁铁失去了磁性,金属簧片又弹回原来的位置。

电路的输出就是提供电压和不提供电压之间变换,这个电路被称为振荡器。也被称为时钟

3.2 R-S触发器

此电路有以下特性:

闭合上面的开关使灯泡点亮,当再断开时,灯泡仍然亮着。

闭合下面的开关使灯泡熄灭,当再断开时,灯泡仍然不亮。

电路的奇特之处是:有时当两个开关都断开时,灯泡亮着;而有时,当两个开关都断开时,灯泡却不亮。当两个开关都断开时,电路有两个稳定状态,这样的一个电路称为触发器。

这个电路可以记忆最近一次是哪个开关先闭合的。这种触发器被称为R-S(Reset-Set,复位/置位)触发器。

3.3 D型锁存器

这个电路被称为电平触发的D型触发器,D表示数据端输入。所谓电平触发 是指当保持位输入为某一特定电平(本例中为“ 1”)时,触发器才对数据端的输入值进行保存。它也可以称为1位存储器。

4.存储器

4.1 存储器原理

这是同一个触发器,但是现在Q输出端命名为输数输出,时钟输入端命名为写入。该电路也叫锁存器。

8个这样的锁存器连在一起,就是8为输入输出。

如果8个中选择一个输出,怎么办?看下图,这是8-1选择器。

下面这个是3-8译码器

8个锁存器的完整电路如下

简化图如下:

4.2 大内存实现原理

我们上一节看到,8位容量的锁存器就有很多条线。但是在真实的计算机中,我们的内存都是以G为单位的,如果按照上一节讲的方法,扩展出来真实可用的物理内存,那么线路复杂度是超过人的想象的。

为了解决大内存的布线问题,工程师们想到了矩阵的方式,也就是以矩阵的形式摆放一个一个锁存器,如下图所示:

也就是以地址线决定是否可写入读出,上图中,横着的地址线和纵向的地址线都是1的情况下,才能选中这个锁存器,这个时候再看write和read信号,来决定是否可写入或读出。

把内存布局抽象一层,我们可以由如下图示进行表示

以上的描述,一个地址只能写入或读出1位数据,如果想要同时写入或读出一个byte的数据,也就是8位,怎么办呢?很简单,把地址线同时连8个像上面的内存就行了,如下图:

4.3 真实物理内存条

该内存条有1M的容量,通过对内存条逐步放大,我们看下其工艺实现。

其中一个小黑条放大之后如下:

其中一个小四方块放大之后如下:

其中每个四方块放大之后如下:

参考:

1. 《编码》

2. 【计算机科学速成课】[40集全/精校] - Crash Course Computer Science_哔哩哔哩_bilibili