随着计算机应用领域的不断扩大,处理的信息量越来越多,并且现代计算机的I/O设备也在不断增加,因此,提高访存的速度已经成为了迫不及待的任务。于是就出现了并行存储器。

在介绍并行存储器之前,先来介绍一个概念:

**存储器的带宽:表示单位时间内存储器存取的信息量,可用字/秒或者位/秒表示。是衡量数据传输率的重要技术指标。**存储器的带宽是决定了以存储器为中心的机器获得信息的速度。可以通过下面的几种方式提高:

- 缩短存取周期

- 增加存储字长

- 增加存储体

双口RAM

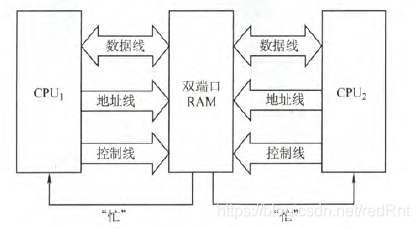

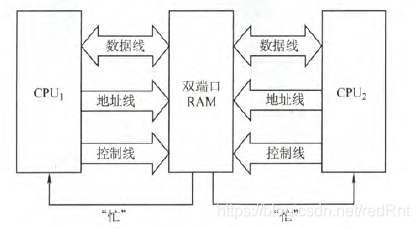

为了提高CPU访问存储体的速度,可以采用双端口的存储器,多模块存储器等技术,它们同属于并行技术。前者为空间并行,后者为时间并行。双口RAM的模型图如下:

该模型允许两个独立的控制器同时异步地访问存储单元。但是这种方式有时也会带来一些读取错误。例如:

- 两个端口对同一个地址单元写入

- 两个端口对同一地址单元,一个写入,一个读出。

(熟悉操作系统的朋友应该能看出来,这是个读者写者问题的模型),通常的处理方式是设立一个置忙信号Busy,当遇到上述状况的时候,将busy置0.暂时关闭一个端口。

可以看出,这是一个从空间上并行的存储技术。

多模块存储器

我们还可以从时间上并行并行存取。我们知道CUP的速度要比存储器要快,如果我们同时从存储器中取出几条指令,那么我们就可以充分利用CPU资源,提高运行效率。

多体并行存储器,由多体模块构成,每个模块都有相同的容量和存取速度,有独立的读写控制电路,地址寄存器和数据寄存器。

多体并行存储器分为高位交叉编址和低位交叉编址两种。

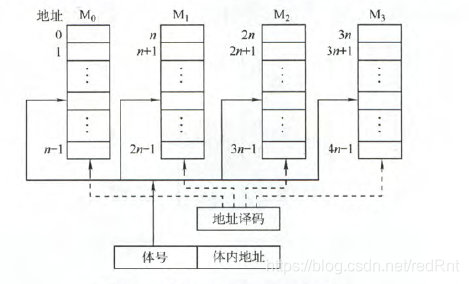

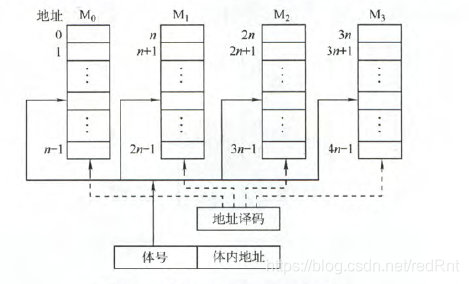

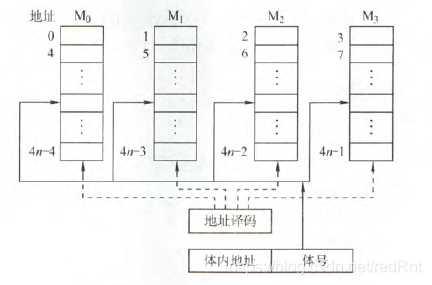

高位交叉编址

当程序按体内地址顺序存放,即一个体存满之后,再存入下一个体时,这种方式称为顺序存储,高位地址表示题号,低位表示体内地址(注意0 1 2 3…的顺序是从上往下的):

因此,CPU给出一次存储访问总是对一块连续的存储单元进行的,在多CPU系统中,不同的CPU访问不同的存储块,达到并行工作。

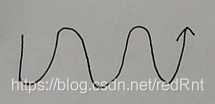

访存轨迹可以用下面的线条表示:

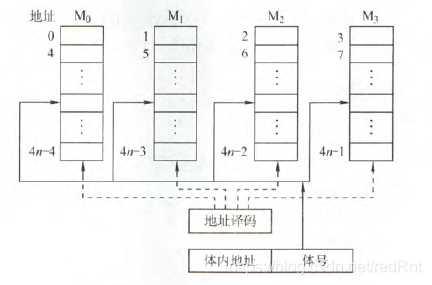

低位交叉编址

对应于高位交叉编址,低位交叉编址指的是将程序连续存放在相邻体中,又称交叉存储。(注意,0 1 2 3的顺序是从左往右的)

这种做法可以在不改变存取周期的前提下,提高存储器带宽,因为可以在一个访问周期下,访问多个不同的存储体。适用于单处理器系统

访存轨迹可以用下图表示:

访存冲突

但是低位交叉存储可能导致访存冲突,当访存地址在相邻的四次访存中,出现在同一存储块内,就会发生访存冲突。

比如,下面有一组将要访问的地址序列(3 9 17 2),采用的是4体低位交叉存储(即4个存储体,从0开始编号)。

我们可以通过计算得知3,9,17,2分别位于存储体3,1,1,2.

由于我们的访存方式是一次性访问多个不同的存储体,比如这个是4体,一次性同时访问4个不同的体,那么就分别是 0,1,2,3,及其对应的其他存储单元。

由于访问的顺序存在体数重合,因此有一次访问是一定失败的,这就是访问冲突。

那么如何算给定访问序列的所在体数呢?

所在体数 = 序列号mod体数,比如3%4 = 3,9%4 = 1

两种并行存储器的访问时间

设存储器的模块数为n,存取周期为T,总线传输周期为i,当采用流水线方式存取的时候,:

- 若采用高位交叉编址,那么连续读取n个字节所需的时间t1为: t1 = nT

- 若采用低位交叉编址,那么连续读取n个字节所需的时间t2为:t2 = T +(n - 1 )i

- 存储器的交叉模块数 m >= T/i

随着计算机应用领域的不断扩大,处理的信息量越来越多,并且现代计算机的I/O设备也在不断增加,因此,提高访存的速度已经成为了迫不及待的任务。于是就出现了并行存储器。

在介绍并行存储器之前,先来介绍一个概念:

**存储器的带宽:表示单位时间内存储器存取的信息量,可用字/秒或者位/秒表示。是衡量数据传输率的重要技术指标。**存储器的带宽是决定了以存储器为中心的机器获得信息的速度。可以通过下面的几种方式提高:

- 缩短存取周期

- 增加存储字长

- 增加存储体

双口RAM

为了提高CPU访问存储体的速度,可以采用双端口的存储器,多模块存储器等技术,它们同属于并行技术。前者为空间并行,后者为时间并行。双口RAM的模型图如下:

该模型允许两个独立的控制器同时异步地访问存储单元。但是这种方式有时也会带来一些读取错误。例如:

- 两个端口对同一个地址单元写入

- 两个端口对同一地址单元,一个写入,一个读出。

(熟悉操作系统的朋友应该能看出来,这是个读者写者问题的模型),通常的处理方式是设立一个置忙信号Busy,当遇到上述状况的时候,将busy置0.暂时关闭一个端口。

可以看出,这是一个从空间上并行的存储技术。

多模块存储器

我们还可以从时间上并行并行存取。我们知道CUP的速度要比存储器要快,如果我们同时从存储器中取出几条指令,那么我们就可以充分利用CPU资源,提高运行效率。

多体并行存储器,由多体模块构成,每个模块都有相同的容量和存取速度,有独立的读写控制电路,地址寄存器和数据寄存器。

多体并行存储器分为高位交叉编址和低位交叉编址两种。

高位交叉编址

当程序按体内地址顺序存放,即一个体存满之后,再存入下一个体时,这种方式称为顺序存储,高位地址表示题号,低位表示体内地址(注意0 1 2 3…的顺序是从上往下的):

因此,CPU给出一次存储访问总是对一块连续的存储单元进行的,在多CPU系统中,不同的CPU访问不同的存储块,达到并行工作。

访存轨迹可以用下面的线条表示:

低位交叉编址

对应于高位交叉编址,低位交叉编址指的是将程序连续存放在相邻体中,又称交叉存储。(注意,0 1 2 3的顺序是从左往右的)

这种做法可以在不改变存取周期的前提下,提高存储器带宽,因为可以在一个访问周期下,访问多个不同的存储体。适用于单处理器系统

访存轨迹可以用下图表示:

访存冲突

但是低位交叉存储可能导致访存冲突,当访存地址在相邻的四次访存中,出现在同一存储块内,就会发生访存冲突。

比如,下面有一组将要访问的地址序列(3 9 17 2),采用的是4体低位交叉存储(即4个存储体,从0开始编号)。

我们可以通过计算得知3,9,17,2分别位于存储体3,1,1,2.

由于我们的访存方式是一次性访问多个不同的存储体,比如这个是4体,一次性同时访问4个不同的体,那么就分别是 0,1,2,3,及其对应的其他存储单元。

由于访问的顺序存在体数重合,因此有一次访问是一定失败的,这就是访问冲突。

那么如何算给定访问序列的所在体数呢?

所在体数 = 序列号mod体数,比如3%4 = 3,9%4 = 1

两种并行存储器的访问时间

设存储器的模块数为n,存取周期为T,总线传输周期为i,当采用流水线方式存取的时候,:

- 若采用高位交叉编址,那么连续读取n个字节所需的时间t1为: t1 = nT

- 若采用低位交叉编址,那么连续读取n个字节所需的时间t2为:t2 = T +(n - 1 )i

- 存储器的交叉模块数 m >= T/i