文章目录

1.AXI接口引入

zynq上有一块ARM硬核,这样的板子称之为SOC系统,想要把我们的电路在SOC系统中用起来,还需要将写好的模块的端口设置为AXI接口。

(1)将端口设置为AXI接口

将A设置为 从axi,CPU作为主机,CPU将数据通过AXI接口发给从机A。

同样B、C也选成s_axilite

Synthesis结果,可见原来的ABC都变成了s_axi_AXILiteS端口

但此时模块的工作依旧是start和done信号控制的,我们希望换成CPU控制。需要对模块的启动方式进行约束。

(2)对模块的启动方式进行约束

右击matrix_mul,进入约束界面。

选择如下

Synthesis结果

start和done信号就没了,交由axi通过cpu控制了。

接下来我们想在系统中使用我们设计的模块。

2.hls生成RTL

点击Export RTL

点击ok

生成RTL过程

Starting export RTL ...

Task has been canceled!

Starting export RTL ...

D:/Xilinx201901/Vivado/2019.1/bin/vivado_hls.bat D:/xxxx/hls/matrix/matrix/solution1/export.tcl

INFO: [HLS 200-10] Running 'D:/Xilinx201901/Vivado/2019.1/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'summer' on host 'desktop-dck1feh' (Windows NT_amd64 version 6.2) on Sat Mar 13 19:35:45 +0800 2021

INFO: [HLS 200-10] In directory 'D:/xxxx/hls/matrix'

Sourcing Tcl script 'D:/xxxx/hls/matrix/matrix/solution1/export.tcl'

INFO: [HLS 200-10] Opening project 'D:/xxxx/hls/matrix/matrix'.

INFO: [HLS 200-10] Opening solution 'D:/xxxx/hls/matrix/matrix/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 30ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020-clg400-1'

INFO: [IMPL 213-8] Exporting RTL as a Vivado IP.

****** Vivado v2019.1 (64-bit)

**** SW Build 2552052 on Fri May 24 14:49:42 MDT 2019

**** IP Build 2548770 on Fri May 24 18:01:18 MDT 2019

** Copyright 1986-2019 Xilinx, Inc. All Rights Reserved.

source run_ippack.tcl -notrace

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx201901/Vivado/2019.1/data/ip'.

INFO: [Common 17-206] Exiting Vivado at Sat Mar 13 19:35:56 2021...

Finished export RTL.

btw,同时自动生成了C语言的驱动

3.通过vivado验证设计的RTL模块

打开vivado,新建platform的文件夹,将vivado工程新建到此文价夹下,工程名也叫platform,一路next,选择pynq-z2的板子。

create block design

点击加号,搜索zynq,并双击选择。

点击 run block automation

点击ok

实现自动连接,结果如下

之所以会自动连接,与我们之前选的板子有关,我们选择的pynq-z2,这块板子的信息在工具里已经加载进来了。可以点击setting来查看

(1)添加我们之前生成的IP模块

选择Matrix_mul,点击ok

然后再将我们的乘法器核添加进来。

点击 run block automation

点击regenera layout

点击validation验证

然后按CTRL+S保存工程

还要进行下述操作,每次修改设计后都要进行如下操作。

点击ok

generate bitstream

FPGA设计就完成了。

pynq架构介绍

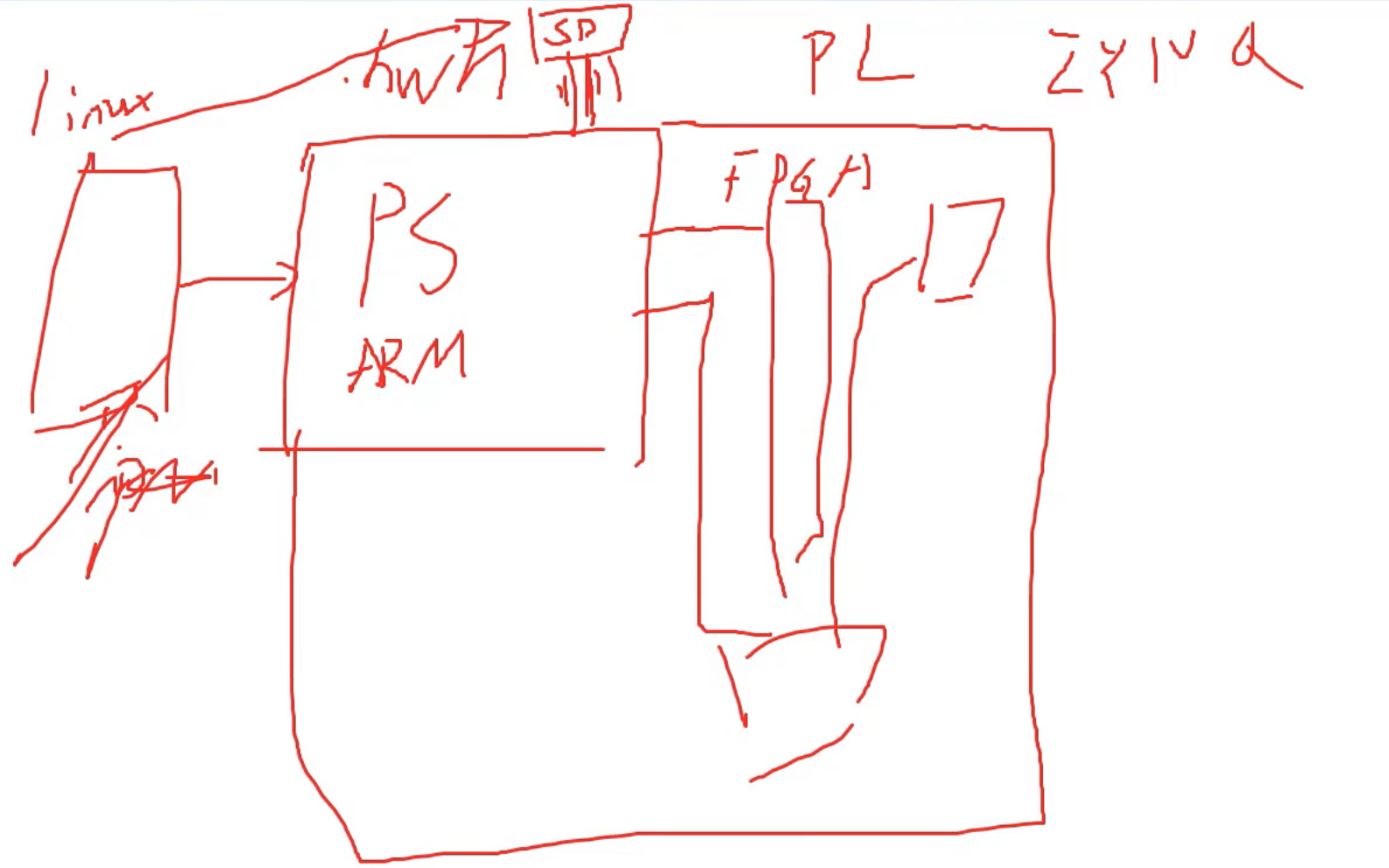

PS指arm核,PL指FPGA,zynq核pynq的启动流程:上电之后arm上运行linux系统(该系统从SD卡加载),可以通过电脑端的网页连接到linux系统对arm进行控制,把前面生成的bitfile拷贝到linux系统里,利用python脚本就可以对FPGA进行烧写,把bitfile烧写进FPGA,FPGA就变成了我们设计成的样子。但是arm仅仅负责烧写,它还并不知道FPGA的电路情况,还需要一个文件在hw_handoff文件夹下的design_1.hwh,arm通过读取这个文件获取FPGA的电路情况,包括我们设计的IP核。这块板子的linux操作系统叫做pynq,这是pynq的来源。

按照这篇博客将pynq操作系统搭建起来:pynq-z2入门

在linux中新建工程

(1)将vivado中生成的hwh和bit文件拷贝到linux工程文件夹中

通过192.168.2.99连接到linux文件夹,在jupyter_notebooks下新建文件夹hls_advance,hls_advance新建文件夹1_matrix_mul,里面放我们的工程。

把vivado工程里的design_1.hwh拷贝到1_matrix_mul中去。

把vivado工程里的design_1_wrapper.bit拷贝到1_matrix_mul中去。

1_matrix_mul文件夹下目前的文件。

这两个文件名字应该一样。

rename

(2)新建python3脚本

使用python3脚本将这两个文件烧录到fpga中去

新建python脚本:

btw:shif+enter 运行

【1】加载bit文件

python3编程需要从hls工程中的驱动文件xmatrix_mul.h这个文件找变量的地址信息。

【2】初始化要处理的数据数组AB

注意python中组合四个字节的方式与reshape的维度与有关

A:

for i in range(4):

tp=0

for j in range(4):

tp=tp|A[i][j]<<(8*j) #python中一次性写4个字节,这里将四个字节拼接成一个tp

matrix_mul.write(0x10+4*i,int(tp)) # 这里i的单位是1字节,相当于8位

B:

for i in range(4):

tp=0

for j in range(4):

tp=tp|B[j][i]<<(8*j)

matrix_mul.write(0x20+4*i,int(tp))

【3】启动

通过对起动信号置1启动

matrix_mul.write(0,1)

【4】读取结束信号

读取计算完成信号

tp=matrix_mul.read(0)

刚才已经读出tp了,done会重新清零,所以要restart & Clear Out

【5】读取ip核的计算结果,读取数组C

C的结构

for i in range(4):

for j in range(2):

C[i][2*j]=matrix_mul.read(0x40+4*(2*i+j))&0xffff;

C[i][2*j+1]=matrix_mul.read(0x40+4*(2*i+j))>>16;

完整代码:

和hls中的测试结果一致,实现了在cpu中给数据,控制启停,并接受数据。测试成功。