这里讲的数组是指顶层函数的参数。

默认情况下数组会映射为相应的 memory 端口,这些端口会包括一些控制信号,如读写、使能,读写地址,还有相应的数据端口。也可以在 Vivado HLS 中设定是用单端口的 RAM 还是双端口的 RAM,通常情况下 Vivado HLS 会自动分析哪种类型能获得最大的数据速率。

- 可以指定单双端口

- FIFO

- 数组分区(后续增加)

如果手动指定了双端口接口,但是 Vivado HLS 分析只需单端口就可以满足,则最终会以单端口实现。

不管数组(输入、输出或者双向数组)类型如何,ap_memory 都是默认的接口协议。

在上述示例中,综合后的各参数含义如下:

d_i_address0:提供存储该数组 memory 的地址以供读取数据

d_i_ce0:片选信号

d_i_q0:输入数据端口,数据来自于外部 memory

d_o_address0:需要写的 memory 的地址

d_o_ce0:片选信号

d_o_we0:写使能信号

d_o_d0:输出数据到外部 memory

FIFO

ap_fifo

system generator

添加寄存器

对输入输出端口添加寄存器是解决时序收敛问题的有效方式,默认情况下 Vivado HLS不会添加寄存器。

对顶层函数接口综合时,选择了register 后还要选择端口 port 选项。

在添加端口寄存器的时候,需要保证 block-level interface protocol 必须是 ap_ctrl_hs

添加时钟使能

时钟使能信号的作用就是让所有电路在使能的情况下才能工作,Vivado HLS 默认是不会添加时钟使能信号的。添加方法就是右击 solution,选择 solution settings,在 General 选项中点击 Add 按钮,

指令优化

在做指令优化时有两个主要原则,一个是要更低的 latency,一个是要更少的 IO

对 for 循环 pipeline 来降低 latency(directive),但是这样往往会增加 IO 的数量,因为 pipeline 之后 Vivado HLS 会将数组使用双端口 RAM 实现。

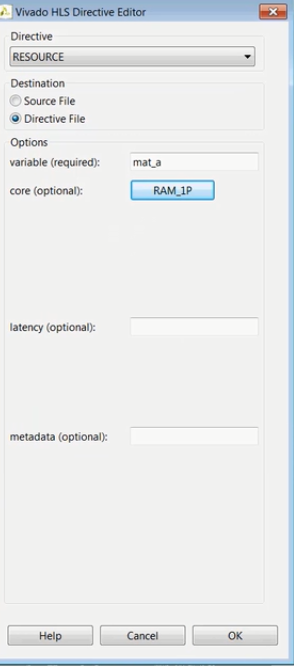

这时就可以对数组使用 RESOURCE 指令优化来设置 RAM 为单端口模式。

设置全局使能信号

ap_ce