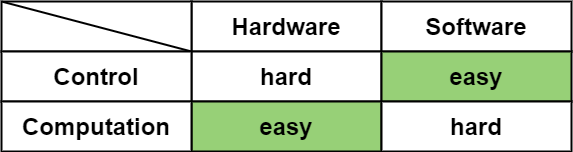

1.软件和硬件就像太极中的阴阳元素一样,你中有我,我中有你,不断演化,彼此渗透又隔离,但总体上看,从控制和计算两个主要维度来讲,软件擅长于控制而非计算,硬件则相反,所以,设计系统的一个大的目标就是要让合适的组件做擅长的事情,在这样的系统中,软件就像大脑一样,统筹全局,运筹帷幄,对整个处理器资源统一调配,而且硬件则发挥领域内的计算优势,对各种具体的应用场景进行加速,所以各种各样的处理器就出来了,比如有擅长做视频编解码的VPU,也有擅长做图形处理的GPU,G2D, 适合做矩阵运算的TPU, 还有各种AI加速单元等等,这些单元可以提供领域内的专用算例,而用软件提供这些算力是非常困难和低效。 通用算力IP作为软件的载体,定义则越来越抽象,越来越灵活。

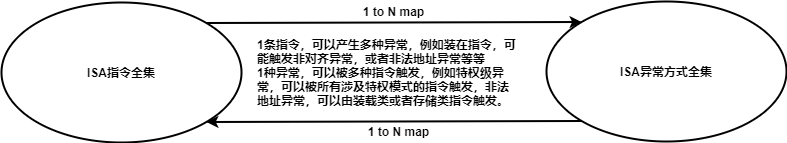

2.关于异常和指令关系的总结

3.关于异常和中断

异常处理,包括指令异常和外部中断,是处理器的一项重要技术,在异常事件产生时,用来使处理器转入对异常事件的处理,异常处理是处理器根据内部或外部的异常事件从正常的程序处理转入特定的异常处理程序,引起异常的外部事件包括,外设中断,总线错误,引起异常的内部事件包括:非法指令和非对齐访问等等,还有某些调试或者系统调用指令等产生异常。异常处理机制利用异常向量表跳转到异常服务程序的入口。异常处理的关键是在异常发生时,保存CPU当前指令运行的状态,在退出异常时恢复异常处理前的状态。异常能够在流水线的各个阶段被识别,并使后面的指令不会改变CPU的状态(当然可以改变流水线的状态,但流水线对ISA之上不可见),异常在指令的边界上被处理,即CPU在指令退役时响应异常,并保存退出异常处理时吓一跳被执行的指令地址。即使异常指令退休前被识别,异常也要在相应的指令退休时才会被处理。处理器根据异常识别时的指令是否完成决定异常地址寄存器存储哪一条指令的地址,例如,如果异常事件是外部中断服务请求,被中断的指令将正常退休并改变CPU状态,它的下一条指令地址将被保存起来,如果异常是由于访问错误指令引起,因为这条指令不能完成,它将退役但是并不改变CPU的状态,也就是不改变寄存器的值,这条非法指令的地址将被保存在返回寄存器中,如果CPU能够从这次异常中恢复,它将继续执行这条出错的指令,当然非法指令访问多少次都是非法,这个例子对其它异常,比如浮点算法更合适。

异常没有使能寄存器,因此一旦触发异常即可进行响应,但是中断优先级一般高于异常优先级,异常内部也分优先级。