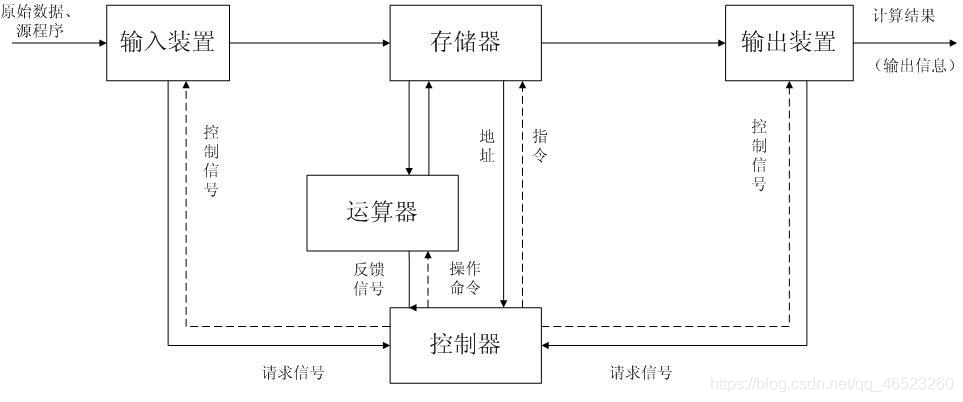

冯·诺依曼结构(von Neumann architecture)

• 冯·诺依曼结构也称作普林斯顿结构,是一种将程序(指令序列的集合)和数据存放在同一存储器的不同地址的电脑设计概念结构。这是建立在冯·诺依曼原理,即程序可看做一种特殊的“数据”,同样地可以被处理和存储,故两者可存放在同一存储器中,采用单一的地址总线和数据总线。

• 目前的PC机都是基于冯·诺依曼结构

• 特点:

- 程序和数据存放在同一存储器的不同地址上,程序指令和数据的宽度相同。

- 存储单元线性排列,且其位数固定

- 顺序执行,即程序/数据—>内存—>取指令执行指令;

执行前,将需要的程序和数据先放入存储器(PC为内存)。当执行时把要执行的程序和要

处理的数据按顺序从存储器中取出指令一条一条地执行。 - 组成上有运算器,存储器,控制器,输入/输出设备。

•CPU能且只能对内存进行读写,不能访问外设(输入或输出设备)。

•CPU能且只能对内存进行读写,不能访问外设(输入或输出设备)。

•外设(输入或输出设备)要输入或输出数据也只能写入内存或从内存中进行读取。

•所有设备都只能直接跟内存打交道

哈佛结构

• 哈佛结构是一种将程序指令储存和数据储存分开的存储器结构,是一种并行结构。

• 哈佛结构的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问,目的是为了减轻程序运行时的访存瓶颈。

• 指令和数据存储器地址独立编码

• 哈佛结构的中央处理器首先到程序指令储存器中读取程序指令内容,解码后得到数据地址,再到相应的数据储存器中读取数据,并进行下一步的操作(通常是执行)。

• 数据和指令的储存可以同时进行,可以使指令和数据有不同的数据宽度。

• 其程序指令和数据指令分开组织和储存的,执行时可以预先读取下一条指令

CACHE高速缓存

CACHE:

• 为了解决CPU和主存之间速度不匹配而采用的一项重要技术。

• 介于CPU和主存M2之间的小容量存储器

• 存取速度比主存快,一般采用高速的SRAM构成。

• 现代PC机实际上是冯氏结构+哈佛结构的复合体(ICACHE+DCACHE)。

指令流水线

• 流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,他们可同时为多条指令的不同部分进行工作,已提高各部件的利用率和指令的平均执行速度。

• 把一个重复的过程分解为若干个子过程,每个子过程由专门的功能部件来实现。

• 把多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其他的子过程并行进行。

• 缺点

• 并发导致每一条指令的执行时间变长

• 优化难度大,有时候两行代码的顺序变动就可能导致数倍的性能差异

• 如果多次分支预测失败,会导致严重的性能损失

分支预测

• 指令形成流水线以后,就需要一种高效的调控来保证硬件层面并发的效果:最佳情况是每条流水线里的十几个指令都是正确的,这样完全不浪费时钟周期。

• 分支预测器猜测条件表达式两路分支中哪一路最可能发生,然后推测执行这一路的指令,来避免流水线停顿造成的时间浪费。但是,如果后来发现分支预测错误,那么流水线中推测执行的那些中间结果全部放弃,重新获取正确的分支路线上的指令开始执行,这就带来了十几个时钟周期的延迟,这个时候,这个CPU 核心就是完全在浪费时间。

• 幸运的是,当下的主流 CPU 在现代编译器的配合下,把这项

工作做得越来越好了。