转自:https://blog.csdn.net/qq_26652069/article/details/90611519

1. 创建综合运行

一个“运行”(Run)是指定义和配置综合过程中的各个方面,包括:使用的Xilinx器件、应用的约束集、启动单个或多个综合的选项、控制综合引擎结果的选项。点击Flow菜单中的Create Funs:

或在Design Runs窗口中:

2. 综合方式选择

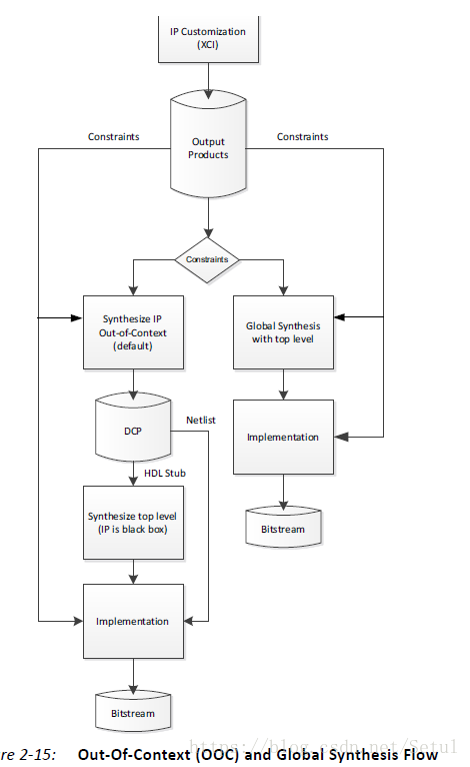

针对定制IP时候,会有一个综合方式(Synthesis Options)的选择:Global和Out-of-context,如下图

Global模式

如果选择的是全局综合选项,那IP生成的文件将会和其他的用户文件一起进行综合,这也就意味着,每一次用户文件被修改后,IP都会跟着一起综合一遍。

OCC模式

OOC是Vivado开发套件提供的一项技术,该综合模式本质上是一种自底向上(bottom-up)的综合方法,该方法可用于IP、IPI(IP Integrator)的Block Design以及选择将HDL对象(即用户逻辑)当作一个隔离模块运行 完成自底向上的综合流程。

针对定制IP

由于不需要每次综合时都运行整个设计,这项技术可以大大减少顶层模块的综合运行时间。IP核就是典型的采用OOC技术的代表,配置好IP核后可以选择综合模式为global(与顶层设计一起综合)或Out-of-context(作为独立模块综合),最好的做法就是选择后者,以减少整体设计的综合运行时间。

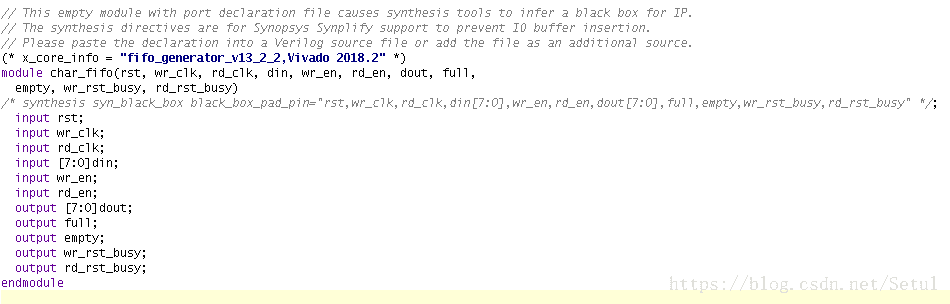

OOC选项是Vivado给我们的默认选项,在OOC模式下,Vivado将会把生成的IP当成一个单独的模块来进行综合,生成.dcp (design checkpoint)文件。同时会使用一个只在OOC模式下有用的约束文件“_ooc.xdc”。 除了生成.dcp文件,OOC还会生成一个以”stub”结尾的HDL文件,是当前IP设计的一个黑盒文件,其实就是只有输入输出端口,没有其他内容,如下图所示是一个FIFO IP的”char_fifo_stub.v”实例。这个文件的作用就是跟着工程中的其他文件一起进行综合过程。

最后,在”implementation”阶段,OOC生成的.dcp文件中的网表文件将和其他设计文件综合后生成的网表文件一起。

OOC具有如下的特点:

- 底层的OOC模块相对于顶层模块独立运行,并拥有自己的约束集合;

- 运行了OOC模块之后,再运行顶层模块综合时可直接调用OOC综合结果,而不需要重新运行一次综合(除非修改了RTL设计或约束)。

针对用户逻辑

选择需要添加到OOC运行的模块,右键->Set As Out-Of-Context for Synthesis,弹出如下窗口:

其中Clock Constraint File必须创建一个新的XDC文件或在下拉菜单中选择一个已经存在的XDC文件,该约束文件中要有该模块时钟信号的相关约束。点击OK后,该模块会出现在Design Runs窗口的Out-of-Context Module Runs目录中,还有Compile Order窗口的Block Sources目录中。

当运行了OOC综合后,会产生底层模块的综合网表和存根文件(stub文件)。存根文件仅描述了底层模块的输入和输出,在综合顶层模块时,通过存根文件来调用底层模块,模块内部当作黑盒子看待。运行实现时,Vivado会将OOC模块的综合网表插入到顶层网表中,从而完成设计。

导入网表文件

可以通过 实例化低层次网表 或第三方网表来手工构造一个自底向上的设计流程。但需要知道,Vivado综合工具不会综合和优化网表,因此XDC约束和综合属性也不会对导入的网表产生作用。事实上,Vivado综合时既不会读取也不会修改网表中的内容。可以按照如下流程完成相关处理:

- 创建低层次网表:创建一个工程,以要导入的网表作为顶层模块,将Settings->Synthesis->More Options设置为**-mode out_of_context**。这样综合时不会为该模块产生I/O缓存器。综合后,在Tcl控制台输入write_edif name.edf。

- 设计中实例化低层次网表:顶层设计需要将低层次模块作为黑盒子实例化,类似于前面提到的stub文件。因此需要创建一个Verilog/VHDL文件,仅定义网表的端口,信号名称必须与网表中的端口名称完全匹配。

- 组合为完整设计:当创建了OOC模式的低层次网表,并且在顶层设计中正确地实例化后,将第一步导出的edif网表添加到工程中。综合后,Vivado会将网表合并到顶层设计中。

Vivado IP和第三方综合工具

大多数Xilinx发布的IP核采用IEEE P1735进行加密,只有Vivado综合工具才支持对IP核的综合,第三方综合工具不能综合Vivado中的IP核。如果想把Vivado中的IP核在第三方综合工具中实例化,可以参考如下步骤:

在Managed IP工程中(Vivado首页->Tasks->Manage IP)创建并配置好IP核。

生成IP核的输出文件,包括综合设计检查点(DCP文件)。Vivado会创建一个stub文件(*_stub.v/*_stub.vhd),该文件会包含一些指令阻止从该文件中推断出I/O缓存器。根据使用的第三方综合器可能需要修改此文件。

使用Vivado综合带有stub文件的Xilinx IP核。

使用第三方综合工具产生的网表和Xilinx IP核的DCP文件一起运行实现步骤