halo~我是bay_Tong桐小白

本文内容是桐小白个人对所学知识进行的总结和分享,知识点会不定期进行编辑更新和完善,了解最近更新内容可参看更新日志,欢迎各位大神留言、指点

总线系统总结——基本知识要点汇总

【更新日志】

最近更新:

- 更新内容——更新总线仲裁、总线标准部分相关内容(2021.1.29)

- 持续更新中……

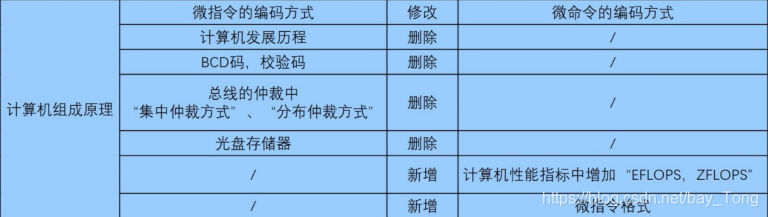

计算机统考408考纲要求

2021计算机统考408考纲计算机组成原理学科考察目标

- 理解单处理器计算机系统中各部件的内部工作原理、组成结果以及相互连接方式,具有完整的计算机系统的整机概念

- 理解计算机系统层次化结构概念,熟悉硬件与软件之间的界面,掌握指令集体系结构的基本知识和基本实现方法

- 能够综合运用计算机组成的基本原理和基本方法,对有关计算机硬件系统中的理论和实际问题进行计算、分析,对一些基本部件进行简单设计,并能对高级程序设计语言(如C语言)中的相关问题进行分析

2021计算机统考408计算机组成原理考纲变动情况

2021计算机统考408考纲对总线系统部分考察要求

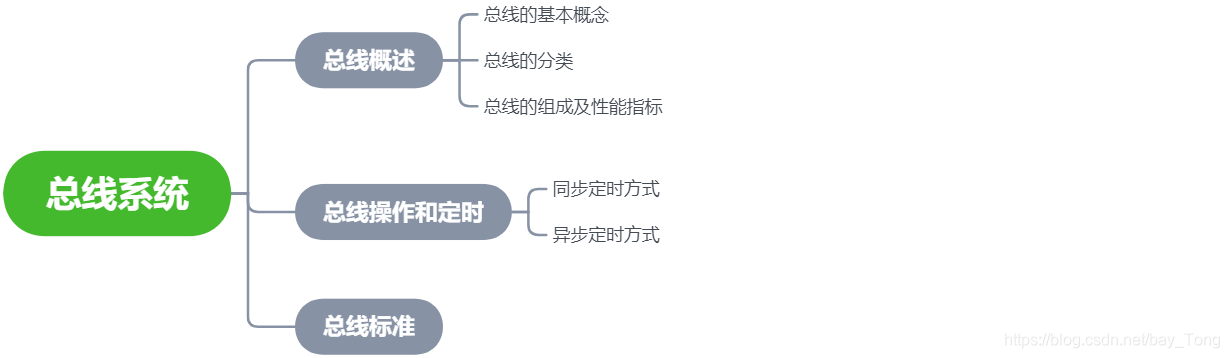

总线概述

总线基本概念

总线概念:

- 连接各个部件的信息传输线,是各个部件共享的传输介质,信号的公共传输线

- 同一时刻只能有一对设备或一对部件进行信息通讯,其它部件需等待其释放总线使用权

- 作用

○ 各功能部件间传递各类信息的通道

○ 各部件间的物理接口,能减少各部件通信的复杂程度

○ 提供信息交换时所需的数据、地址、时序、控制信息

○ 提供一个共同遵循的协议或标准

○ 不应成为整个计算机性能的瓶颈

○ 方便计算机系统的集成、扩展、进化

总线上信息的传送方式:

- 串行:逐位放在总线上传送、逐位接收

- 并行:多位同时放在总线上进行传输、多位同时接收。

○ 需要多条数据线

○ 在传输距离较大时,线与线之间容易产生干扰,信号易变形 - 一般并行支持的距离短,串行支持的距离长

总线分类

根据总线的位置可划分:

- 片内总线(内部总线):芯片内部的总线(CPU内部连接各寄存器及运算器部件之间的总线)

- 系统总线(外部总线):计算机各种部件之间的信息传输线,一般所说的总线主要就是指系统总线

○ 数据总线(DB):数据信号,双向,与机器字长、存储字长有关

○ 地址总线(AB):单向,与存储地址、I/O地址有关,通常与地址单元的个数相关

○ 控制总线(CB):有出(存储器读/写、总线允许、终端确认等)有入(中断请求、总线请求等)。向系统各个部件传输控制信号/系统各个部件将自己的状态信号传给其它部件 - 通信总线(I/O总线):中低速I/O设备相互连接的总线,即用于计算机系统之间或计算机系统与其他系统(如控制仪表、移动通信等)之间的通信

○ 传输方式:串行通信总线、并行通信总线

○ 串行通信方式有2种:同步方式、异步方式(详细见总线通信控制部分)

总线特性及性能指标

总线特性:

- 机械特性:尺寸、形状、管脚数、排列顺序等总线物理连接方式

- 电气特性:传输方向、有效的电平范围

- 功能特性:每根传输线的功能(地址信号、数据信号、控制信号、状态反馈信号)

- 时间特性:信号的时序关系

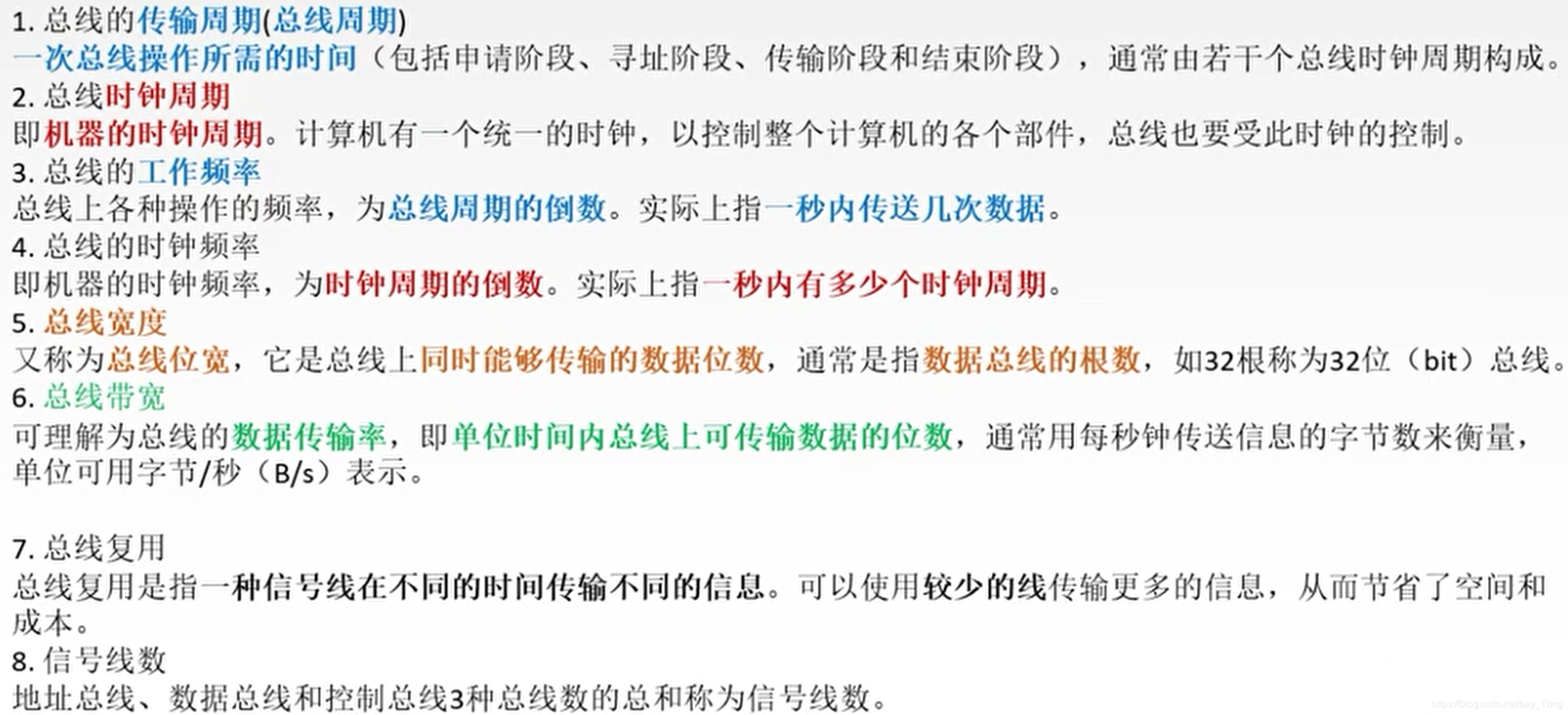

总线的性能指标:

- 总线带宽 —— 总线本身所能达到的最高传输速率,单位兆字节每秒(MB/s),与数据线的根数有关

总线频率(f):反映总线工作速率,通常单位MHz

总线宽度(w):数据总线的位数,通常与处理器的字长一致

总线传输速率(BW):总线上可传输的数据总量,单位MB/s。总线传输速率=(总线宽度÷8位)x 总线频率 - 标准传输率 —— 每秒传输的最大字节数

- 时钟同步/异步 —— 同步、不同步

- 总线复用 —— 地址线与数据线复用

- 信号线数 —— 地址线、数据线、控制线的总和

- 总线控制方式 —— 突发、自动、仲裁、逻辑、计数

- 其他指标 —— 负载能力

总线结构

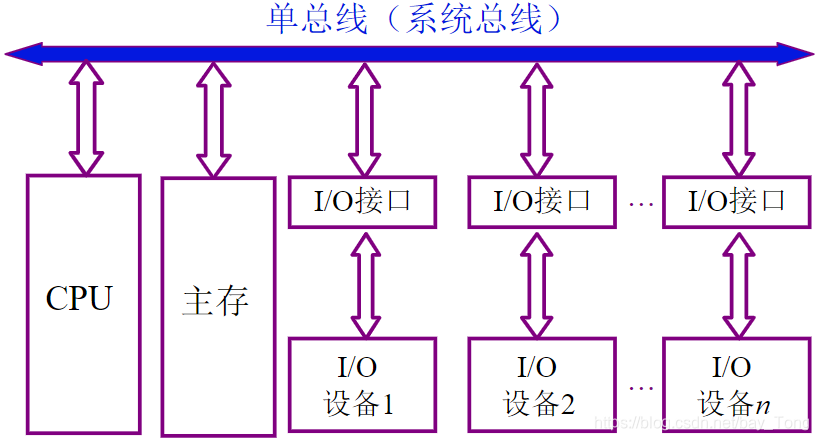

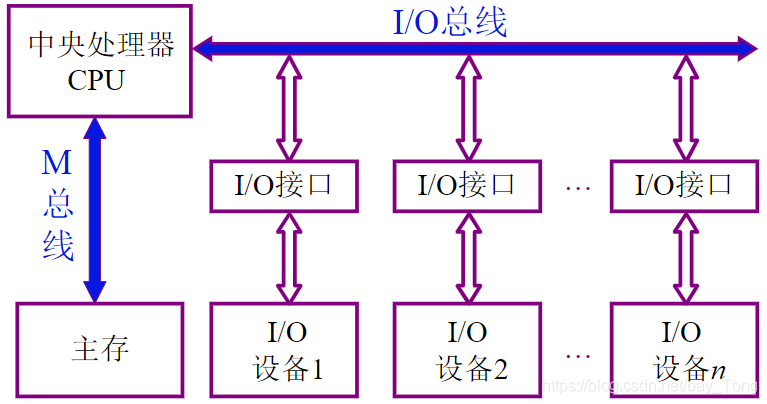

单总线结构:

- 使用一条单一的系统总线来连接 CPU、主存和I/O设备

- 访问存储器和访问外设指令相同,由地址区分

- 总线简单,使用灵活,易于扩展

- 问题:总线成为系统的瓶颈,要求总线上的逻辑部件须高速运行,所有设备分时操作,设备需要使用总线时能迅速获得总线控制权,不再使用 总线时能迅速放弃总线控制权,仅适用于慢速计算机系统

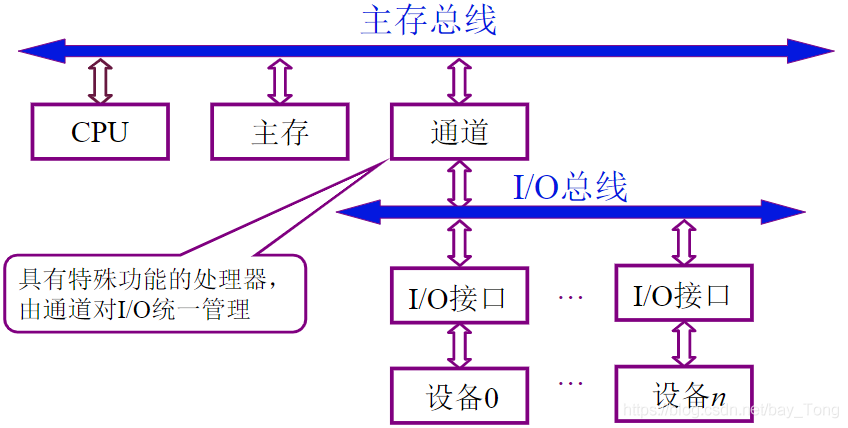

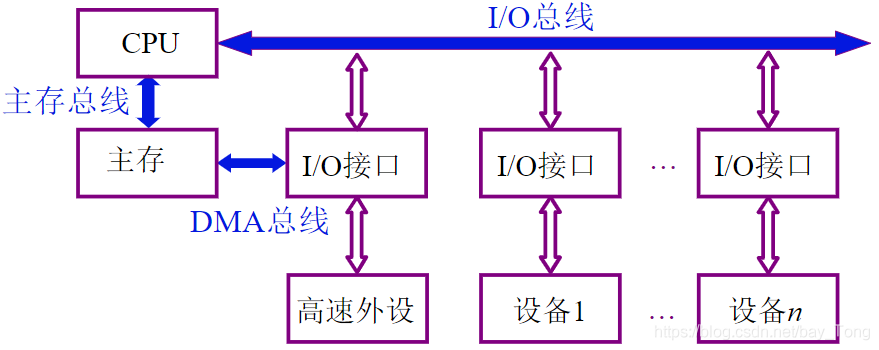

双总线结构:

- 面向CPU的双总线结构

- 以存储器为中心的双总线结构

- 主存-I/O双总线结构:通过通道(具有特殊功能的处理器)对I/O统一管理

- 主存总线、I/O总线、DMA总线(个别教材也称三总线结构)

○ 保持了单总线系统简单易扩充的优点

○ CPU与存储器可高速交换信息,减轻了系统总线的负担

○ 同时主存可通过系统总线与外设之间实现DMA操作,不必经过CPU

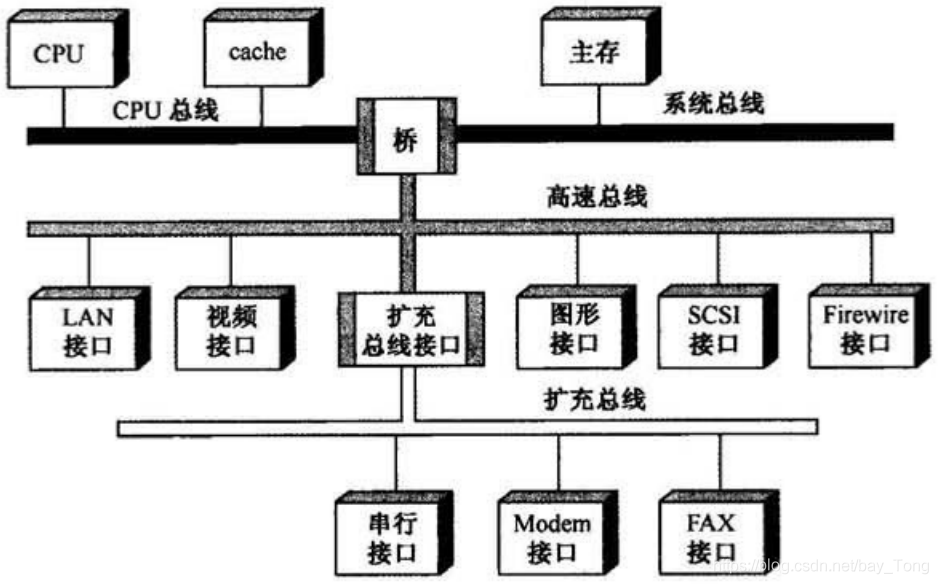

多总线结构:

- CPU与cache之间采用高速的CPU总线,主存连接在系统总线上,另外设有桥、扩展总线接口

- 大多数计算机采用了分层次的多总线结构。此结构下速度差异较大的设备模块使用不同速度的总线,速度相近的设备模块使用同类总线

- 总线桥:是不同速率总线之间的连接器件,起信号速度缓冲、电平转换、控制协议转换等作用

单机总线与多级总线的区分标志:

- 并不是单纯看总线的条数,单机总线结构中不一定只有一条总线

- 指令中若有单独的I/O总线,则为双级总线或多级总线,否则为单机总线

总线结构对计算机系统性能的影响:

- 对最大存储容量的影响:单总线结构有影响,双总线和多总线结构没有

- 对指令系统的影响:双总线和多总线结构需要增加I/O指令

- 吞吐量(单位时间内成功传送的数据量):单总线结构的吞吐量小,多总线结构的吞吐量大,双总线结构的吞吐量居中,即总线数目越多,吞吐能力越大

总线接口(I/O接口)概述

概念: 也称I/O接口,即I/O设备控制器,具体指CPU与主存、外围设备之间通过总线进行连接的逻辑部件

作用:

- 外设种类繁多,存储器种类单一,必须经过接口电路连接到总线上

- 外设速度较慢,存储器的速度较快,必须经过接口电路进行数据的缓冲和锁存

- 外设的信号多种多样,必须经过接口电路转换成处理器可以识别的信号

- I/O接口的作用相当于与一个转换器,它可以保证外围设备用计算机要求的形式发送或接收信息

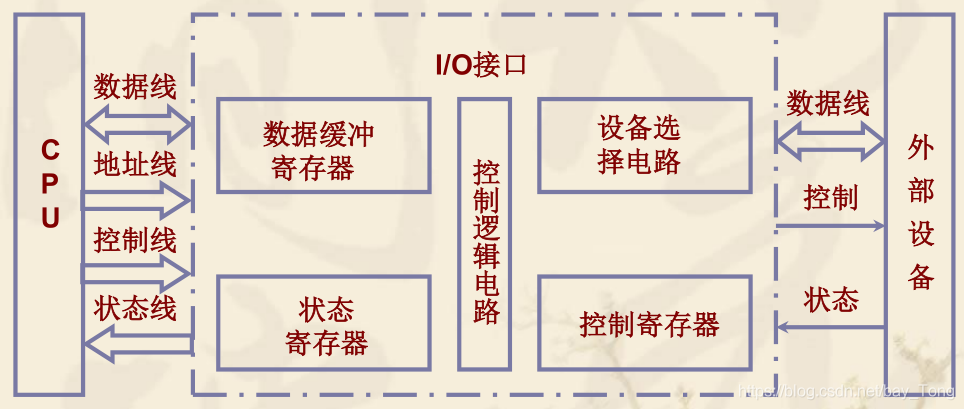

基本结构:

- 端口:CPU能够直接访问的I/O接口内部的寄存器称为端口

- 端口号:每一个端口的访问地址

I/O接口的功能:

- 控制功能:能接收来自CPU的控制命令来控制外围设备的动作,如启动/关闭设备

- 缓冲功能:在外围设备和计算机其他部件之间作为一个缓冲器,补偿速度差异

- 状态功能:监视外围设备的工作状态并保存状态信息,供CPU查询

- 转化功能:完成任何要求的数据转换,如串-并变换(装配)和并-串(拆卸)变换

- 程序中断功能:当外围设备请求CPU某种动作时,接口模块能够向CPU发出中断请求信号

- 复位功能:接口能接收复位信号,使接口本身和外设重启

- 错误检查功能:对输入输出的数据进行校验,检查传送中的错误

I/O接口及相关内容详细见本栏文章《输入输出(I/O)系统总结——基本知识要点汇总》

总线通信

相关概念:

- 波特率:每秒传送的二进制数的位数

- 计算机数据的处理方式为并行处理,则串行传送需要数据在发送部件进行并-串变换,称为拆卸;接收部件进行串-并变换,称为装配

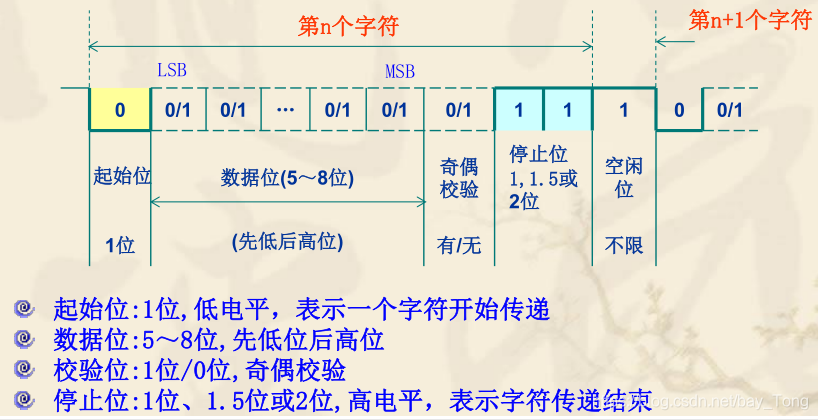

信息传递方式:

- 串行通信:一条信息的各数据位在一个信道上按照固定的时间长度被逐位按顺序传送,采用脉冲方式传送信息,一次新的传送一定是以一个电平的跳变开始,因此通常采用异步通信

○ 速度慢,信息率低,但成本低,适合远距离传输

○ 通讯中数据以单个字符为单位,每两个字符间的传输间隔是任意的

- 并行通信:把一个字符的各数据位用几条传输线同时进行传输,通常采用应答式的联络信号协调双方的数据传送操作(半同步通信)

○ 实际的传输速度快,信息率高

○ 远距离传输电缆开销大,线与线之间容易产生干扰,信号易变形 - 串并传送:一次传送多个二进制位,但是同时传送的二进制位数小于数据宽度,按照串行的方式多次传输将整个数据宽度传送完

总线控制

- 总线事务:从请求总线到完成总线使用的操作序列称为总线事务,它是在一个总线周期中发生的一系列活动;典型的总线事务包括:请求操作、裁决操作、地址传输、数据传输、总线释放

- 总线的判优控制:总线在同一时刻只能由一对设备进行控制使用

- 总线的通信控制:这对设备占用总线后如何完成通信过程,保证通信过程的正确性

总线判优控制

根据是否能提出总线请求,将总线上的设备分为

- 主设备(模块):对三总线有控制权,可以提出总线占用申请,申请占用成功后可以控制这段通信过程

- 从设备(模块):本身不能对总线进行控制,也不能提出总线占用请求,只能响应从主设备发来的总线命令

- 有些设备既可以作为主设备又可以作为从设备,有些总线可以有多个主设备,有些总线只有唯一的主设备

一般情况下CPU为主模块,但有两种情况需要解决总线的控制权问题(总线仲裁):

- 多处理系统中,每一个CPU均能提出占用总线的请求

- 某些I/O设备也能提出总线请求

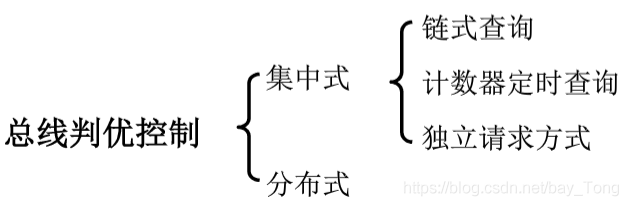

总线仲裁部件解决多个主设备同时竞争总线控制权的问题,一般采用优先级或公平策略进行仲裁。按照总线仲裁电路的位置不同,仲裁方式可分为集中式仲裁和分布式仲裁两类

集中式仲裁

集中式仲裁:总线控制逻辑基本上集中于一个设备中,将所有的总线请求集中起来,利用一个特定的裁决算法进行裁决

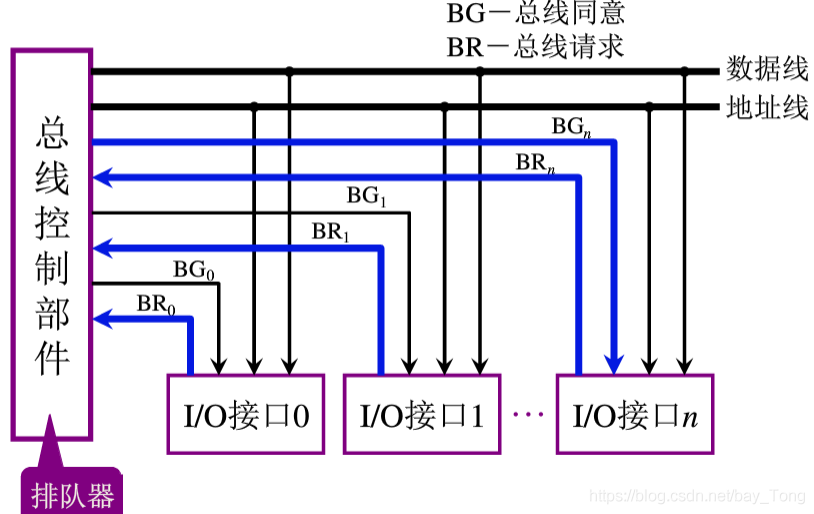

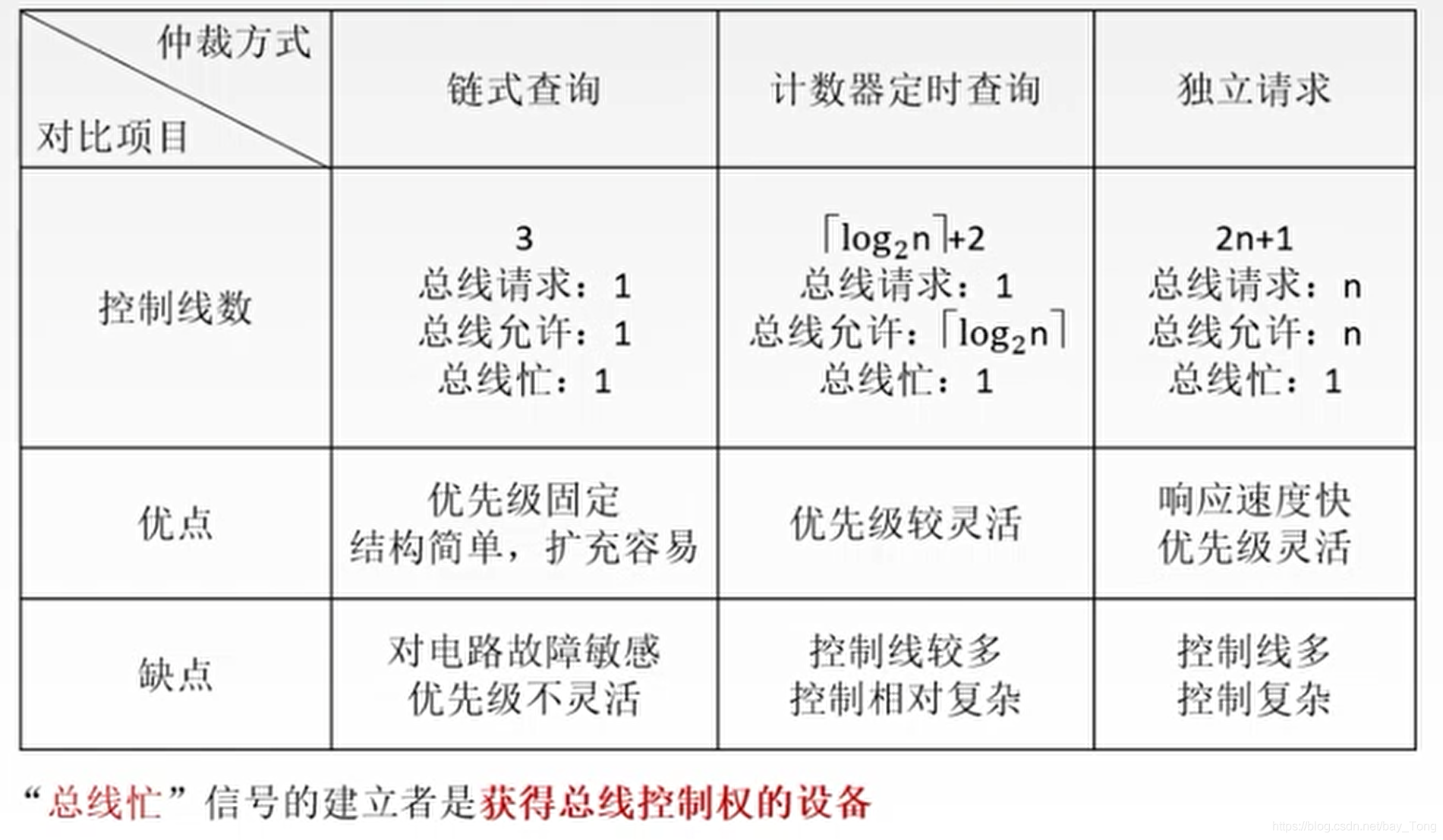

链式查询方式:

- 总线同意信号BG串行地从一个I/O接口送到下一个I/O接口,若BG到达的接口有总线请求,则BG信号就不再往下传,意味着该接口获得了总线使用权,并建立总先忙BS信号,表示它占用了总线

- BG信号需要线性链式查询,速度较慢

- 优先级受限于连接的排序

- 对链路故障敏感(尤其针对BG)

- 结构简单,增删设备容易,优先级算法简单,进行可靠性设计较容易实现(如将BG设两条线,避免其中一条线出现故障导致无法进行判优)

- 一般用于微型计算机或简单的嵌入式系统

计数器定时查询方式:

- 与链式查询相比,多了一组设备地址线,少了一根总线同意线BG。总线控制部件接到由BR送来的总线请求信号后,在总线未被使用(BS=0)的情况下,总线控制部件中的计数器开始计数,并通过设备地址线向各设备发出一组地址信号。当某个请求占用总线的设备地址与计数值一致时,即获得总线使用权,此时终止计数查询

- 设备地址:通过计数器给出,用来查找某一个设备是否发出请求

- 优先级的确定灵活,对电路的故障没有链式敏感

- 控制相比链式查询更复杂

- 增加了控制线数,若设备有n个,则需要[log2n]+2条控制线(n个设备的设备地址需要log2n条地址线,再共用BS和BR两条线)

独立请求方式(集中式并行总线仲裁):

- 内部排队器集中进行排队,优先级的确定灵活

- 使用的线数多,若设备有n个则需要2n+1条控制线(每个设备一条BR线一条BG线,最后共用一条BS线),总线的控制逻辑更加复杂

三种集中式仲裁方式对比:

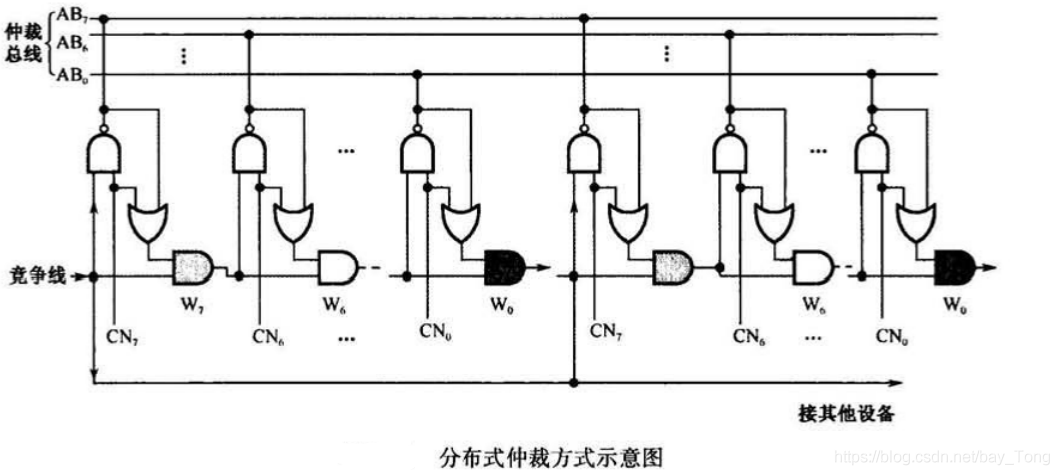

分布式仲裁

分布式仲裁不需要中央仲裁器(总线控制部件),每个潜在的主方功能模块都有自己的仲裁号和仲裁器。当它们有总线请求时,把它们唯一的仲裁号发送到共享的仲裁总线上,每个仲裁器将仲裁总线上得到的号与自己的号进行比较。如果仲裁总线上的号大,则它的总线请求不予响应,并撤消它的仲裁号。最后,获胜者的仲裁号保留在仲裁总线上。显然,分布式仲裁是以优先级仲裁策略为基础

常用仲裁(优先级确定)策略

- 固定优先级总线仲裁

- 轮叫式总线仲裁

- LRG总线仲裁(类比存储器页面替换)

- 混合式总线仲裁

总线通信控制(总线的定时)

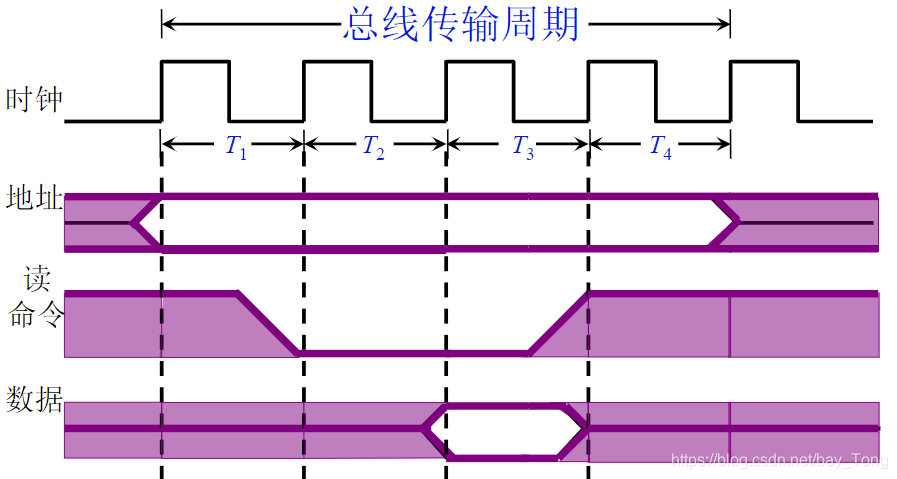

总线传输周期:完成一次总线上信息传送操作的时间

- 申请分配阶段:主模块申请,总线仲裁决定

- 寻址阶段:主模块向从模块给出地址和命令

- 数据传输阶段:主模块和从模块交换数据

- 主模块撤销有关信息,让出总线使用权

目的:解决通信双方协调配合的问题。为了约定主从双方的操作,必须制定定时协议(定时:事件出现在总线上的时序关系)

总线通信的四种方式:

- 同步通信:统一时序控制数据传送

- 异步通信:采用应答方式,没有公共时钟标准

- 半同步通信:同步异步相结合,主要解决不同速度的设备间通信的问题

- 分离式通信:充分挖掘系统总线每个瞬间的潜力,让系统总线发挥最大潜能

同步定时方式

同步式数据输入

同步式数据输出

事件出现在总线上的时刻由总线的时钟信号来确定。由于采用了公共时钟,每个功能模块什么时候发送或接收信息都由统一时钟规定,因此,同步定时具有较高的传输频率

- 定宽、定距的时钟

- 固定时间点给出固定的操作

- 在设备速度不一致时按最坏情况确定,传输线不能太长(时钟相移)

- 时序关系简单,实现容易,传送速度快,具有较高的传输速率

- 主从设备属于强制性同步,不能及时进行数据通信的有效性检验,可靠性较差

- 一般用于总线长度短、各模块存取时间较一致的情况下

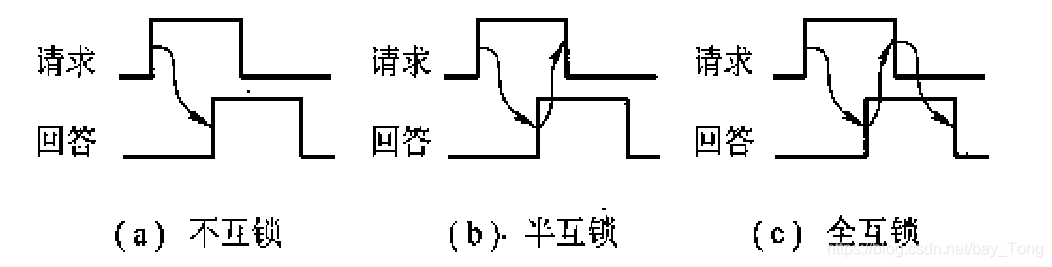

异步定时方式

在异步定时协议中,后一事件出现在总线上的时刻取决于前一事件的出现,即建立在应答式或互锁机制基础上。在这种系统中,不需要统一的公共时钟信号。总线周期的长度是可变的

全互锁:

- 主设备占用总线后,向数据总线发送数据,同时使控制总线的“数据准备好”信号有效,该信号作用是告诉从设备数据已经发到总线上

- 从设备检测到总线的“数据准备好”信号有效,就认为数据总线上的数据是有效并开始接收数据,并发出“数据已接收”信号,该信号作用是告诉主设备数据已经被接收

- 主设备检测到“数据已接收”信号有效,就认为从设备已经接收了数据总线的数据,就使“数据准备好信号”无效

- 从设备检测到“数据准备好”信号无效,就使“数据已接收”信号无效

不互锁:

- 主设备发出数据后,使“数据准备好”信号有效,不等待“数据已接收”信号,而是经过特定的时间后,使“数据准备好”信号无效

- 从设备检测到“数据准备好”信号有效,就从总线接收数据,并使“数据已接收”信号有效。经过特定的时间后,使“数据已接收”信号无效

半互锁:

- 主设备发出数据后,使“数据准备好”信号有效。等待从设备的“数据已接收”信号

- 从设备检测到“数据准备好”信号有效,就从总线接收数据,并使“数据已接收”信号有效。从设备不再等待“数据准备好”信号无效,而是经过特定的时间后,使“数据已接收”信号无效

- 主设备检测到“数据已接收”信号有效,就使“数据准备好”信号无效

通过请求和应答的握手信号进行通信;适用于传输周期不同的设备,对通讯线的长度没有严格的要求;速度相对较慢

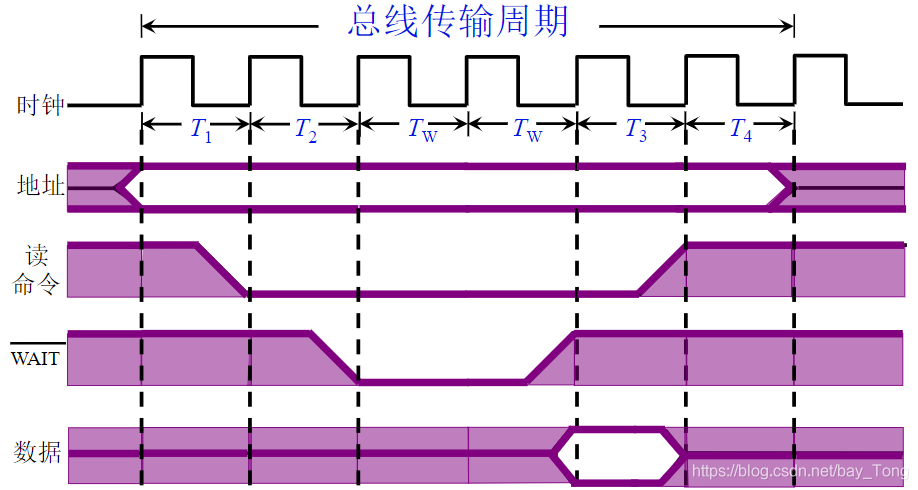

半同步定时方式

- 同步:发送方用系统时钟上升沿发信号,接收方用系统时钟下降沿判断、识别

- 异步:允许不同速的模块和谐工作,增加一条WAIT响应信号(从设备给出)

简单来说,总线上各操作之间的时间间隔可以变化,但仅允许为公共时钟周期的整数倍。信号的出现、采样和结束仍以公共时钟为基准

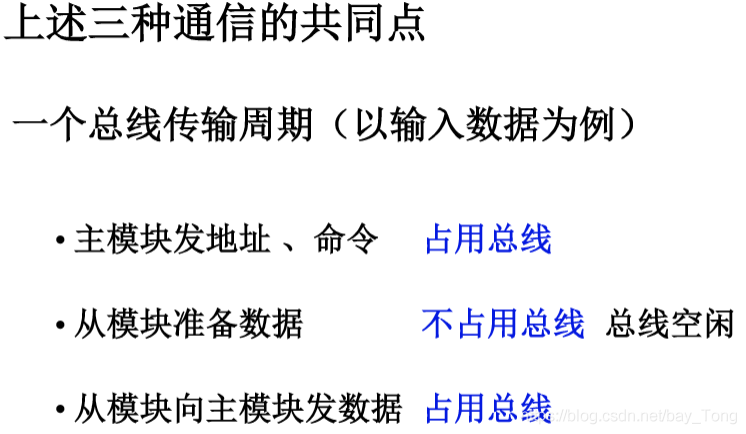

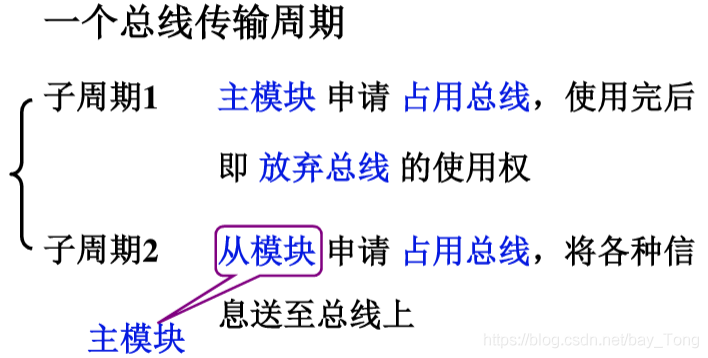

分离式通信

充分利用总线,解决以上三种通信模块准备数据时总线的空闲

- 各模块有权申请占用总线

- 采用同步方式通信,不等对方回答

- 各模块准备数据时不占用总线

- 总线被占用时无空闲

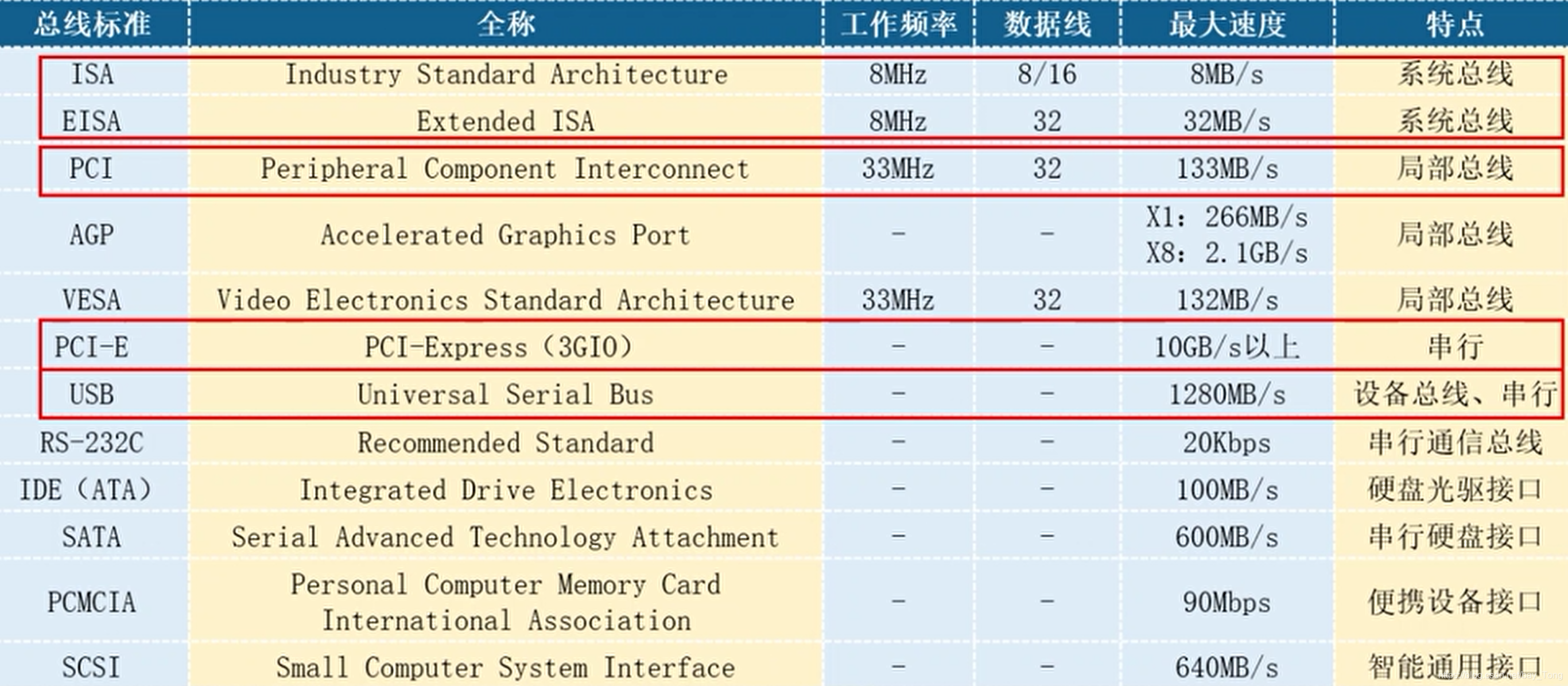

总线标准(待更新……)

持续更新中……

我是桐小白,一个摸爬滚打的计算机小白