文章目录

前言

根据计算机组成原理课程内容,设计对应的基础实验教学方案。其中分别为数据表示实验,运算器实验,存储器实验,以及 MIPS CPU 实验。本文将改进以往的实践教学方案,将虚拟仿真实验引入教学课堂。

实验资料

平台:Educoder

实验软件:Logisim 2.15.0.2

以下是本篇文章正文内容,下面案例可供参考

一、计算机数据表示实验

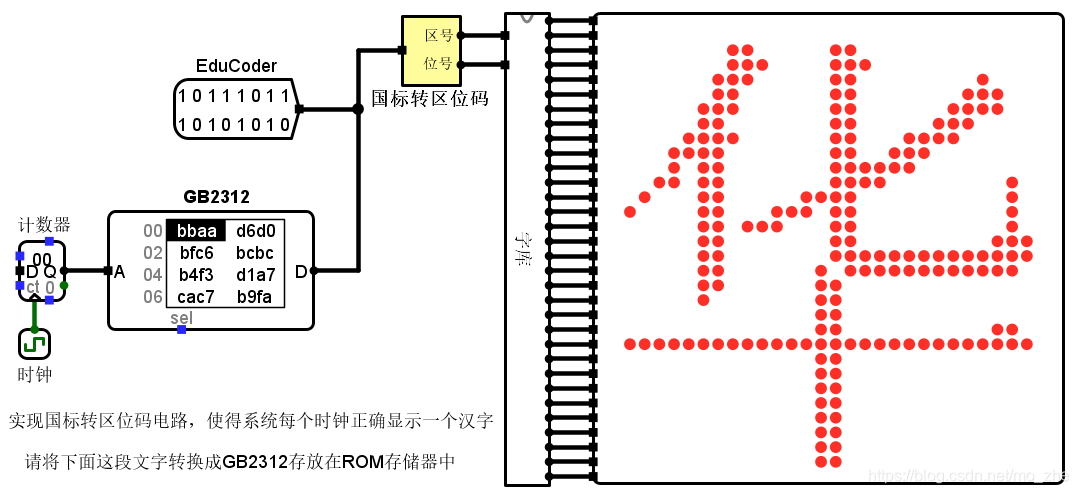

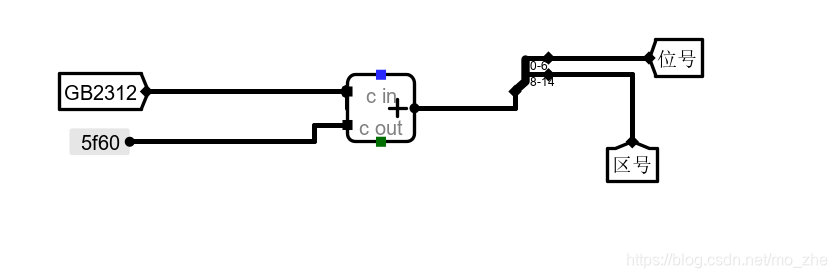

第1关:汉字国标码转区位码实验

在 logisim 中打开实验资料包中的 data.circ 文件,在对应电路中完成国标码转区位码的子电路设计。其中输入引脚为16位的 GB2312 双字节国标码;输出为区号和位号(区号位号均从1开始计数),图1.6为转换子电路引脚定义,请在电路中复制对应隧道标签信号使用,注意不要增改引脚,不要修改子电路封装,以免影响子电路在其它电路模块中的正常调用。

测试结果:

国标转区位码电路

第2关:汉字机内码获取实验

完成国标码到区位码的转换电路后,可以在汉字显示电路中进行测试,尝试在下图所示电路中的 ROM 存储器中存入下面给出的指定句子,注意这里不允许使用逐字查码表的方式获得编码,应掌握批量转换的方法和原理。

实例文本:

12345ABCDEFGabcdefg轻轻的我走了,正如我轻轻的来;我轻轻的招手,作别西天的云彩。那河畔的金柳,是夕阳中的新娘;波光里的艳影,在我的心头荡漾。

转GB2312填入ROM存储器

a3b1 a3b2 a3b3 a3b4 a3b5 a3c1 a3c2 a3c3

a3c4 a3c5 a3c6 a3c7 a3e1 a3e2 a3e3 a3e4

a3e5 a3e6 a3e7 c7e1 c7e1 b5c4 ced2 d7df

c1cb a3ac d5fd c8e7 ced2 c7e1 c7e1 b5c4

c0b4 a3bb ced2 c7e1 c7e1 b5c4 d5d0 cad6

a3ac d7f7 b1f0 cef7 ccec b5c4 d4c6 b2ca

a1a3 c4c7 bad3 c5cf b5c4 bdf0 c1f8 a3ac

cac7 cfa6 d1f4 d6d0 b5c4 d0c2 c4ef a3bb

b2a8 b9e2 c0ef b5c4 d1de d3b0 a3ac d4da

ced2 b5c4 d0c4 cdb7 b5b4 d1fa a1a3 0000

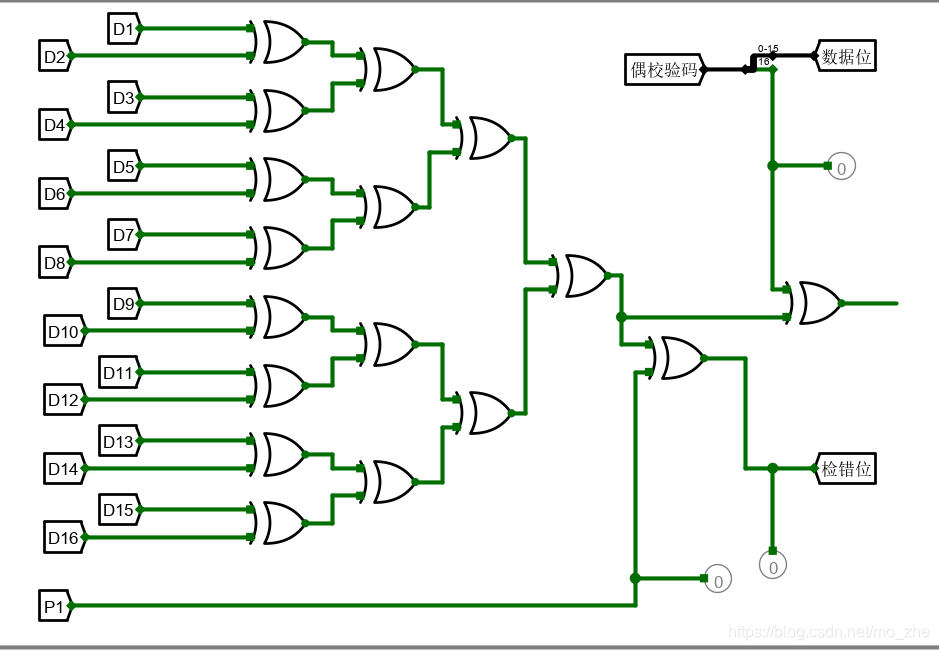

第3关:偶校验编码设计

在 logisim 中打开实验资料包中的 data.circ 文件,在对应电路中完成偶校验编码电路。实验电路输入输出引脚如图所示。输入:16位原始数据;输出:17位校验码(16位数据位+1位校验位),其中校验位存放在最高位,注意输入16位原始数据的每一位都已经通过分线器利用隧道标签引出,可以直接复制到绘图区使用。

第4关:偶校验解码电路设计

在logisim中打开实验资料包中的 data.circ 文件,在对应电路中完成偶校验检错电路。输入:17位校验码,校验位存放在最高位;输出:16位原始数据,1位检错位;实验电路输入输出引脚定义如图所示,注意17位校验码的每一位都通过分线器利用隧道标签引出,方便实验时使用。

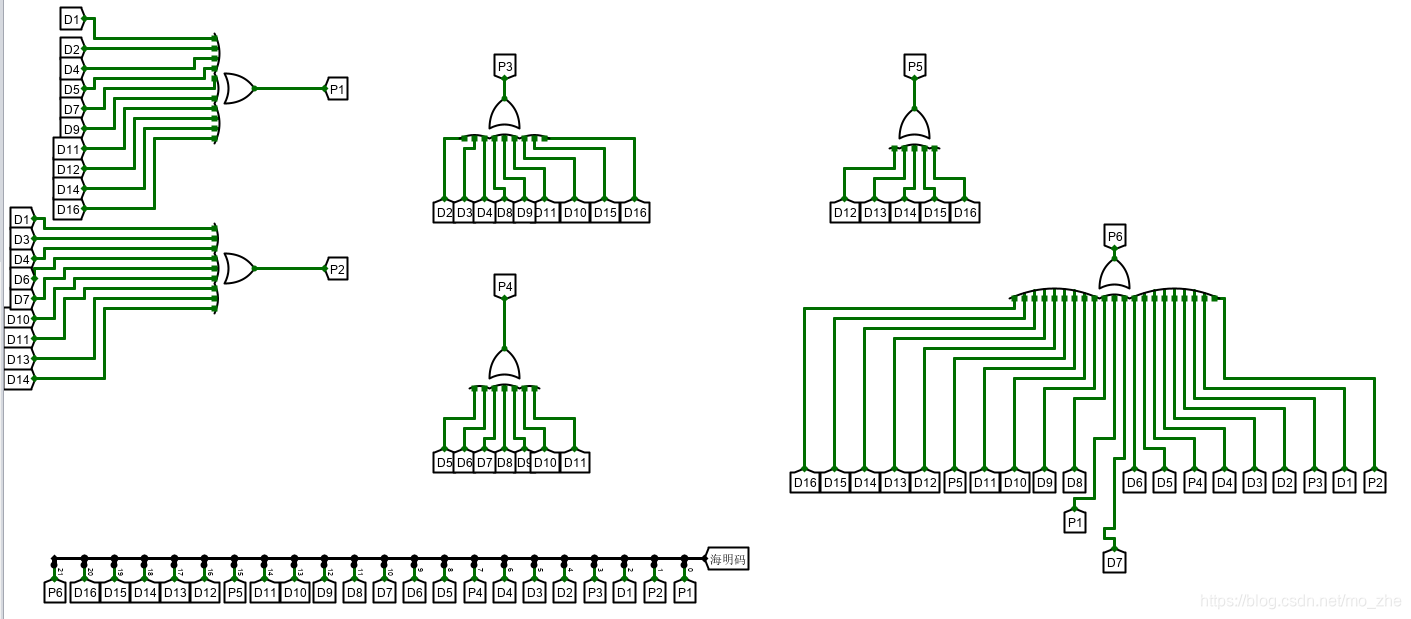

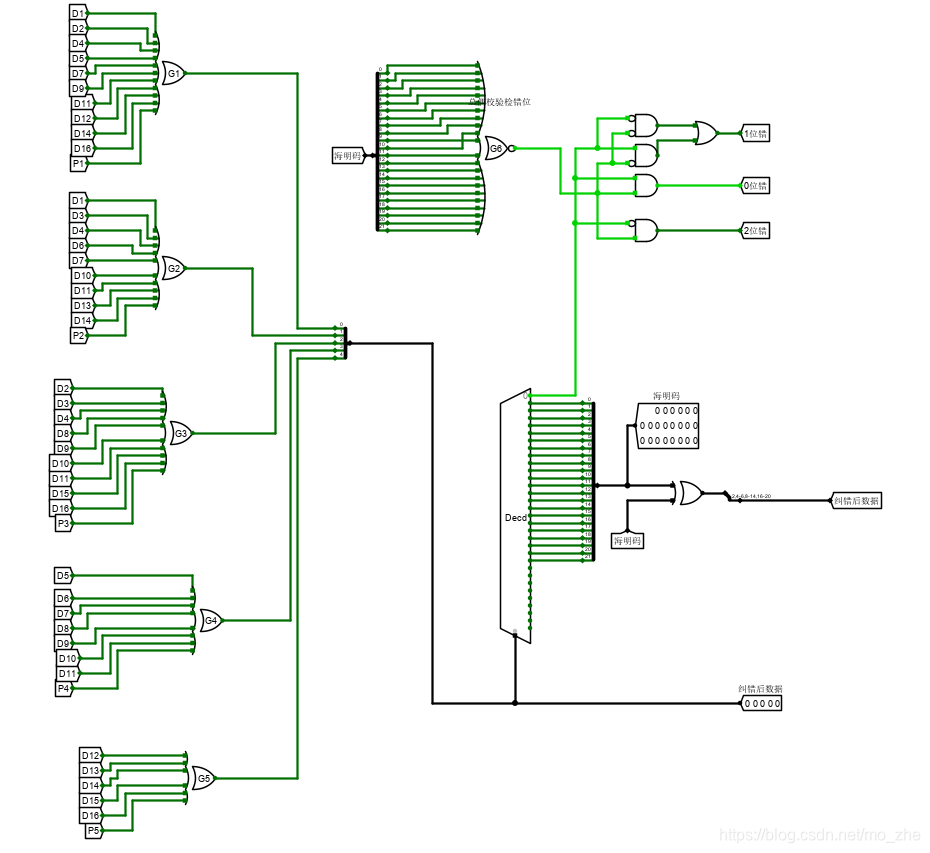

第5关:16位海明编码电路设计

在 logisim 中打开实验资料包中的 data.circ 文件,在对应电路中完成海明校验编码电路。输入输出引脚定义如图所示。输入:16位原始数据;输出:22位校验码(16位数据位+5位校验位+1位总校验位),注意输入16位原始数据的每一位都已经通过分线器利用隧道标签引出,可以直接复制到绘图区使用。

第6关:16位海明解码电路设计

在 Logisim 中打开实验资料包中的 data.circ 文件,在对应电路中完成海明校验解码电路。输入输出引脚定义如图,输入:22位校验码;输出:16位原始数据,1位检错位;2位检错位;无错误状态位。注意输入16位原始数据的每一位都已经通过分线器利用隧道标签引出,可以直接复制到绘图区使用。

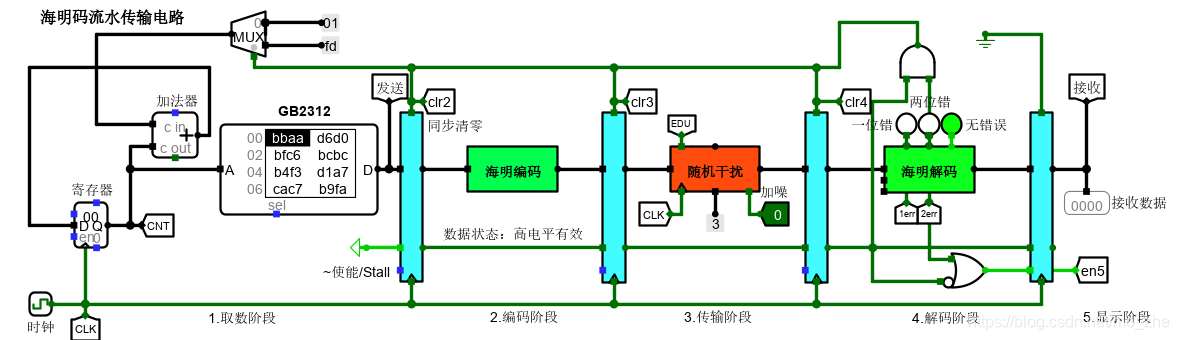

第7关:海明编码流水传输实验

图中将海明编码传输过程分成了5个阶段(取数,编码,传输,解码,显示)类似 CPU 指令流水线的处理过程。中间蓝色长条为流水接口部件(内部实际是若干锁存器/寄存器,用于锁存数据和控制信号),流水接口部件提供同步清零控制信号,试启用时钟自动仿真运行该电路(CTRL+T),观察接收方接受到的信息,当发生两位错时,将会发生错误。

尝试使用最少的器件简单修改该电路,使得解码阶段出现两位错时,系统能自动重传出错的编码(类似指令流水线中的分支跳转),从而使得该电路能正确传输所有数据。

解题思路:当出现两位错时,首先要将编码阶段和传输阶段的数据清空,这部分数据会导致接收端数据顺序不一致,同时要将已经进入显示阶段的数据锁定,并将取数阶段的地址回滚到正确的位置。

二、运算器设计

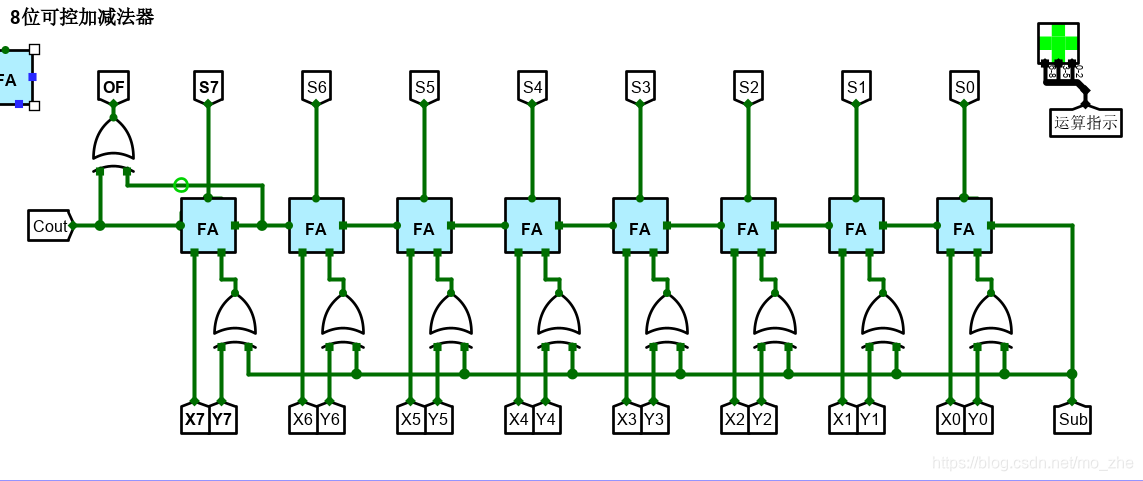

第1关:8位可控加减法电路设计

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。

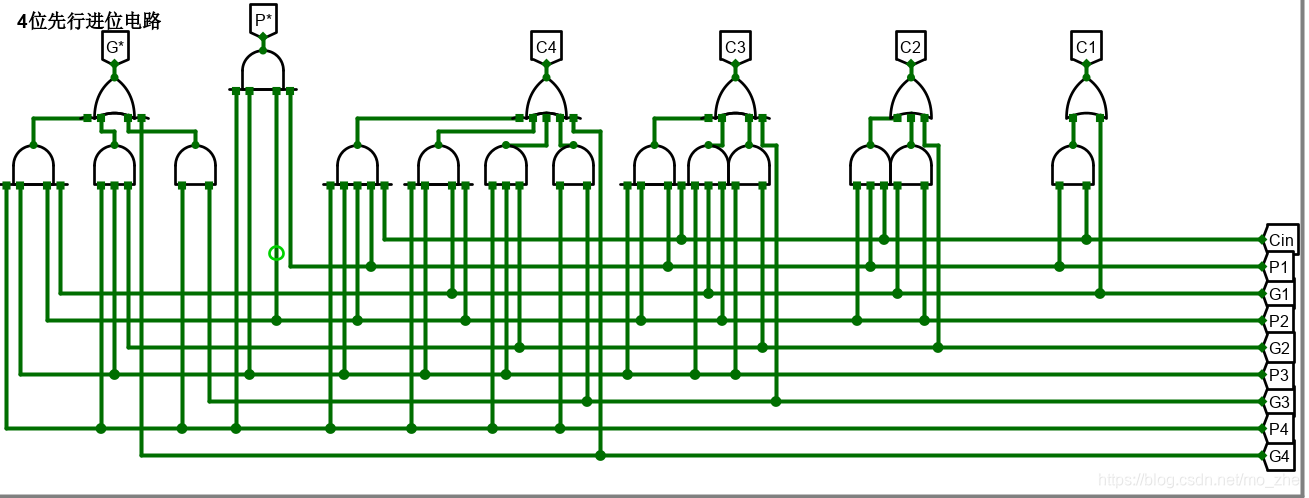

第2关:CLA182四位先行进位电路设计

在 Logisim 中打开 alu.circ 文件,按照图中定义的输入输出引脚,在对应子电路中实现可级联的4位先行进位电路。其中 Gi,Pi 为进位生成函数和传递函数,Cin 为进位输入,C1~C4 为进位输出,G,P 为成组进位生成函数和成组进位传递函数。

第3关:4位快速加法器设计

利用前一步设计好的四位先行进位电路构造四位快速加法器,其引脚定义如图所示,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

第4关:16位快速加法器设计

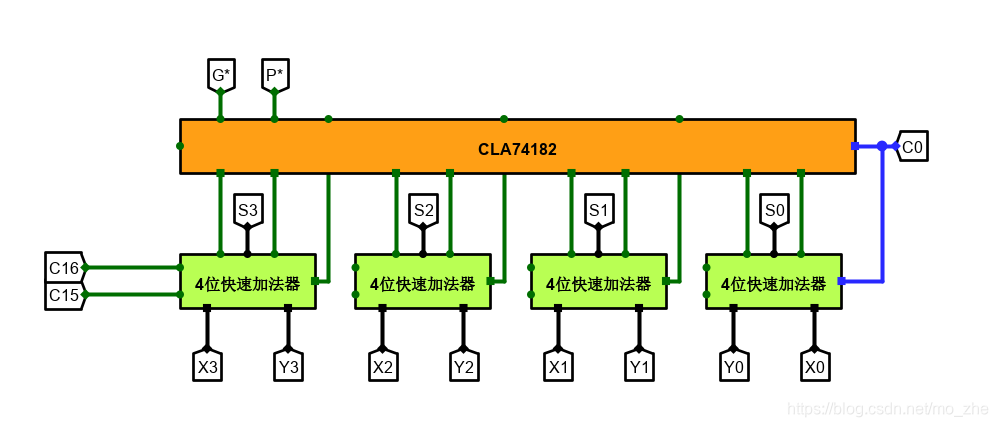

在 Logisim 中打开 alu.circ 文件,在对应的子电路中利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器,并验证其功能是否正常,快速加法器引脚定义如图所示。其中 X,Y 为16位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为16位成组进位生成函数和成组进位传递函数。

第6关:5位无符号阵列乘法器设计

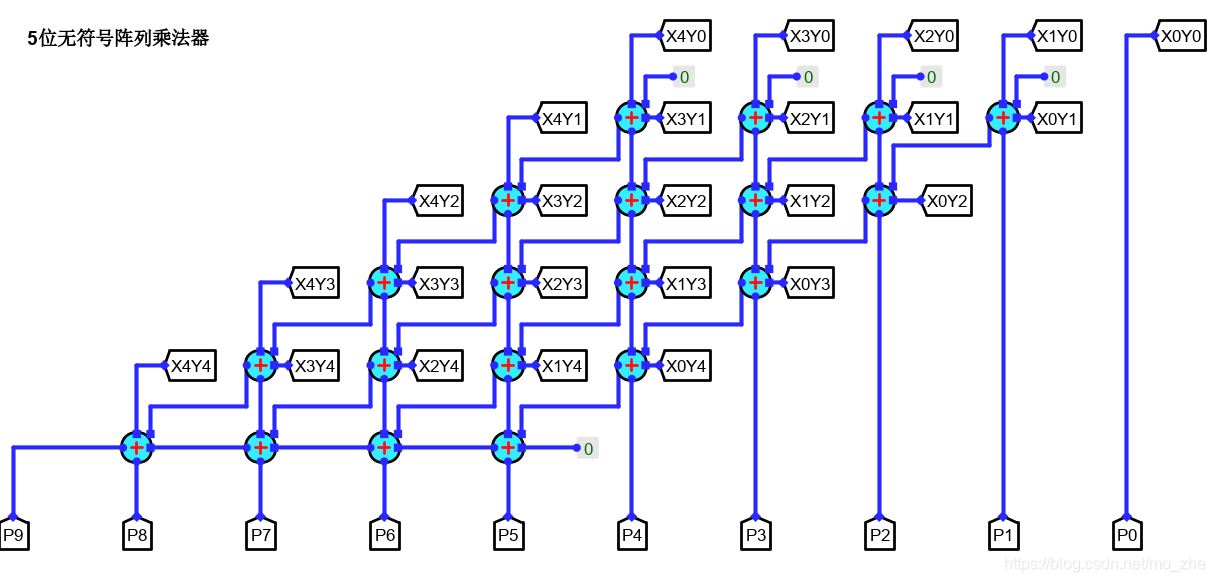

在 Logisim 中打开 alu.circ 文件,在5位阵列乘法器中实现斜向进位的阵列乘法器,该电路引脚定义如图所示,其中 X,Y 为5位被乘数和乘数,P 为乘积输出,阵列乘法所需的25按位与的乘积项已经通过辅助电路生成,如图2.21所示,所有乘积项均通过隧道标签给出,用户只需要在已给出的电路框架中进行简单连线即可完成5位阵列乘法器。

三、存储系统设计

第1关:汉字字库存储芯片扩展实验

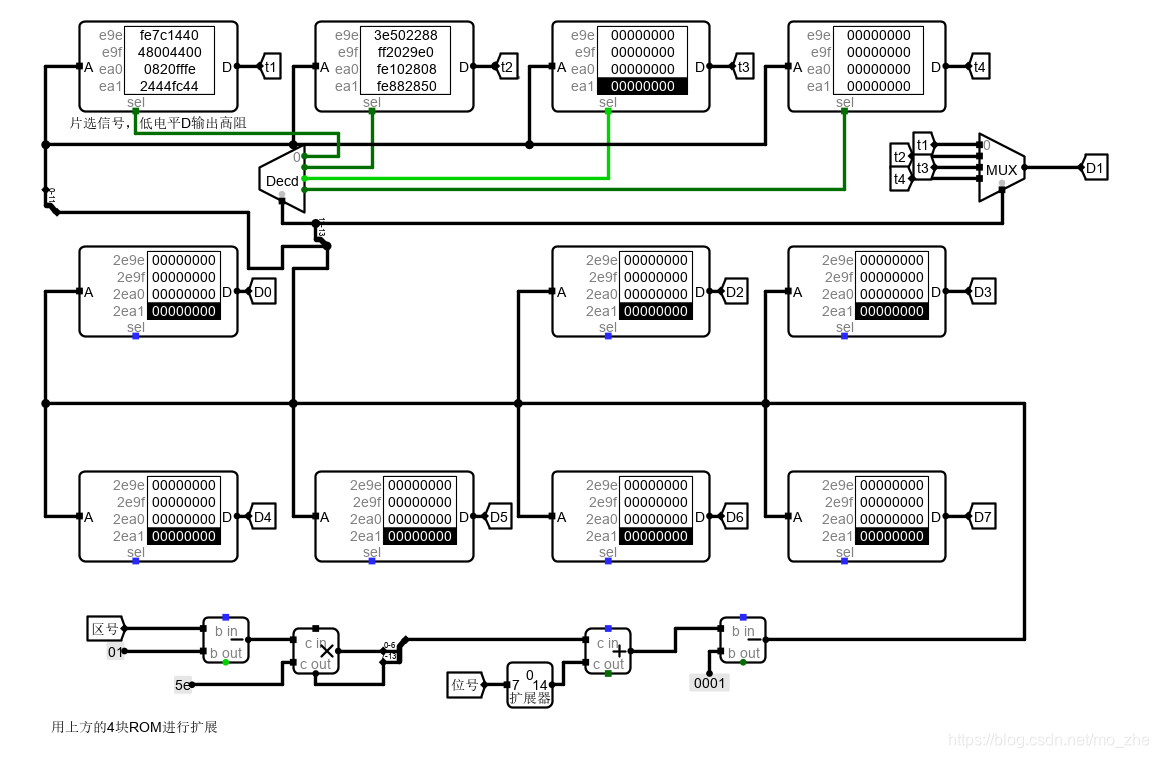

现有如下 ROM 组件,4片4K32位 ROM ,7片 16K32位 ROM,请在 Logisim 平台构建 GB2312 汉字编码的16K16点阵汉字字库,电路输入为汉字区号和位号,电路输出为8×32位(16K16=256 位点阵信息),待完成的字库电路输入输出引脚见后图,具体参见工程文件中的 storage.circ 文件,图中左侧是输入引脚,分别对应汉字区位码的区号和位号,中间区域为8个32位的输出引脚,可一次性提供一个汉字的256位点阵显示信息,右侧是实际显示区域,用于观测汉字显示是否正常。待完成字库子电路封装已经完成,请勿修改以免影响后续自动测试功能。

第2关:MIPS寄存器文件设计

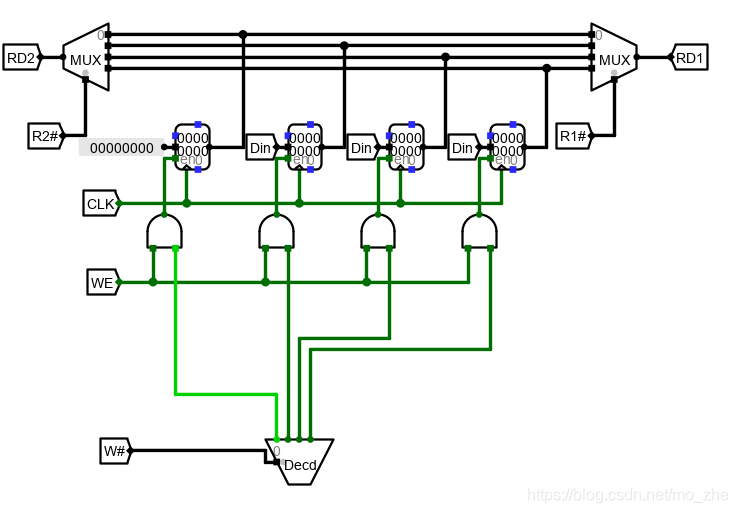

利用 Logisim 平台构建一个简化的 MIPS 寄存器文件,内部包含4个32位寄存器,其具体引脚与功能描述如下表。

总结

感谢支持,需要源工程文件的自取。

链接:冲冲冲~

提取码:po8c

复制这段内容后打开百度网盘手机App,操作更方便哦