1.概念

①中央处理部件(Central Processing Unit,CPU)可以说是计算机的“大脑”,其功能是通过从主存储器中逐条进行 取指令、分析指令和执行指令的过程来执行计算机程序。

②程序计数器(Program Counter,PC)它用于指向下一条将要被取出用于执行的指令。

③指令寄存器(Instruction Register,IR)其中存放着当前正执行的执行。

④算术逻辑部件(Arithmetic Logic Unit,ALU)

⑤数据通路:一般包括 寄存器、ALU和连接它们的内部总线。、

2.CPU组

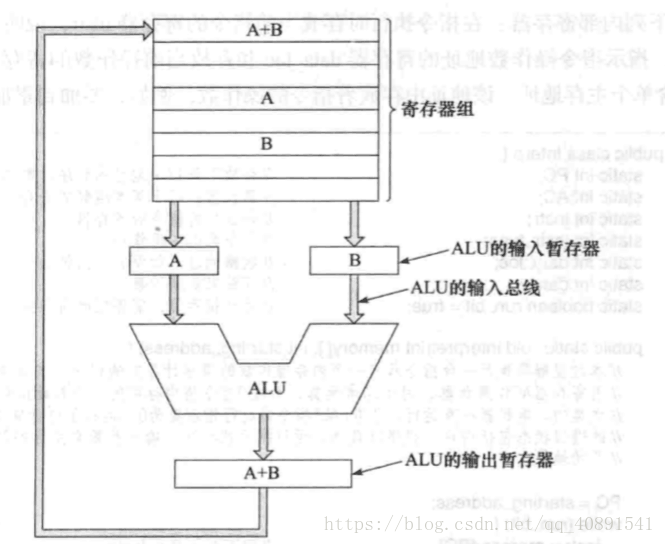

上图是一个CPU的数据通路图

①如上图,ALU有两个输入暂存器,一个输出暂存器。暂存器的功能是在ALU进行计算时维持ALU的输入数据。

3.CPU指令

①大多数CPu中的指令可以归为:寄存器-主存指令和 寄存器-寄存器指令。前者用于在寄存器和主存之间交换数据,后者用于在寄存器与寄存器之间操作,比如:从两个寄存器中取得两个操作数,送入ALu的输入暂存器中。

②ALU将两个操作数进行运算并将结果协会的过程成为数据通路周期,这是大多数CPU的核心。

③执行指令的过程大致可以分为以下几个步骤:

1)从主存中去下一条指令到指令寄存器中。

2)将程序计数器指向后面一条指令。

3)判断刚刚取得的指令的类型。

4)若该指令用到某主存单元,则对该主存单元进行寻址。

5)必要时,从主存中取一个字,则对该主存单元进行寻址。

6)执行指令。

7)返回第1步准备执行下一条指令。

4.RISC和CISC

① RISC:是 精简指令计算机(Reduced Instruction Set Computer)

②CISC:是 复杂指令计算机(Complex Instruction Set Computer)

5.现代计算机设计原则

①所有指令由硬件直接执行

②最大限度提高指令启动速度

③指令应容易译码

④只允许读写主存指令访问主存

⑤提供足够的寄存器

6.指令级并行

① 指令级并行指的是在指令之间应用并行。

②指令流水:

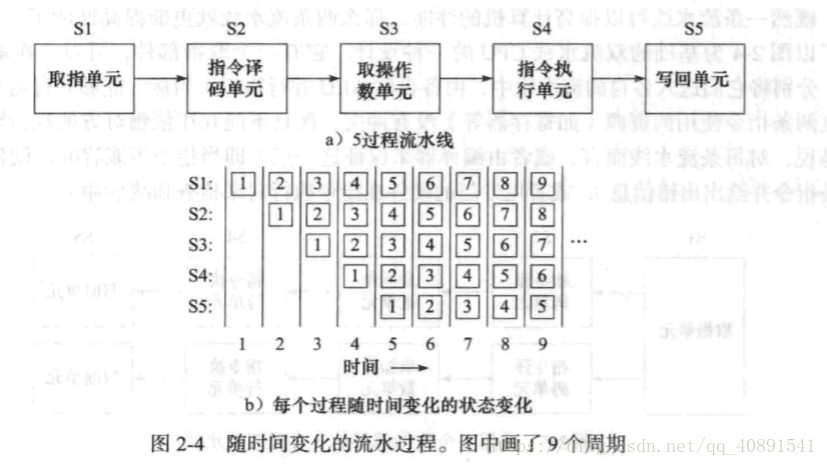

图中的例子里,将指令执行划为了5个部分(现实中通常为12个或者更多),每个部分由精心设计的硬件分别执行,让他们并行运行。

第1个时钟周期:S1工作已第1条指令。

第2个时钟周期:S2对第1条指令进行译码,S1取第2个指令。

第3个时钟周期:S3取第1个指令的操作数,S2对第2个指令进行译码,S1取第3条指令。

.................................................

以此类推。

③指令流水可以用 指令时延 或者 处理器处理器带宽(MIPS数)来衡量。

④超标量体系结构:

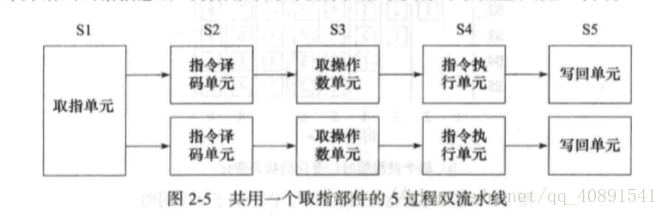

如果一条流水线不够用,则用两条流水线来加速,使得慢的部件能够跟上快的部件的节奏。

如图的方案,其取指部件可以一次取两条指令,分别送入各自的流水线,并由其各自的ALu并行执行。

⑤无论是几条流水线,大多都用在RISC机上。

7.处理器级的并行

①指令级并行固然可以提高效率,可是传输的速度是有物理极限的,并且,芯片越多,其产生的热量也会越多,散热就很成问题。

②对于那些高度规则的数据结构进行相同的数据运算,加速它们相对容易。我们主要有两种方式来可快速并高效的执行这类高度规则的程序:SIMD处理器和向量处理器。前者被看成是并行计算机,后者被当成单处理器的扩展。

③单指令流多数据流处理器(Single Instruction-stream Multiple Data-stream,SIMD):这种处理器由许多在不同数据集合上执行同样的指令序列的王权相同的处理器组成。

现代的GPU(图形处理器)严重依赖SIMD处理器使用较少的晶体管来提供巨大的处理能力。

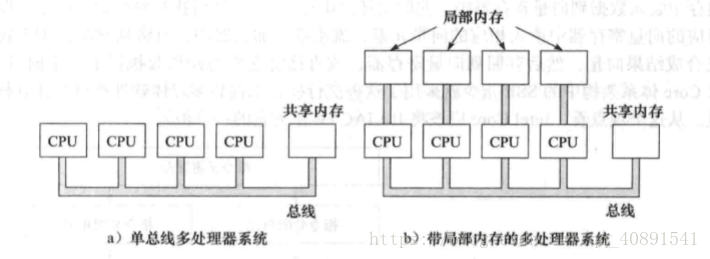

④多处理器系统:除了增加处理器的性能和数据的规整程度外,还可以增加多处理器

⑤ 多计算机系统:才用多个计算机互联组成多计算机系统。