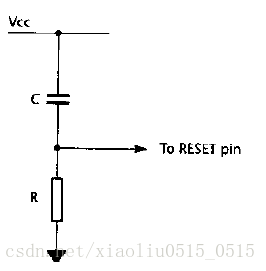

一、阻容复位电路

8051系列大部分是高电平复位,通常用阻容复位电路实现

高于1.2v左右认为是高电平,开始硬件复位,上电后电压为Vcc,后降为0V

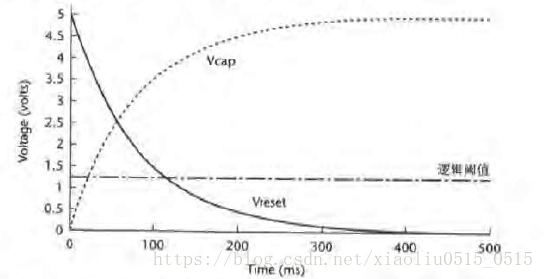

下图实线为R上电后电压曲线,Vcap为电容充电曲线

选择R和C值,通常RC>100ms,这是一个经验法则

标准10k电阻和10uF电容得到100ms时间常数

实际电路中增加一个复位按钮,很多开发板的最小系统是这个电路

二、阻容复位电路可靠性

1.上电延时带来风险

例如:电源100ms上电,复位电路中电容一直跟随电源电压,复位引脚一直是低电平,芯片只有复位信号到来才进入复位程序,因此芯片没复位

解决办法:降低电压滤波电容值,增大电源变压器容量,电源快速上电

2.晶振起振延时影响

阻容复位周期在晶振起振前结束

3.电源电压变化的影响

两个方面:瞬变和电压过低

瞬变:电源失灵,电源迅速降到0,cpu停止运行,电源恢复时复位,这里还受电源掉电时间的影响

电压过低:比如电源电压低1v,处理器不工作,但复位引脚电平逻辑不是0(低于1.2v才为零),芯片上电后不复位

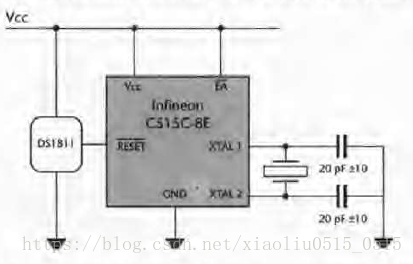

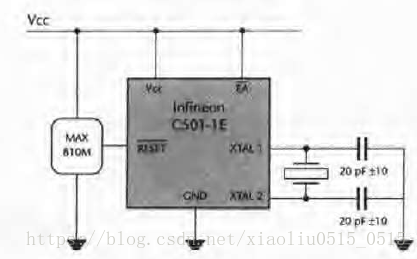

三、怎么实现可靠复位

使用外部芯片实现,完成两个功能:

1.系统上电时,提供100ms以上延时的复位信号,在振荡器和电源正常运行时复位电路在工作;

2.正常运行时电源电压小于某个值时启动复位电路。

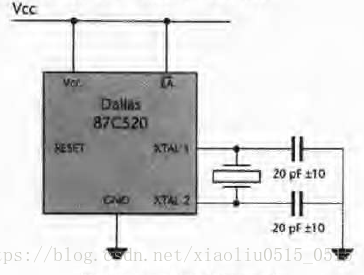

有的芯片片内带有复位电路

总结:复位电路一般设计都不会注意,当出现问题还不容易发现,前面提到一些复位电路不合理带来的可靠性风险,说了一下产生的原因,一般国内教材不会提及,只有在这受挫过的人才注意到,后面提到了使用外部芯片或者内部复位电路解决复位可靠性的办法。