能将C语言转换成硬件编码语言的高级综合HLS,跨越软硬件编码的隔阂,将软件编码的功能性与硬件编码的高速性结合起来,借助一些不断改进中的HLS工具(FPGA三巨头争破头),已然构成了一个时新的行业。虽然大多数HLS工具能够自动将一些循环体或者接口进行优化,但其软体转换而来的结构始终难以达到资深硬件工程师的标准,故而目前HLS还是需要人工操作,针对软体源代码进行更细节的优化,并且已经有HLS工程师这一说,不过其要求比较苛刻,软体编程和硬件编程是基础,熟悉各种算法和数字电路是闪光点。

行业背景

FPGA设计挑战

随着FPGA密度随着工艺几何尺寸的缩小而不断增长,设计复杂性使得继续使用传统的HDL设计流程变得越来越困难。尽管HDL语言和工具已经发展,但是设计周期仍然长得令人讨厌。

今天,在所有领域都遇到了具有挑战性的应用程序:高级驾驶员辅助系统(ADAS),5G,深度学习,计算机视觉,金融应用程序,航空航天和国防等。所有这些都需要几个处理内核,通常具有复杂的控制结构。这导致处理流水线不容易实现。探索架构实现以找到最佳策略来满足约束需要花费时间和成本,而且,项目进度压力以及设计成本增加了对首次实现正确实现的需求。在开发的后期阶段遇到瓶颈时,手工重构设计的某些部分实际上将使它步履维艰。

当需求改变时,经典的FPGA设计流程也会受到影响。在产品集成和验证阶段,经常出现后期规格变更或必须应用新约束的情况,这确实很常见。功能或性能的简单更改可能需要进行大量的设计修改。这些设计修改可能要求对体系结构进行更新,从而导致重写部分低级HDL实现。当然,这将导致潜在的较长的重新验证周期。

HLS加速FPGA设计的优势和挑战

为了帮助解决该问题,出现了高级综合(HLS)编译器,以使设计人员能够进入更高的抽象级别。这些对于设计的高度复杂部分特别有用,这些部分可以通过高级语言(例如C或C ++)轻松表达。更高的抽象级别使描述复杂算法和快速适应单调性变得更容易更改,更适合设计重用。

除了加快HDL设计的速度,HLS还具有简化设计验证的主要优势。使用HLS,可以确保在门中正确实现高级C / C ++描述。不必进行扩展且费时的位级仿真。而且,由于HLS采取的高级C / C ++代码是可执行的,因此它也用于高级应用程序验证。

HLS的另一个主要优点是能够通过以伪指令的形式指导编译器来快速探索不同的体系结构设计空间。这种能力是有代价的。为了指导编译器,设计人员必须首先对代码以及数据在函数和循环中的移动方式有深刻的理解。 HLS编译器是静态工具,对理解代码的动态特性没有任何帮助。此外,HLS编译器的行为通常难以预测最终的性能和资源利用率。因此,设计人员必须通过对相应的代码部分应用各种编译指示及其相关的参数设置,来手动探索设计空间,直到达到设计目标。

HLS工具流程

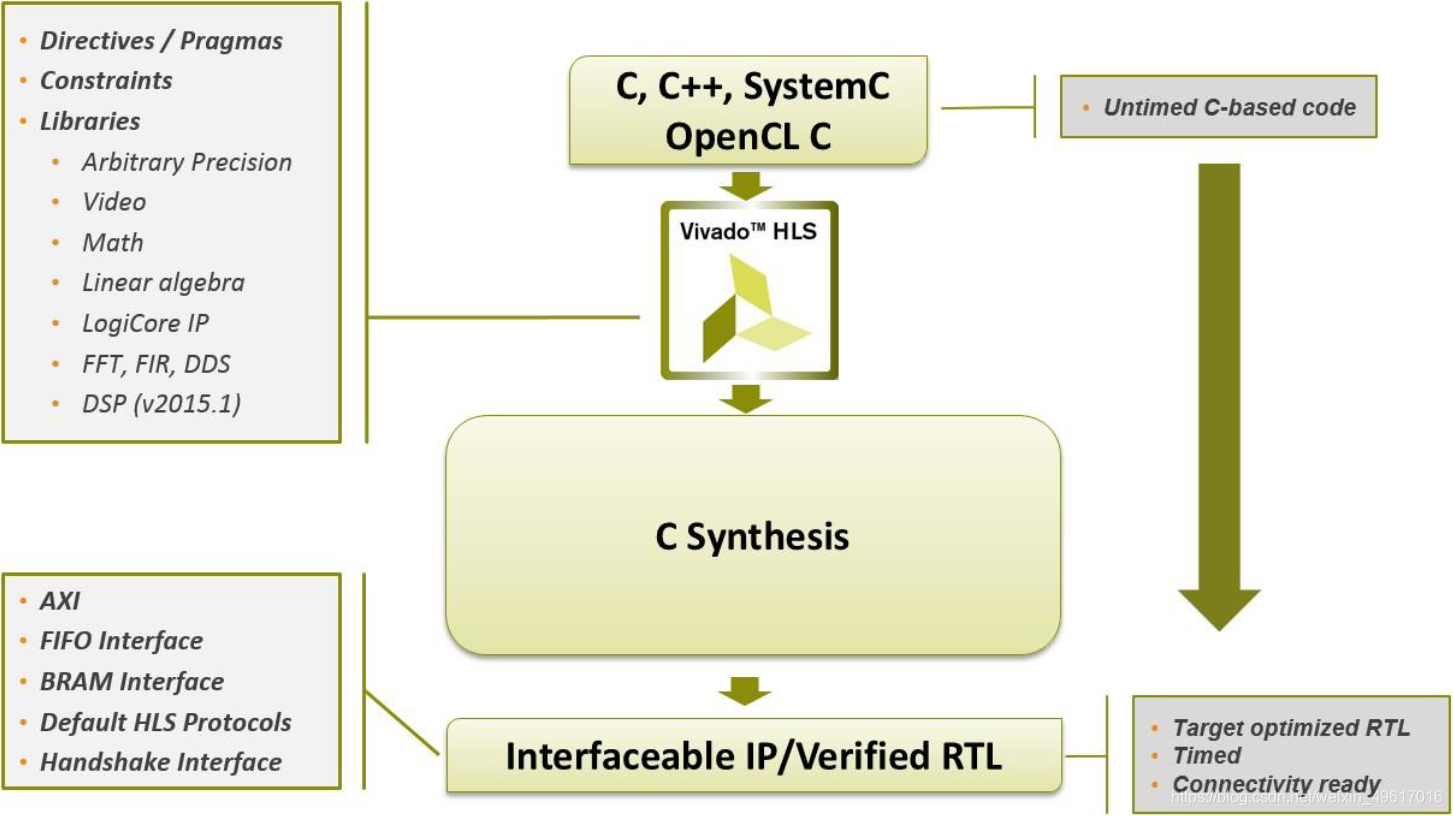

—>从C、c++、SystemC或OpenCL C开始

- 设计源代码和测试平台代码

—>C到RTL综合

- 调度和映射资源;

- 生成通用RTL代码;

- 使用综合指令进行优化

—>RTL验证

- 使用原始的C测试台;

- RTL模拟(XSim / ISim / ModelSim)

—>输出到

- IP目录;

- 系统生成器;

- DCP

HLS优势

- 对于软件工程,实现算法基于硬件(ASIC或者FPGA)的计算加速。

- 对于IC设计开发,从抽象的C层级进行功能设计。

- 对于硬件验证,从更抽象的层次进行功能性验证,加速设计流程。