简易计算机系统综合设计设计报告(VHDL)

一、设计目的

完整、连贯地运用《数字逻辑》所学到的知识,熟练掌握EDA工具基本使用方法,为学习好后续《计算机原理》课程做铺垫。其次,了解Quartus II软件的应用,学习Quartus II环境下设计CPU的基本过程,掌握CPU设计代码的含义以及CPU的工作原理,了解CPU与内存RAM间的连接数据的传输过程,学习在Quartus II环境下建立模型机的具体过程。融会贯通本课程(数字逻辑)各章节的内容,通过知识的综合运用,加深对计算机系统各模块的工作原理及相互联系的认识。学习设计和调试计算机的基本步骤和方法,提高使用软件仿真工具和集成电路的基本技能。培养科学研究的独立工作能力,取得工程设计与组装调试的实践和经验。

二、设计内容

按照给定的数据通路、数据格式和指令系统,使用 EDA 工具设计一台用硬连线逻辑控制的简易计算机。

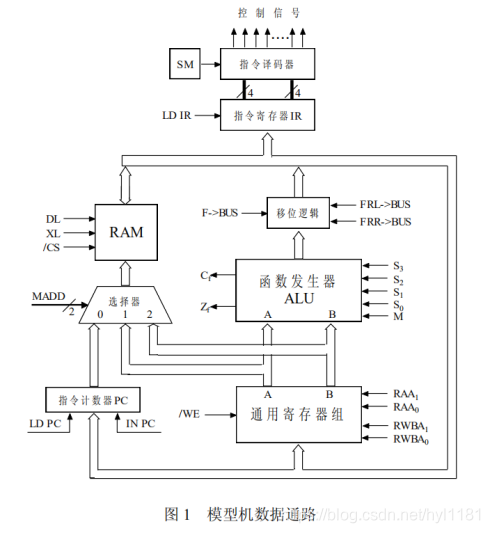

数据通路:

数据格式:数据字采用 8 位二进制定点补码表示,其中最高位(第 7 位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<+1 或-128≤X<+127。

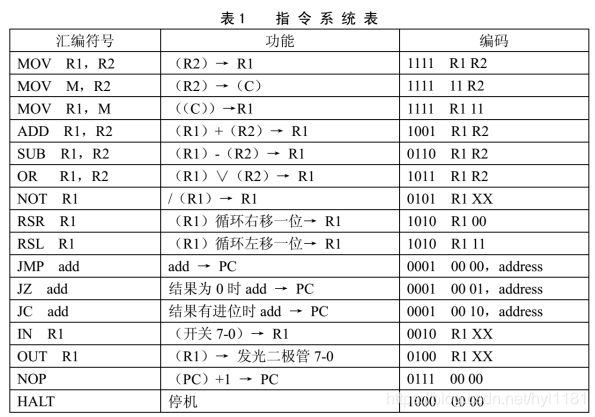

指令系统:

三、详细设计

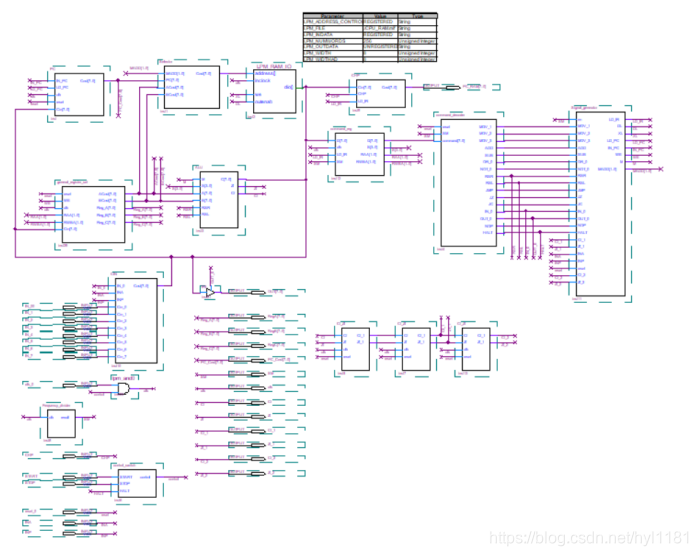

3.1整体架构(放大图见最后附图)

3.2各模块具体实现

1)指令计数器PC:

接口设计:

总线输入端、时钟输入端、复位输入端、两控制信号输入端、总线输出端。

功能实现:

a.复位信号有效时,计数器清零;

b.时钟下降沿到来时,如果LD_PC = ‘1’、IN_PC = ‘1’ 实现加一计数,或者LD_PC = ‘1’、IN_PC = ‘0’ 实现总线数据打入计数器,否则无操作;

c.输出为当前状态。

2)选择器:

接口设计:

PC输入端、通用寄存器组A口输入端、通用寄存器组B口输入端、两位使能输入端、总线输出端。

功能实现:

功能相当于一个多路复用器,对于不同的使能选择不同的输入输出:

a.MADD = ‘00’ 时选择PC输入端的输入输出;

b.MADD = ‘01’ 时选择通用寄存器组A口输入端的输入输出;

c.MADD = ‘10’ 时选择通用寄存器组B口输入端的输入输出;

d.MADD = ‘10’ 时输出高阻态。

3)指令寄存器IR:

接口设计:

总线指令输入端、时钟输入端、使能输入端、指令分解控制信号输入端、总线指令输出端,操作码S输出端,RAA、RWBA输出端。

功能实现:

功能相当于一个寄存器(时钟下降沿将信号传入指令译码器),外加无不受时钟控制的信号分解器(先提取出RAA、RWAB,以便时钟下降沿到来时,通用寄存器组读出数值的正确性)。

4)指令译码器:

接口设计:

总线指令输入端、复位输入端、使能输入端、各类指令控制信号输出端。

功能实现:

a.使能为有效时,对于传入的指令码译出各类指令控制信号;

b.复位信号有效时,不管使能如何,将HALT指令控制信号直为低电平,即无效(用于指令控制停机后的开机操作)。

5)控制器

接口设计:

使能输入端、各类指令控制信号输入端、Cf及Zf的各两个寄存信号输入端、各类控制信号输出端(LD_IR、DL、XL等)。

功能实现:

a.初始化各类控制信号;

b.使能为高电平,即有效时,执行阶段,对于不同的指令控制信号和条件信号进行将各类控制信号赋值,使执行指令时相应的功能块或者通路打开;

c.使能为低电平时,取指阶段,改变控制取值的信号,使取指正常进行。

6)通用寄存器组

接口设计:

置位输入端、使能输入端、时钟输入端、RAA及RWBA输入端、总线输入端、总线指令输出端、通用寄存器A口及B口输出端、ABC三寄存器输出端。

功能实现:

a.使能为0时,将总线数据通过RWBA选择写入三个寄存器;

b.使能为1时,将寄存器内的数据分别通过RAA、RWBA的选择从A口和B口输出;

c.置位时清零;

d.将寄存器内数据外显。

7)函数发生器ALU(+移位逻辑)

接口设计:

使能输入端、操作码输入端、通用寄存器组A口及B口输入端、两移位信号输入端、总线输出端、进位Cf及结果为0信号Zf输出端。

功能实现:

a.对于A口及B口传入的数据,根据操作码和控制信号的不同执行不同的操作,;

b.将结果从总线传出,并判断是否有进位和结果是否为零。

8)开关输入

接口设计:

控制台信号INA及INP输入端、指令控制信号IN_0输入端、八个开关信号输入端、总线输出端。

功能实现:

当IN_0或INA或INP等于1 时将开关上的数据打入总线。

9)分频器

接口设计:

原时钟输入端、分频后时钟输出端。

10)钟控开关

接口设计:

STRAT及STOP控制台信号输入端、HALT指令控制信号输入端、control信号输出端。

功能实现:

根据输入信号输出控制系统开关的信号,与时钟进行与操作,实现对系统的控制。

11)Cf、Zf寄存器

接口设计:

Cf及Zf输入端、时钟输入端、置位输入端、Cf_1及Zf_1输出端。

功能实现:

通过串联三个寄存器,实现Cf及Zf的寄存,为下一执行阶段为跳转时提供条件。

12)CHP

接口设计:

RAM输入端、控制台信号CHP输入端、使能输入端、RAM值输出端。

功能实现:

通过CHP与LD_IR的控制,输出当前PC对应的RAM内相应内存单元的值。

四、工程文件

工程文件、报告部分请参见:https://download.csdn.net/download/hyl1181/12647130