前言

学习Verilog和学习任何一门编程语言一样,都需要从语法开始,不会语法去学习设计是几乎不可能的,当然从另一门类似语言转来的除外(例如VHDL是你的第一门硬件描述语言)。学会了语法不懂硬件思维也不可以,因为你不能使用软件思维来设计硬件电路。

本系列其他博文:

初学者值得一读的博文:

FPGA/ASIC初学者应该学习Verilog还是VHDL?

本文以极简的风格来谈谈这一篇博文的话题,verilog中的初级语法。

正文

注释

Verilog提供了两种注释的方式,分别为:

- 单行注释

//This is a single line comment

当然,你这样写也可以:

/////////////////// This is Okay!

这是因为双斜杠后面的都是注释!

- 多行注释

/* this is a

multiple line

comments!

*/

空格

verilog中的空格是起到缩进的作用,基本没有什么要求,你可以使用TAB键,空格键,回车键在代码中的任何位置,它几乎会被语法忽略,但是为了代码的可读性,还是建议遵守一定的规则。

注:空格在字符串中不会被忽略!

例如:

always@(*) begin

//--------

c = a + b;

adder inst_adder(

.i_a(i_a),

.i_b(i_b),

.o_dout(o_dout),

.o_sum(o_sum)

);

end

以美观易读为准,或者和公司标准保持一致,做个正常人。

操作符

操作符分为三种,本文不详细展开:

- 一元运算符应显示在其操作数的左侧

- 二进制运算符应出现在其操作数之间

- 条件运算符有两个单独的运算符,它们将三个操作数分开

例如:

//一元操作符

b = ~a;

//二元操作符

assign c = a & b;

//条件操作符

assign z = en ? a : b;

数字格式

我们最常见的数字表示为十进制,然而,数字还可以表示为二进制,八进制,以及十六进制等,其中二进制和十六进制较为常见。

默认情况下,Verilog仿真器会把数字默认为十进制,除非你使用特定的格式告诉它,你使用的是二进制,八进制或者十六进制。

例如:

3'b001;

3表示的是这个数字有多少位;b表示的是进制,这里表示的是二进制,八进制用o来表示,十六进制用h,十进制用d,当然如果不写进制,而默认为十进制。

例如:

reg [3:0] b = 10;

则b被初始化为十进制10;

如下分别为二进制,十六进制,八进制以及十进制的表示方法:

```c

3'b001; // this is binary

8'ha0; // this is hexadecimal

6'o12; // this is octal

4'd15; // this is decimal

Verilog 2001标准更新了一些用法,例如可以省去位宽也可以:

initial begin

a = 'b001; // this is binary

b = 'ha0; // this is hexadecimal

c = 'o12; // this is octal

d = 'd15; // this is decimal

end

这时,编译器会根据左边变量的位宽来自动扩展右边数值或者截位后赋值给左边。

还有需要注意的是,如果需要给一个有符号reg型变量赋值一个负数值,如何表达呢?

如下:

reg signed [7:0] a = -8'd21;

也就是说,负号必须放在位数的前面,如下这种写法就是错误的:

8'd-4; // Illegal

字符串

Verilog中的字符串使用场景大多数是在仿真时使用,它由双引号包裹着(位于双引号之间)。字符串中的一个字符使用一个字节来存储。

"Hello World!" // String with 12 characters -> require 12 bytes

"x + z" // String with 5 characters

字符串中的字符不能分割成多行来写,如下是不合规的:

"How are you

feeling today ?" // Illegal for a string to be split into multiple lines

标识符

标识符就是变量的名字以及模块的名字,它们可以有大小写字母,数字,美元符号,下划线构成,但是美元符号$以及数字不能作为标识符的开头,如下:

integer var_a; // Identifier contains alphabets and underscore -> Valid

integer $var_a; // Identifier starts with $ -> Invalid

integer v$ar_a; // Identifier contains alphabets and $ -> Valid

integer 2var; // Identifier starts with a digit -> Invalid

integer var23_g; // Identifier contains alphanumeric characters and underscore -> Valid

integer 23; // Identifier contains only numbers -> Invalid

关键字

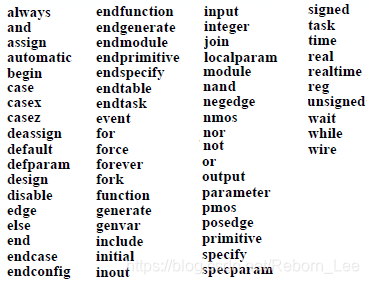

关键字是保留用于定义语言结构的特殊表示符,用小写字母表示,每一种语法都有其关键字,Verilog语法也不例外,你在给模块以及变量命名的时候应该避开这些关键字:

verilog修订

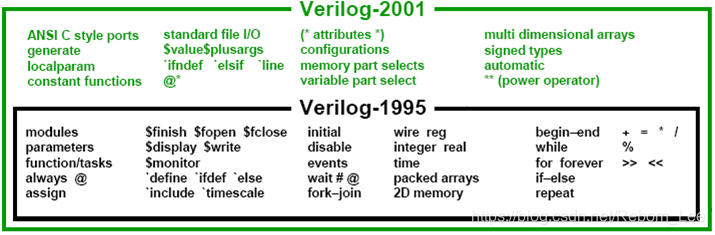

多年来,Verilog进行了一些修订,从1995到2001年进行了更多的添加,如下图:

写在最后

我的微信公众号:FPGA LAB

我的知乎二维码 :