通过TICC3200+TLV320AIC3254录音,将录取的音频传至电脑上播放,发现录得声音特别小:

考虑应该是麦克风的增益问题,然后从程序里面找到音频的芯片的配置函数,在这个函数里面找到mic相关的配置,代码:

if(mic)

{

unsigned char reg1 = 0x00; // TI3254_MICBIAS_CTRL_REG

unsigned char reg2 = 0x00; // TI3254_LEFT_MICPGA_P_CTRL_REG

unsigned char reg3 = 0x00; // TI3254_LEFT_MICPGA_N_CTRL_REG

unsigned char reg4 = 0x00; // TI3254_RIGHT_MICPGA_P_CTRL_REG

unsigned char reg5 = 0x00; // TI3254_RIGHT_MICPGA_N_CTRL_REG

unsigned char reg6 = 0x00; // TI3254_FLOAT_IP_CTRL_REG

AudioCodecPageSelect(TI3254_PAGE_8); // Select Page 8

AudioCodecRegWrite(TI3254_ADC_ADP_FILTER_CTRL_REG, 0x04); // Adaptive Filtering enabled for ADC

AudioCodecPageSelect(TI3254_PAGE_0); //Select Page 0

AudioCodecRegWrite(TI3254_ADC_SIG_P_BLK_CTRL_REG, 0x2); // ADC Signal Processing Block PRB_P2

if(mic & AUDIO_CODEC_MIC_LINE_IN)

{

reg1 |= 0x40; // MICBIAS powered up

reg2 |= 0x40; // IN1L is routed to Left MICPGA with 10k resistance

reg3 |= 0x40; // CM is routed to Left MICPGA via CM1L with 10k resistance

reg4 |= 0x40; // IN1R is routed to Right MICPGA with 10k resistance

reg5 |= 0x40; // CM is routed to Right MICPGA via CM1R with 10k resistance

reg6 |= 0xC0; // IN1L input is weakly driven to common mode. Use when not routing IN1L to Left and Right MICPGA and HPL, HPR

}

if(mic & AUDIO_CODEC_MIC_MONO)

{

reg1 |= 0x40; // MICBIAS powered up

reg2 |= 0x00;

reg3 |= 0x10;

reg4 |= 0x10; // IN2R is routed to Right MICPGA with 10k resistance

reg5 |= 0x40; // CM is routed to Right MICPGA via CM1R with 10k resistance

reg6 |= 0x10; // IN2R input is weakly driven to common mode. Use when not routing IN2R to Left and Right MICPGA

}

if(mic & AUDIO_CODEC_MIC_ONBOARD)

{

reg1 |= 0x40; // MICBIAS powered up

reg2 |= 0x00;

reg3 |= 0x04;

reg4 |= 0x04; // IN3R is routed to Right MICPGA with 10k resistance

reg5 |= 0x40; // CM is routed to Right MICPGA via CM1R with 10k resistance

reg6 |= 0x04; // IN3R input is weakly driven to common mode. Use when not routing IN3R to Left and Right MICPGA

}

AudioCodecPageSelect(TI3254_PAGE_1); //Select Page 1

AudioCodecRegWrite(TI3254_MICBIAS_CTRL_REG, reg1);

//Route IN2L not routed

AudioCodecRegWrite(TI3254_LEFT_MICPGA_P_CTRL_REG, reg2);

//Route IN2R CM1L to LEFT_N with 10K input impedance

AudioCodecRegWrite(TI3254_LEFT_MICPGA_N_CTRL_REG, reg3);

//Route IN2R to RIGHT_P with 10K input impedance

AudioCodecRegWrite(TI3254_RIGHT_MICPGA_P_CTRL_REG, reg4);

//Route CM1R to RIGHT_M with 10K input impedance

AudioCodecRegWrite(TI3254_RIGHT_MICPGA_N_CTRL_REG, reg5);

AudioCodecRegWrite(TI3254_FLOAT_IP_CTRL_REG, reg6);

//make channel gain 0dB, since 20K input

//impedance is used single ended

AudioCodecRegWrite(TI3254_LEFT_MICPGA_VOL_CTRL_REG, 0x5F); // 0.0dB

//Unmute Right MICPGA, Gain selection of 6dB to

//make channel gain 0dB, since 20K input

//impedance is used single ended

AudioCodecRegWrite(TI3254_RIGHT_MICPGA_VOL_CTRL_REG, 0x5F); // 0.0dB

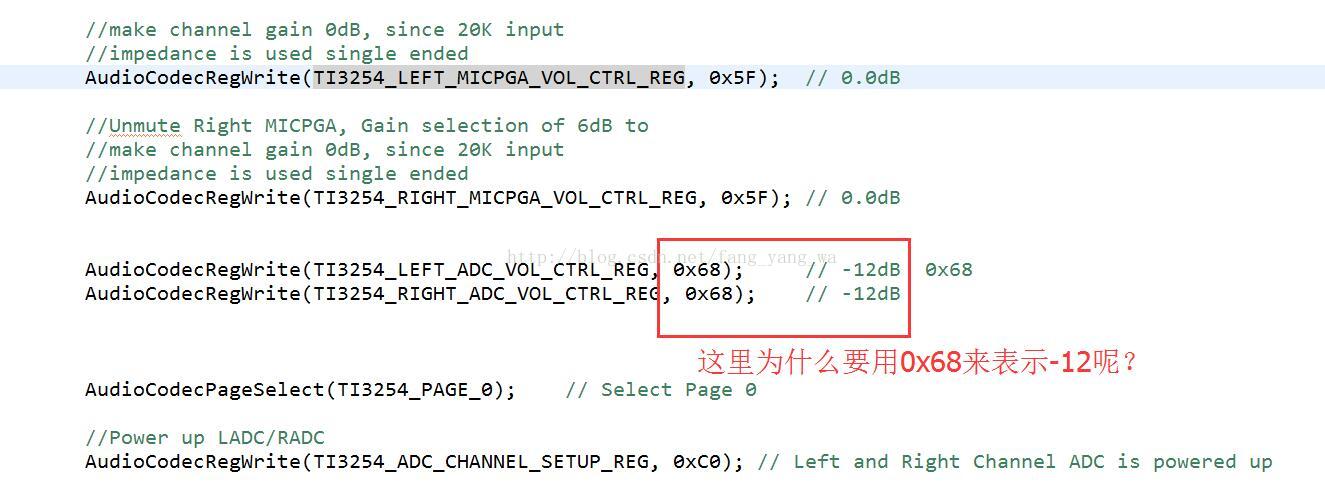

AudioCodecRegWrite(TI3254_LEFT_ADC_VOL_CTRL_REG, 0x68); // -12dB 0x68

AudioCodecRegWrite(TI3254_RIGHT_ADC_VOL_CTRL_REG, 0x68); // -12dB

AudioCodecPageSelect(TI3254_PAGE_0); // Select Page 0

//Power up LADC/RADC

AudioCodecRegWrite(TI3254_ADC_CHANNEL_SETUP_REG, 0xC0); // Left and Right Channel ADC is powered up

//Unmute LADC/RADC

AudioCodecRegWrite(TI3254_ADC_FINE_GAIN_ADJ_REG, 0x00); // Left and Right ADC Channel Un-muted. Left and Right ADC Channel Fine Gain = 0dB,

}

//make channel gain 0dB, since 20K input

//impedance is used single ended

AudioCodecRegWrite(TI3254_LEFT_MICPGA_VOL_CTRL_REG, 0x5F); // 0.0dB

//Unmute Right MICPGA, Gain selection of 6dB to

//make channel gain 0dB, since 20K input

//impedance is used single ended

AudioCodecRegWrite(TI3254_RIGHT_MICPGA_VOL_CTRL_REG, 0x5F); // 0.0dB

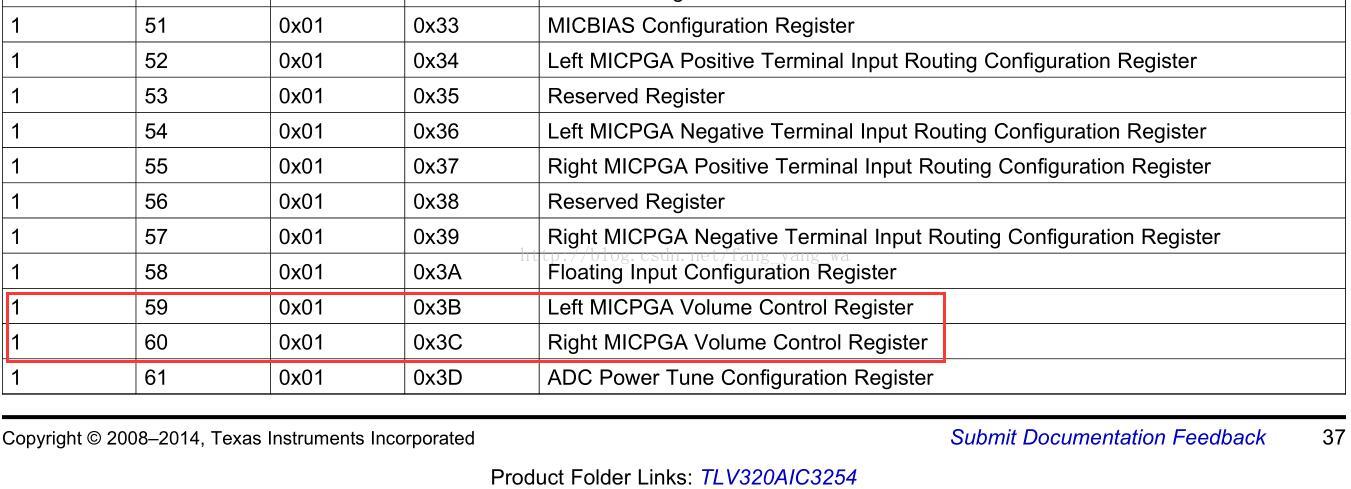

#define TI3254_LEFT_MICPGA_VOL_CTRL_REG 0x3B

#define TI3254_RIGHT_MICPGA_VOL_CTRL_REG 0x3C

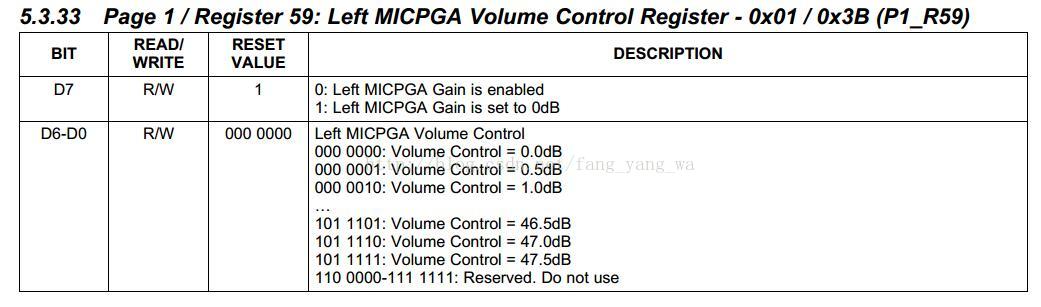

初步确定,应该是这两个寄存器来调节增益的,但是增益的范围是多少呢?继续查找数据手册得到:

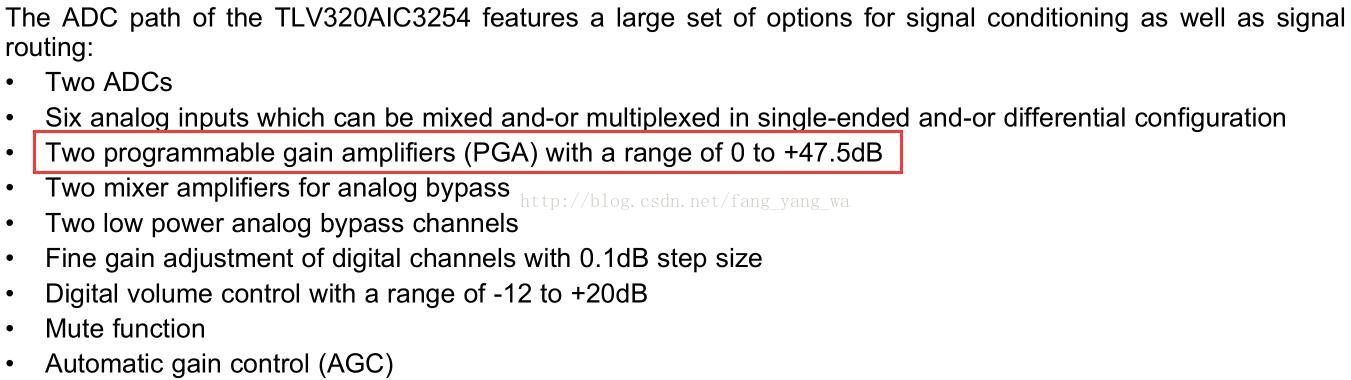

知范围是0—47.5dB,这里带着小数点,怎么用十六进制来表示呢,继续找数据手册,但是找遍了也没有找到,于是乎就自己试,比如增益20dB就用0X14来表示,这里试了很长很长时间也没有成功。期间有一个问题很是不解:

带着这个问题和增益值的设置问题百度,百度到一个TI官网的链接:

http://www.ti.com.cn/product/cn/TLV320AIC3254/technicaldocuments

这份文档的名字“TLV320AIC3254 Application Reference Guide

Reference Guide”,在这个文档里面有关于每个寄存器的值是怎么设置的。

恍然大悟。

【但是需要注意的是:这些寄存器分为Page1、Page2、一直到Page44,在Page1和Page2里面都有0X3B和0X3C这两个寄存器,当然作用和完全不同的,刚开始的时候我就是没有注意,在这里困惑了好久,直到和数据手册一个一个比对了一下才反应过来。】

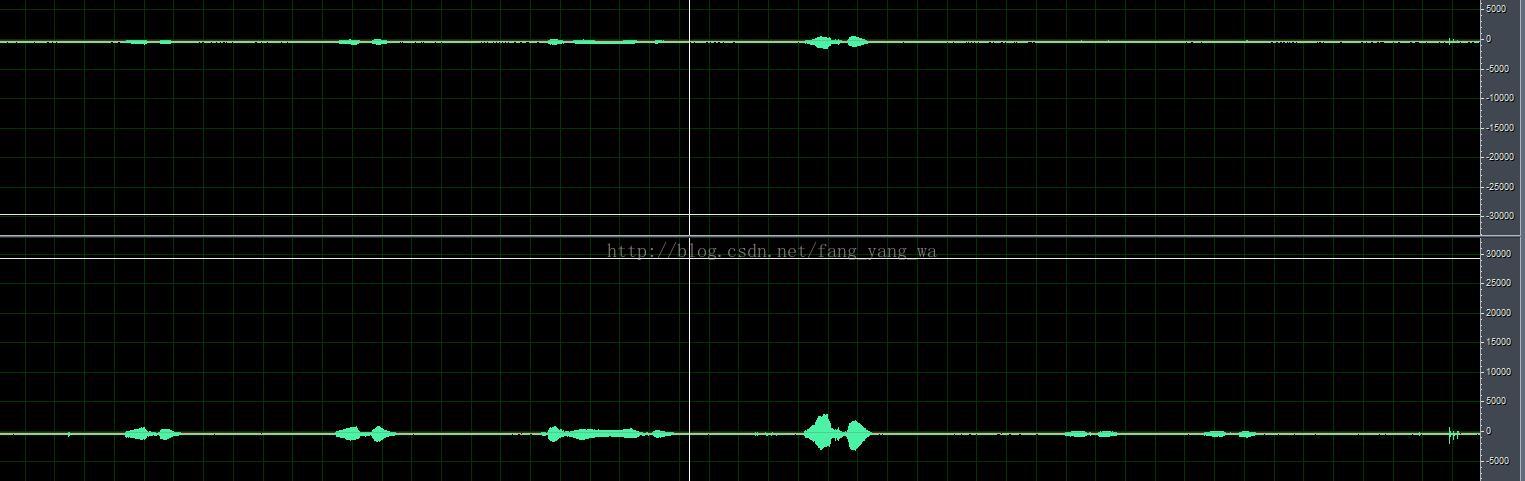

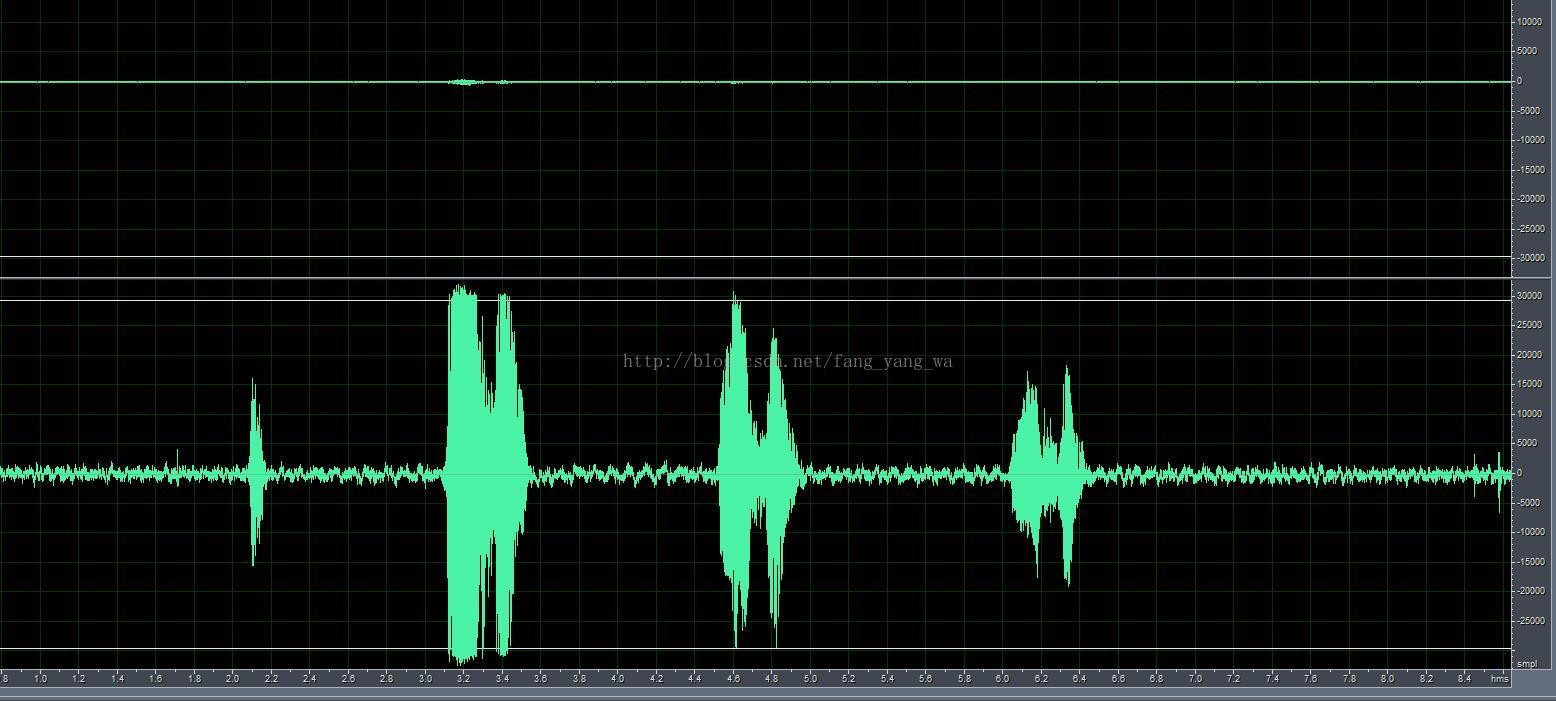

将增益设置为47.5之后波形: