项目名称

单端口rom

具体要求

将0-1023存入rom,并读出

设计架构

地址从0-1023需要10位,数据同样如此

代码设计

verrilog代码设计

1.创建mif文件,数据最大为1024,数据位宽10位,存储深度为1024

2.创建rom ip核

顶层模块设计

扫描二维码关注公众号,回复:

11384568 查看本文章

module rom_top(

input clk,

input rst_n,

output [9:0] q

);

wire [9:0]addr;

rom_ctrl rom_ctrl(

.clk(clk),

.rst_n(rst_n),

.addr(addr)

);

my_rom my_rom(

.address(addr),

.clock(clk),

.q(q)

);

endmodulerom_ctrl模块设计

module rom_ctrl(

input clk,

input rst_n,

output reg[9:0]addr

);

always@(posedge clk or negedge rst_n)

if(!rst_n)

addr<=10'd0;

else if(addr<10'd1023)

addr<=addr+1'd1;

else

addr<=10'd0;

endmodule仿真代码

`timescale 1ns/1ns

module rom_top_tb;

reg clk;

reg rst_n;

wire [9:0] q;

rom_top rom_top(

.clk(clk),

.rst_n(rst_n),

.q(q)

);

initial clk=0;

always #10 clk=~clk;

initial begin

rst_n=0;

#100

rst_n=1;

#20700

$stop;

end

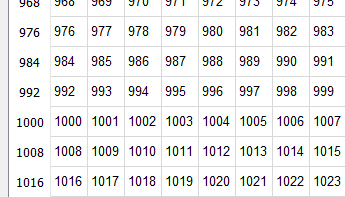

endmodule仿真结果

数据延迟地址一拍读出