《SystemVerilog验证-测试平台编写指南》学习 - 第1章 验证导论

测试平台(testbench)的功能

- 产生激励(Generate stimulus);

- 把激励输入到待测设计上(DUV,Design Under Verification);

- 产生预期(Generate Expectation);

- 捕捉响应(Capture response);

- 检验响应的正确性(Check the response for correctness);

- 根据验证目标评估验证进度(Measure the progress against the overall verification goals);

验证四要素:

- 灌激励:(产生输入信号)

- 做预期:(产生预期结果)

- 集响应:(收集输出信号)

- 作比较:(比较响应和预期结果)

方法学基础

本书采用如下原则:

- 受约束的随机激励;

- 功能覆盖率;

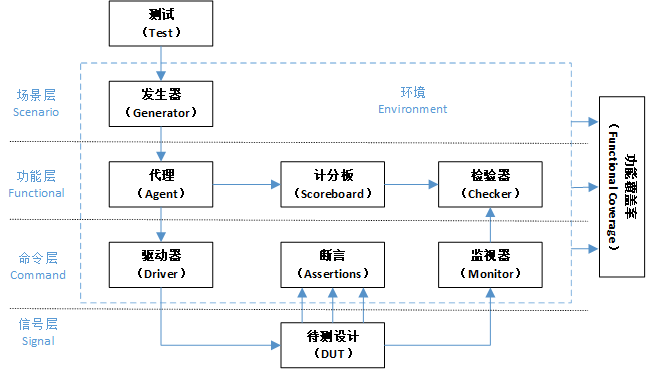

- 使用事务处理器的分层测试平台;

- 对所有测试通用的测试平台;

- 独立于测试平台之外的个性化测试代码;

这些原则是相关联的。随机激励对测试复杂设计十分关键。

定向测试:找出设计中预期的漏洞;

随机测试:找出预料不到的漏洞;

当使用随机激励时,需要用功能覆盖率来评估验证进度。一旦开始使用自动生成的激励,就需要一种能够自动预测结果的方式 -- 通常是计分板或参考模型。

1. 受约束的随机激励

为什么要约束?

答:

虽然你希望仿真器能产生随机激励,但同时有不希望这些激励数值完全随机。

你的随机化对象是什么?

需要广泛地考虑所有的设计输入,而不是仅仅是数据字段,如下所列:

- 设备和环境配置;

你应该对整个环境的配置进行随机化,包括仿真的时长、设备的数量,以及它们的配置方式。当然,你需要创建约束以确保配置的合法性。- 输入数据;

你需要事先估计好所有的分层协议和错误注入,以及计分板的内容和功能覆盖率。- 协议异常、错误和违例;

应该尽量尝试去仿真在实际的硬件中可能出现的错误,而且应该针对所有可能出现的错误。- 时延和同步;

尝试协调各个驱动器使他们能够在不同的速率下进行通信。

2. 功能覆盖率

你需要知道哪些部分已经被验证过,这样才能对验证计划中的项目进行核对。

功能覆盖率的测量和使用:

- 添加代码用于监控进入设备中的激励,以及设备对激励的反应,并据此确定哪些功能已经被验证过;

- 运行几次仿真,每次使用不同的种子,合并报告;

- 分析结果,采用新的激励测试未被测试到的条件和逻辑;

随机测试需要使用反馈。最初的测试会被运行很多次,使用不同的种子,创建很多互异的输入序列。但是到了最后,即时使用新的种子,所产生的激励也很可能无法在设计空间中探测到新区域。

随着功能覆盖率逐渐接近极限,你需要改变测试,以期望能找出新的方法去达到那些尚未被覆盖的区域。这被称为“ 覆盖率驱动的验证 ”

在受约束的随机激励中很少采用动态反馈。相反地,需要手工分析覆盖率报告,然后调整随机约束。

3. 分层的测试平台

不分层的的测试平台或者低层次的Verilog测试就是初学Verilog时写的简单testbench那种形式。