基于cadence的四位全加器设计及仿真。

1、实验原理

板图,也就是芯片的原理图。通过学习板图的绘制,可以有效地提高对芯片的工作原理的认识。在版图设计中,需要掌握许多的规则,能够按照特定的规范优化,才能完成一个精美的板图。这里只是实验,所以没有那么严格。如果想要深入学习版图设计的话,这里的知识还是权当感受,找其他专业的书籍学习为好。本实验仅为对版图设计感兴趣的人提供一次体验。

2、实验操作

一、打开软件

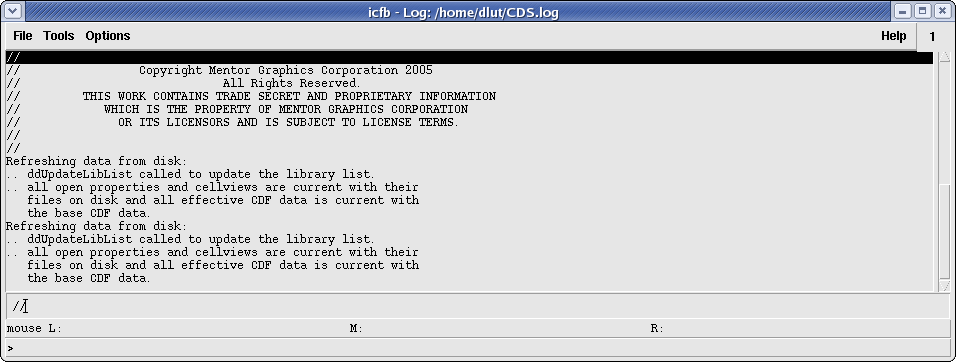

由于是在linux下操作,打开软件的话也要在相应的目录下打开。这里根据个人的资源自由选择。我们实验要求的smic013工艺,所以也是有相应的目录的。实在不行的可以在windows上使用,反正操作可能差不多。其他板图设计的软件应该也是可以的,不过操作可能有变。这里附一张工作界面图。

二、新建工程

在tools》library manager【双击】,进入库管理文件。

新建library》输入库名》选择第二个》选择库引用的工艺库

新建 cell view》新建原理图(下面可以选择其他的类型,如板图,模型图等)。

三、原理图设计

根据所需设计导入原理图即可。

三、原理图仿真

在tools》analog Environment中进入仿真界面,设置好仿真参数,即可进行仿真。其中比较重要的是导入输入输出信号。注意,仿真的对象应该是加了激励源以后的电路。

四、板图设计

将原理图的文件对应加入到板图设计图中,将每一个连线都对应,这样可以得到板图。然后进行尺寸验证、功能验证。通过两个后,生成标准文件。

五、后仿真

将前面生成的标准文件加入到仿真库的首选项,再次重复仿真操作,完成后仿真。

六、实际生产前的调整

在实际生产(也就是流片)前,还需要对设计的可靠性以及密度分布等问题调整。最后,才能送到加工场,将晶圆加工成所需的芯片。

总结:原本是想将操作一一展现以提高个人对每个操作的理解。但是,根据实际设计一个简单的4位全加器的历程来看,工作量实在太大。单靠一个人想完成基本不可能。前面的只是一个大框架的操作,实际上在设计4位全加器前先得设计一位全加器,一位全加器需要仿真和板图设计。总之,一个完全的新手(比如本人),想要完成设计并写出实验报告至少得四天(大部分时间都在板图的尺寸调整上)。

顺便提一下,版图设计所需的资料:工艺手册(必备),软件操作指南(必备,用过的忽略),实验手册(有最好),linux常用指令(有最好)。

3、实验结果

由于要交实验报告,这里就不展示。等这门课上完了后,如果有时间再展示。

4、实验感受

板图设计是真的累。在学习电路设计时觉得电路设计真的烦,每个器件都要在器件库中寻找。学习了板图设计,才知电路设计是真的直接。