在《FPGA editor 的使用之二 ------ 增加delay之一》这篇博文里,讲述了 一种 增加delay的场景和方法,那个典型的场景就是FPGA内部信号输出到PAD上,为了保证时序要求,增加了延时。在本篇博文里,介绍另一种增加延时的场景。

在一般的项目中,都会有外部输入到FPGA内部的信号,参入到内部逻辑。此时外部信号从PAD传入FPGA内部,在debug时,为了解决时序问题,可能需要增加输入延迟。那么此时,也可以使用FPGA editor来实现。

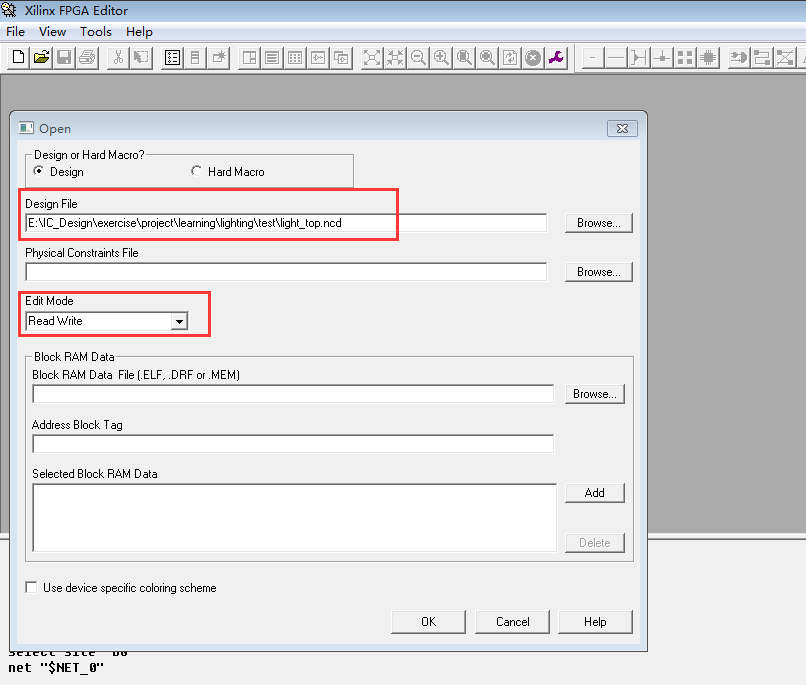

还是以《FPGA editor 的使用之二 ------ 增加delay之一》中的例子来介绍。首先,使用FPGA editor打开项目的 xxxx.ncd(本例中是light_top.ncd)。

这个例子很简单,只有clk 和 rst 两个输入信号,本博文以rst信号为例。本例中,rst输入PAD例化到“B8”引脚。使用下列脚本找到这个PAD。

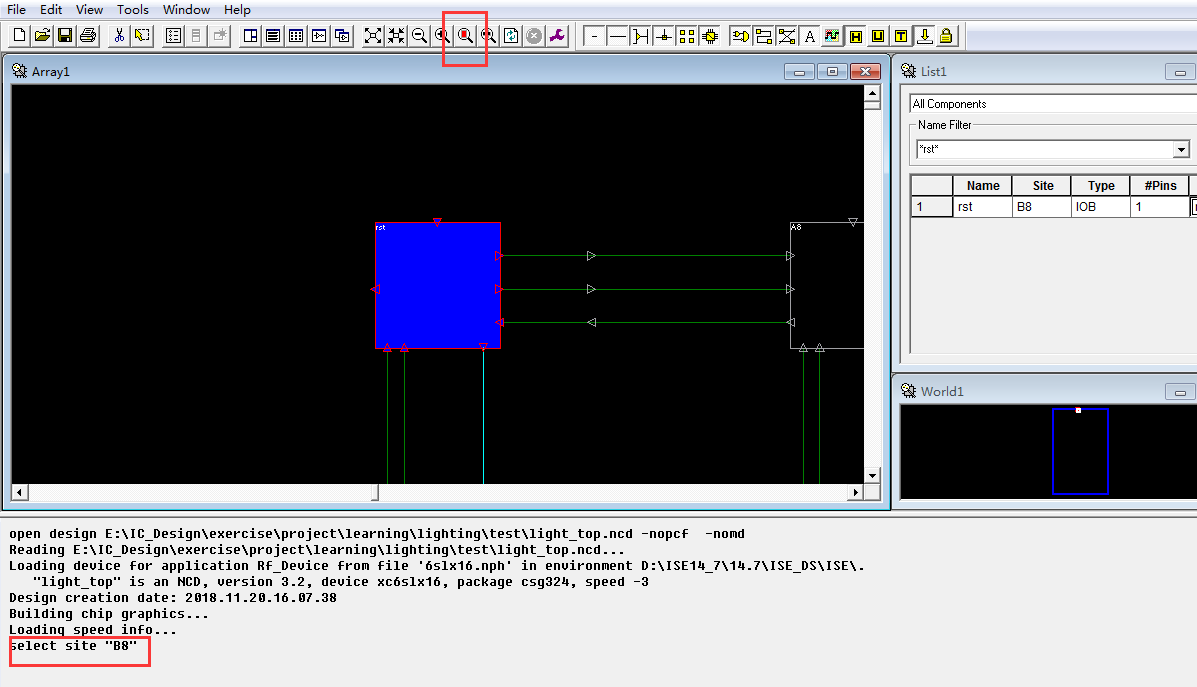

select site “B8” 输入enter

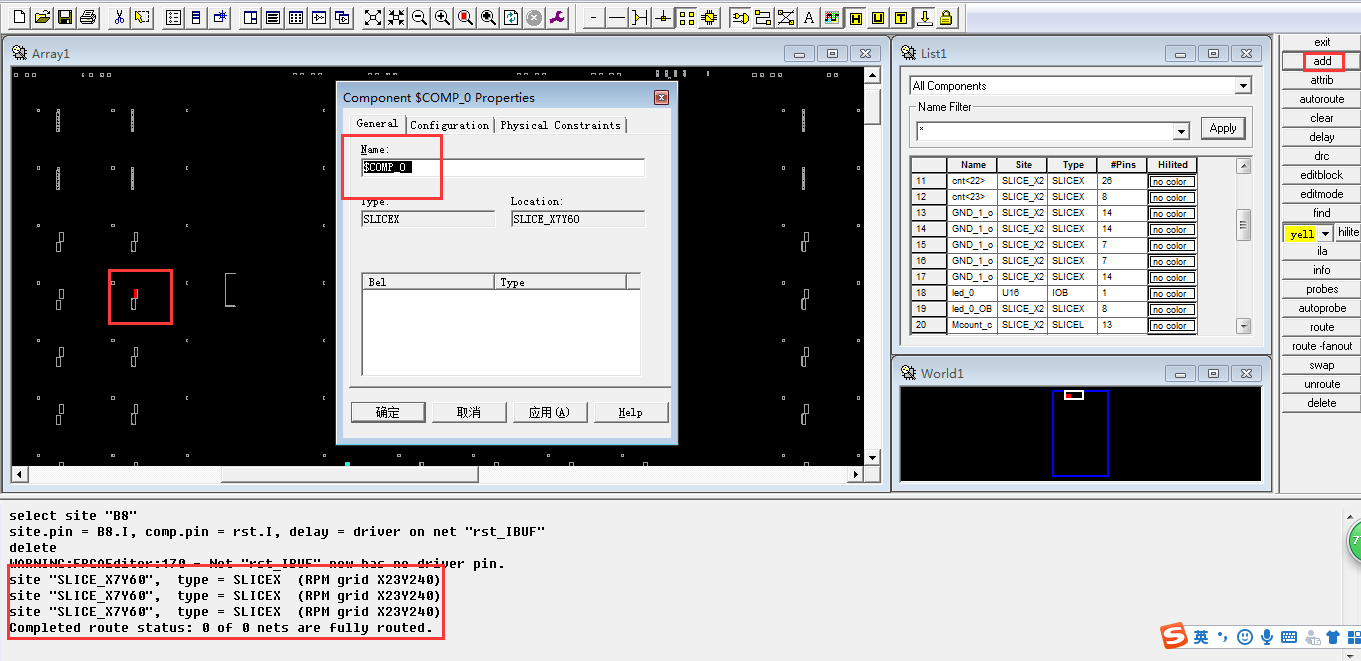

再单击zoom selection,选中它。如下图所示。

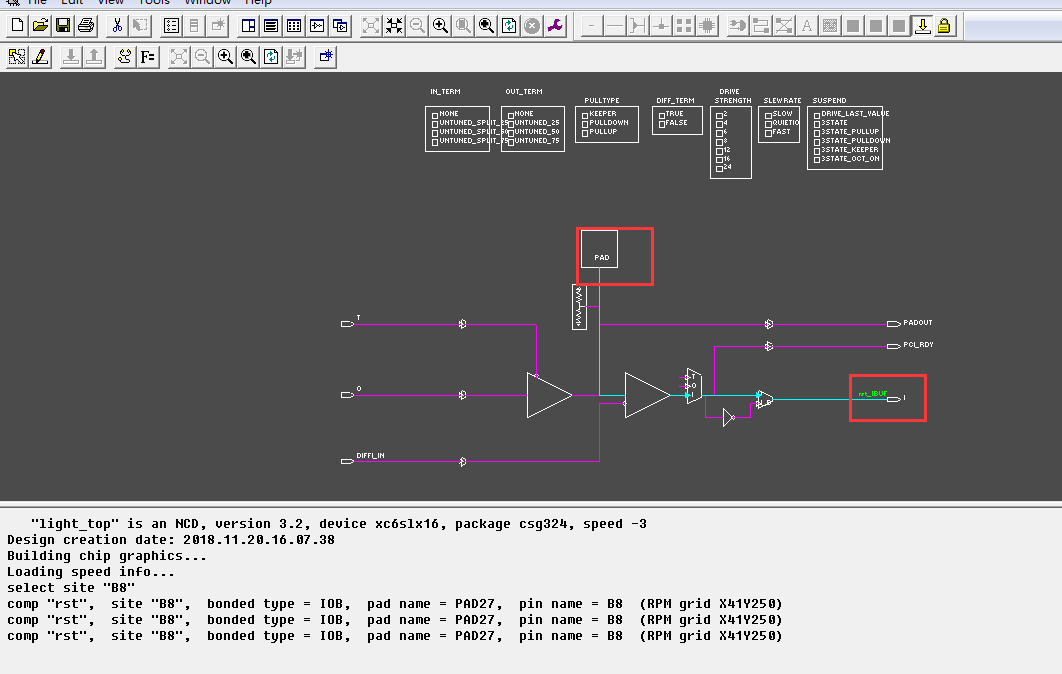

双击这个PAD,发现rst信号经过PAD后,从PAD的 I 端口 输出,送到其他逻辑里使用。如下图所示。

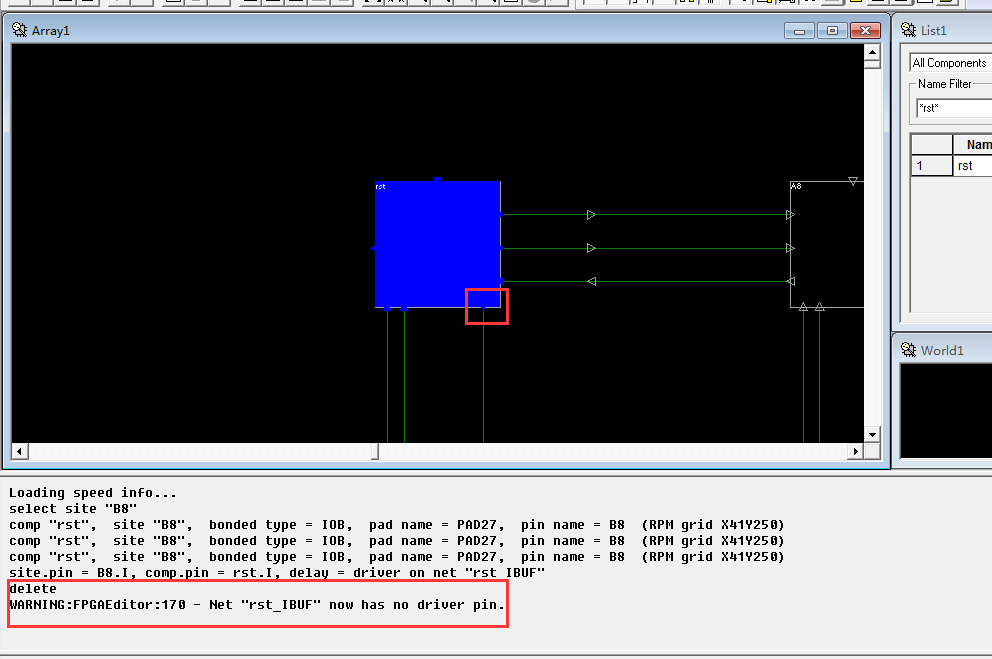

回到主界面,选中这个PAD的 I 引脚,如下图所示。右击鼠标,选择delete。

在这个PAD附近找一个空闲的slice,单击add,添加一个new component,如下图所示。

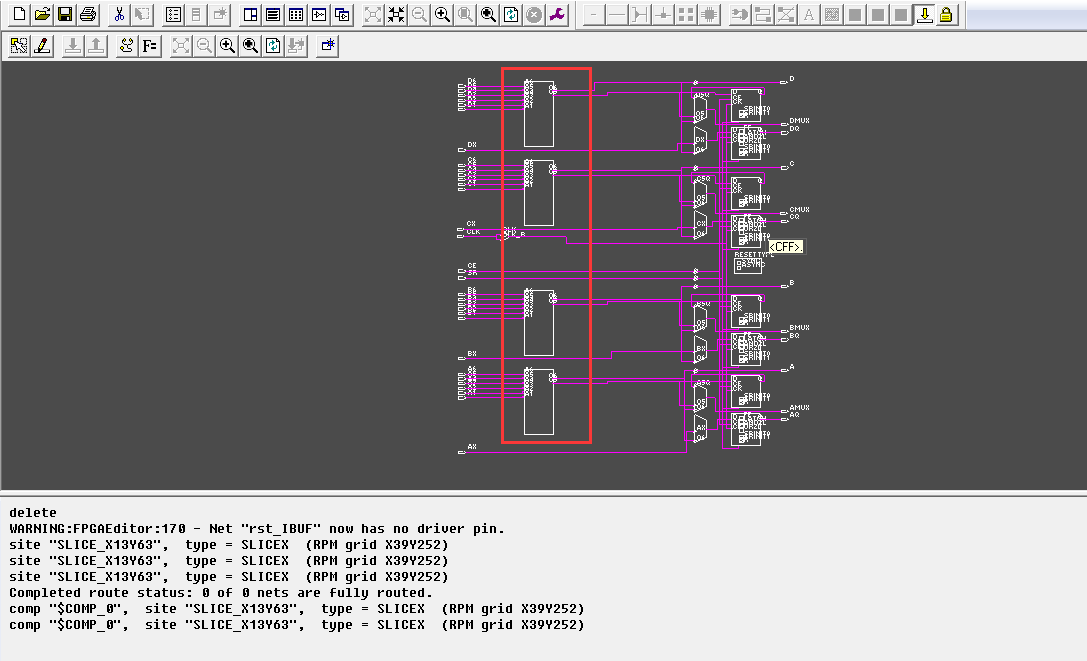

双击这个slice,可以看到内部电路图,里面有四个LUT,如下图所示。

本例中选择最上面一个LUT来增加延时,将rst信号穿过PAD后的信号重新连接到这个slice的D6引脚上。使用如下命令行:

select pin "SLICE_X13Y63.D6" 回车

select pin "B8.I" 按住Ctrl键,回车,然后 点击 add

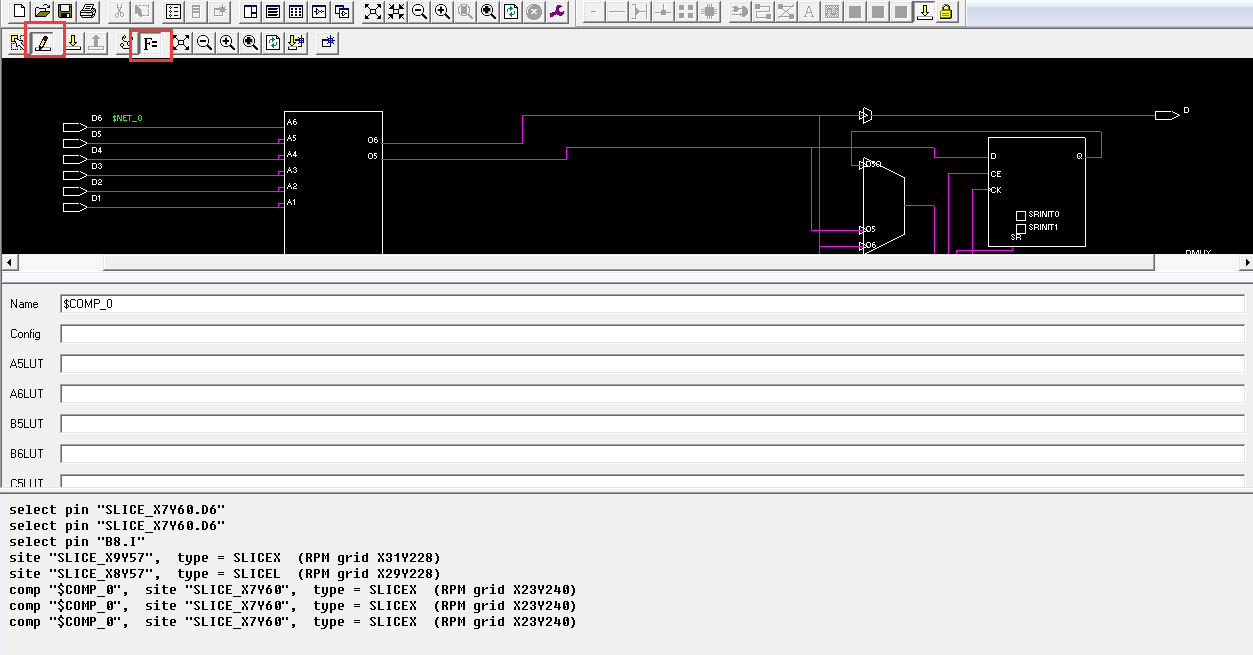

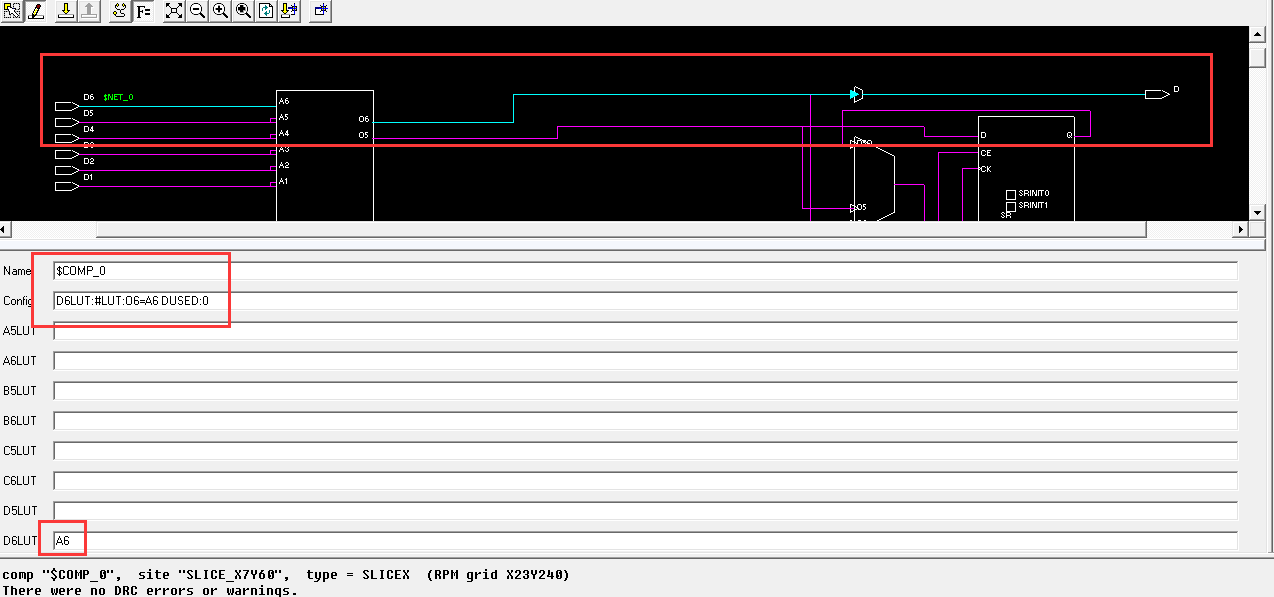

再双击这个slice,修改内部逻辑。如下图所示。

在config框里做如下修改。

上面的修改,即是将 rst信号经过PAD后的信号送入SLICE_X7Y60的D6LUT,然后从SLICE_X7Y60的D端输出。

在增加延时之前,rst信号经过PAD后会通过 net rst_IBUF,送给内部其他逻辑使用,在最开始我们只是delete了PAD的 I pin,并未delete掉net rst_IBUF。其实也不能delete掉这个net,因为内部可能有很多地方使用了这个net,如果delete掉,会引起内部逻辑紊乱,这也是只delete PAD的拼,而不delete net的 原因。所以,接下来要将上面传到SLICE_X7Y60的 D端的信号重新连接回net rst_IBUF。使用如下命令行:

select pin "SLICE_X7Y60.D" 回车

select net “rst_IBUF” 按住Ctrl键,点击add

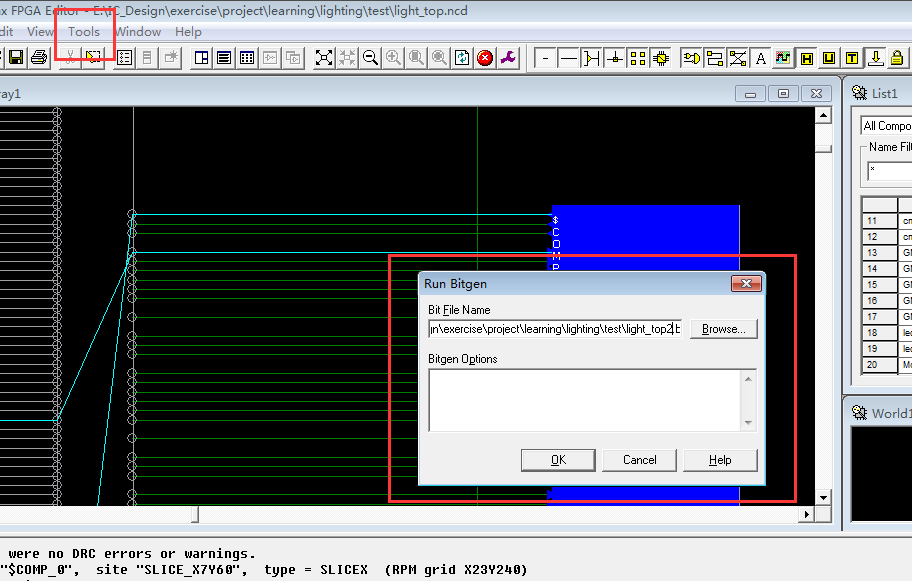

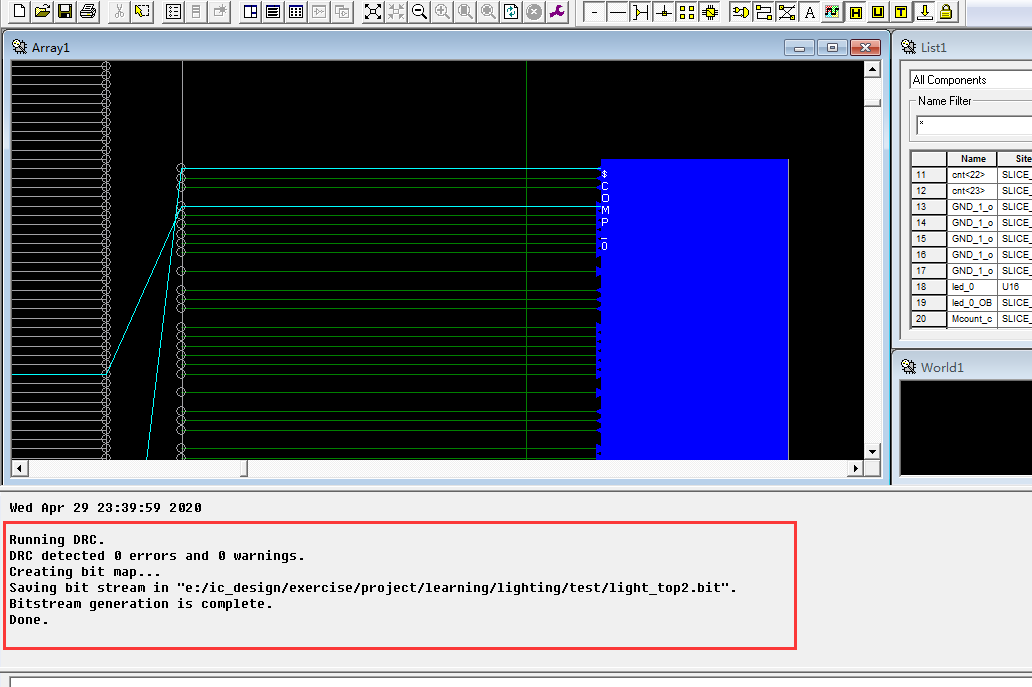

保存修改,然后在Tools里面选择 Run bitgen

到此为止,所做的修改已经改好了,并生成了 bit stream 文件,可以下载到板子测试了。