在MSP430单片机中,一个时钟周期 = MCLK晶振的倒数。如果MCLK是8MHz,则一个时钟周期为1/8us。

一个机器周期 = 一个时钟周期,即430每个动作都能完成一个基本操作。

一个指令周期 = 1~6个机器周期,具体根据具体指令而定。

另外,指令长度只是一个存储单位,与时间没有必然的关系。

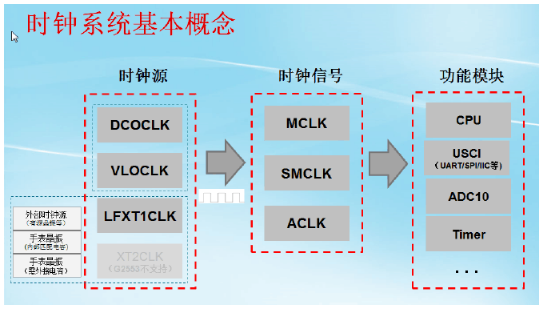

MSP430G2553单片机的时钟模块主要包括:

三个时钟:辅助时钟ACLK 、主时钟MCLK 、子系统时钟SMCLK

三个时钟源:内部低频时钟源LFXT1 、内部数字控制RC振荡器DCO、外部低频振荡器(需要焊上晶振)

对于时钟系统的配置,一共用到四个寄存器:DCOCTL-DCO控制寄存器、BCSCTL1-基本时钟控制寄存器1、BCSCTL2-基本时钟控制寄存器2、BCSCTL3-基本时钟控制寄存器3。

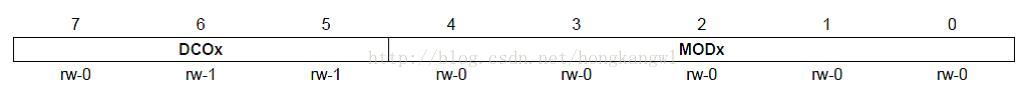

DCOCTL-DCO控制寄存器:

DCOx

DCO频率选择控制1

MODx

DCO频率校正选择,通常令MODx=0

一般不用管这个寄存器,在配置DCO时和BCSCTL2配合使用。

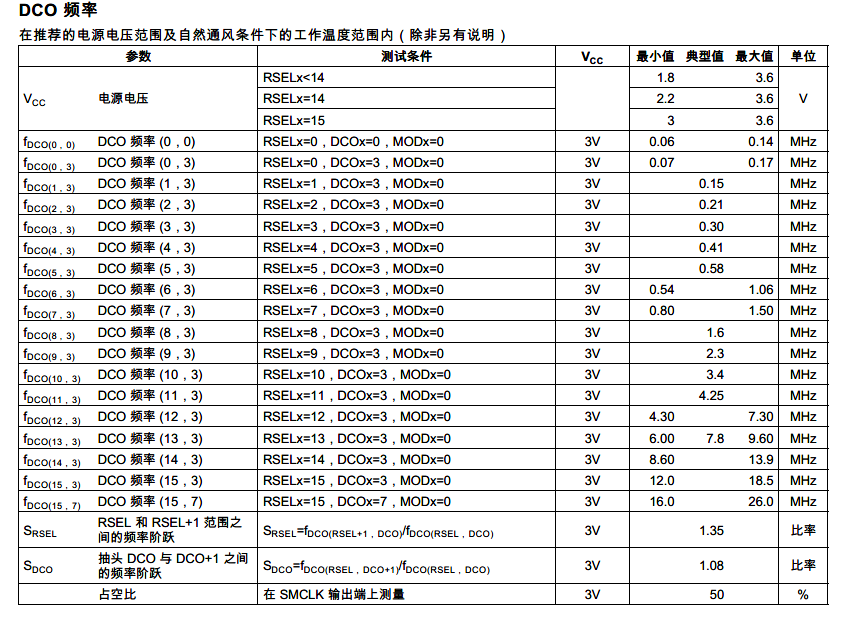

注意:在MSP430G2553上电复位后,默认RSEL=7,DCO=3,通过数据手册查得DCO频率大概在0.8~1.5MHz之间。

2、BCSCTL1-基本时钟控制寄存器1:

XT2OFF

不用管,因为MSP430G2553内部没有XT2提供的HF时钟

XTS

不用管,默认复位后的0值即可

DIVAx

设置ACLK的分频数

00 /1

01 /2

10 /4

11 /8

RSELx

DCO频率选择控制2

3、BCSCTL2-基本时钟控制寄存器2(比较常用):

SELMx

MCLK的选择控制位

00 DCOCLK

01 DCOCLK

10 LFXT1CLK或者VLOCLK

11 LFXT1CLK或者VLOCLK

DIVMx

设置MCLK的分频数

00 /1

01 /2

10 /4

11 /8

SELS

SMCLK的选择控制位

0 DCOCLK

1 LFXT1CLK或者VLOCLK

DIVSx

设置SMCLK的分频数

00 /1

01 /2

10 /4

11 /8

DCOR

DCO直流发生电阻选择,此位一般设0

0 内部电阻

1 外部电阻

4、BCSCTL3-基本时钟控制寄存器3:

XT2Sx

不用管

LFXT1Sx(当SELMx选择2或3时,通过该寄存器来选择是LFXT1还是VLOCLK)

00 LFXT1选为32.768KHz晶振

01 保留

10 VLOCLK

11 外部数字时钟源

XCAPx

LFXT1晶振谐振电容选择

00 1pF

01 6pF

10 10pF

11 12.5pF

常用宏定义:

#ifndef __DisableCalData

SFR_8BIT(CALDCO_16MHZ);

SFR_8BIT(CALBC1_16MHZ);

SFR_8BIT(CALDCO_12MHZ);

SFR_8BIT(CALBC1_12MHZ);

SFR_8BIT(CALDCO_8MHZ);

SFR_8BIT(CALBC1_8MHZ);

SFR_8BIT(CALDCO_1MHZ);

SFR_8BIT(CALBC1_1MHZ);

#endif

/*

功能:按下按键,系统主频在VLO和DCO之间切换,使用系统delay函数大概输出1hz和10hz的脉冲

*/

#include <msp430g2553.h>

volatile u8 flag=0;

void inter_init()

{

P1DIR = BIT0; // 设置P1.0为输出

P1DIR &=~ BIT3; //将按键1对应的IO口P1.3设置为输入

P1IFG &=~ BIT3; //初始化清空中断标志位

P1IE |= BIT3; //P1.3中断使能

P1IES |= BIT3; //下降沿产生中断

P1REN |= BIT3;//启用内部上下拉电阻

P1OUT |= BIT3; //P1.3设置为上拉电阻:OUT = 1; REN = 1;

__enable_interrupt();//开启总中断

}

#pragma vector = PORT1_VECTOR //固定格式,声明中断向量地址,不能变

__interrupt void Port1 (void)

{

P1IE &=~ BIT3; //关闭P1.3中断使能

P1IFG &= BIT3;//因为只用到了P1.3 ,其他的中断标志全部清零。

switch(P1IFG)

{

case BIT3: flag++;P1IFG=0;break; //P1.3 产生的中断

default: break;

}

__delay_cycles(1000);//消抖

P1IE |= BIT3; //P1.3中断使能

}

void main(void)

{

WDTCTL = WDTPW | WDTHOLD; // 关闭看门狗

IFG1 &=~OFIFG; // 晶振接触不良导致错误之后,便会使OSCFault标志位置1。这个是一个不可屏蔽中断。

//__bis_SR_register(SCG1 + SCG0); // 关闭 DCO

inter_init();

while (1)

{

if(flag%2)

{

BCSCTL2 = SELM_0 + DIVM_3; // 主频选择DCO,8分频(试试在这里用

//BCSCTL2 |= SELM_0 + DIVM_3,会发现不能切换了

DCOCTL = CALDCO_1MHZ; //DCO选择1MHZ

BCSCTL1 = CALBC1_1MHZ; //设置基础时钟寄存器1为1Mhz时钟时的设置,一般和DCOCTL一起使用

P1OUT ^= BIT0;

__delay_cycles(12500);//延时10hz

}

else{

BCSCTL3 |= LFXT1S_2; // 确定VLOC

BCSCTL2 |= SELM_3 + DIVM_3; // 选择 LFXT1CLK或者VLOCLK,8分频

P1OUT ^= BIT0;

__delay_cycles(1500);//延时1hz

}

}

}

参考文章:1.https://blog.csdn.net/blank_king/article/details/46543813 点击打开链接

2.https://blog.csdn.net/hongkangwl/article/details/16971399 点击打开链接

3.https://wenku.baidu.com/view/0088ee96d1d233d4b14e852458fb770bf78a3b6b.html 点击打开链接