在学习了jz2440的内存控制器和一些简单的内存设备之后,这一节完成了对JZ2440的SDRAM的设置,通过学习知道了JZ2440上面的SDRAM由两个32M的芯片组成64M的

1、JZ2440对SDRAM的控制

SDRAM由很多和Bank组成,每一个Bank可以看成是一张表,而每一个格子中存放一个16bit的数据,这里针对jz2440来说,那么CPU访问SDRAM的过程就可以总结为:

1、发出片选信号

2、发出Bank地址

3、 发出行地址

4、 发出列地址

这里的行列地址由内存控制器自动拆分,然后发送给SDRAM

2、SDRAM的配置

SDRAM的电路图如下

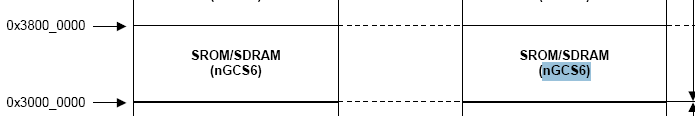

在这个图上还可以看出SDRAM使用的片选引脚为LnGCS6,查找数据手册发现如下

这个在我们之后的配置中会使用到,对应于JZ2440的Bank6,也就是SDRAM对应的Bank

接下来就对SDRAM进行配置,首先在数据手册中找到内存控制器这一章节,根据其中的寄存器我们来进行配置

BWSCON

第一个寄存器如上图,我们只使用到了Bank6,所以在这里只关心bank6的配置

[27] : 0 使用位写入的方式byte write

[26] : 0 暂不使用wait信号

[25:24] :10 每一片SDRAM芯片都是32位

BWSCON

[16:15] :11 对应SDRAM,

SDRAM只需要配置低4位

[1:0] :01 查找SDRAM的数据手册发现SDRAM的列地址为9位

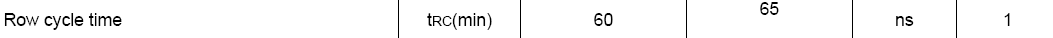

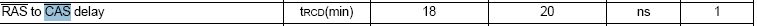

根据第2、3位需要配置的Trcd在芯片数据手册中搜索,找到该值的时间要求如上,这里取值20ns

在start.S中对JZ2440的芯片时钟进行了设置,其中FCLK为100MHZ,所以这里Trcd取2个时钟周期

[3:2]:00

REFRESH

刷新寄存器:

[23] :1自动刷新

[ 22] :0刷新模式

[ 21:20] :00 trp如上图显示,这里取2个clk

[19:18] : 01 trc取值70ns tsrc=trc-trp=70-20=50ns

[10:0] : 1269

period=64ms/8k=7.8ns=(2^11 - refresh_count+1)/100000000

refresh_count = 1269

BANKSIZE

[7] : 1 选择burst操作模式

[2:0] : 001 总共为64M的SDRAM

MRSRB6

这个寄存器其他的值均可使用默认的值,对CL进行设置,这个值表示内存控制器从SDRAM中拿到数据需要等待的时钟周期,这里选择20ns,也就是2个clk

[6:4] : 010

SDRAM牵扯到的寄存器我们就配置完成了,接下了需要调用该初始化函数并进行测试