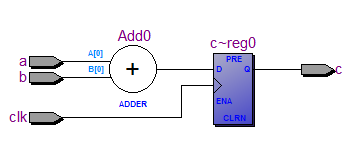

1.输出寄存器reg类型

module QQ(a,b,c,clk);

input a,b,clk;

output reg c;

always@(posedge clk) c=a+b;

endmodule

可以看到输出c有一个寄存器驱动

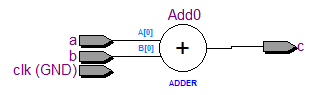

2.输出寄存器类型,但没有触发条件时,软件会自动将触发器综合掉

module QQ(a,b,c,clk);

input a,b,clk;

output reg c;

always@* c=a+b;

endmodule

3输出线型wire

(1)在always块中赋值给wire类型是不允许的

module QQ(a,b,c,clk);

input a,b,clk;

output wire c;

always@* c=a+b;

endmodule

会报错Error (10137): Verilog HDL Procedural Assignment error at QQ.v(4): object “c” on left-hand side of assignment must have a variable data type

assignment:赋值

(2)输入定义为reg类型是不允许的

module QQ(a,b,c,clk);

input reg a,b,clk;

output c;

assign c=a+b;

endmodule

报错Error (10279): Verilog HDL Port Declaration error at QQ.v(2): input port(s) cannot be declared with type “reg”

寄存器类型一般需要信号触发的,已经是输入了还怎么触发?这里quartus直接报错,不会综合掉

(3)正确写法

module QQ(a,b,c,clk);

input a,b,clk;

output c;

assign c=a+b;

endmodule

总结:

1.reg类型只能在always块中赋值,wire在assign中赋值

2.输入只能wire型,输出可wire可reg