学习摘自数字芯片实验室

这是一道笔试题

设计一个计算连续Leading Zeros个数的电路。输入8-bit,输出4-bit。 0000_1000 ->0100

0010_0010 ->0010 1000_1000 ->0000

可以parameter你的设计么?其hardware是什么样子的?

方案一:

`timescale 1ns / 1ps

module method1(

input[7:0] din ,

inputclk ,

inputrst_n ,

outputreg [4:0] dout

);

always@(posedgeclk or negedge rst_n) begin

if(!rst_n)begin

dout<= 0 ;

end

elsebegin

if(din[7])dout <= 0;

elseif(din[6]) dout <= 1;

elseif(din[5]) dout <= 2;

elseif(din[4]) dout <= 3;

elseif(din[3]) dout <= 4;

elseif(din[2]) dout <= 5;

elseif(din[1]) dout <= 6;

elseif(din[0]) dout <= 7;

else dout <= 8;

end

end

endmodule

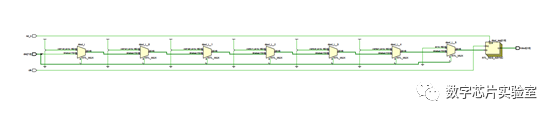

可以发现上述代码使用了7级MUX级联,可以在单周期内完成运算。但是,不易参数化。

方案二:

`timescale 1ns / 1ps

module method1#(

parameter N = 8,

parameter M = 4

)(

input[N-1:0] din ,

inputclk ,

inputrst_n ,

outputreg [M-1:0] dout

);

reg [N-1:0] dout_1;

reg [M-1:0] dout_2 [N-1:0];

genvar i ;

generate

for(i=0;i<N;i=i+1) begin

always@(*) begin

dout_1[i]=(din[N-1:N-1-i]==1'b0)?1'b1:1'b0;

dout_2[i] = (i==0)?dout_1[i]:dout_1[i]+ dout_2[i-1];

end

end

endgenerate

always@(posedgeclk or negedge rst_n) begin

if(!rst_n)begin

dout<= 0 ;

end

else begin

dout <= dout_2[N-1];

end

end

endmodule

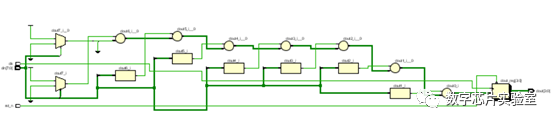

该代码实现了参数化的需求。使用了7级异或级联,可以在单周期内完成运算。

方案三:

这个就不cooooding 了

首先并行转串行,使用FSM在多个周期实现上述功能,可以达到更高的工作频率,但是每次处理延迟在1~N周期之间。

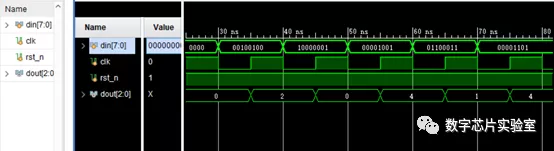

最后Testbench如下:

`timescale 1ns / 1ps

module method_tb;

reg [7:0] din ;

reg clk;

reg rst_n;

wire [3:0] dout;

initial begin

clk = 0 ;

rst_n = 1 ;

din = 0 ;

#12 ;

rst_n = 0 ;

#12 ;

rst_n = 1 ;

repeat(5) begin

@(negedge clk) ;

din =$random%256 ;

end

end

always #5 clk = ~clk ;

method1 method1(

.din(din) ,

.clk(clk) ,

.rst_n(rst_n) ,

.dout(dout)

);

endmodule