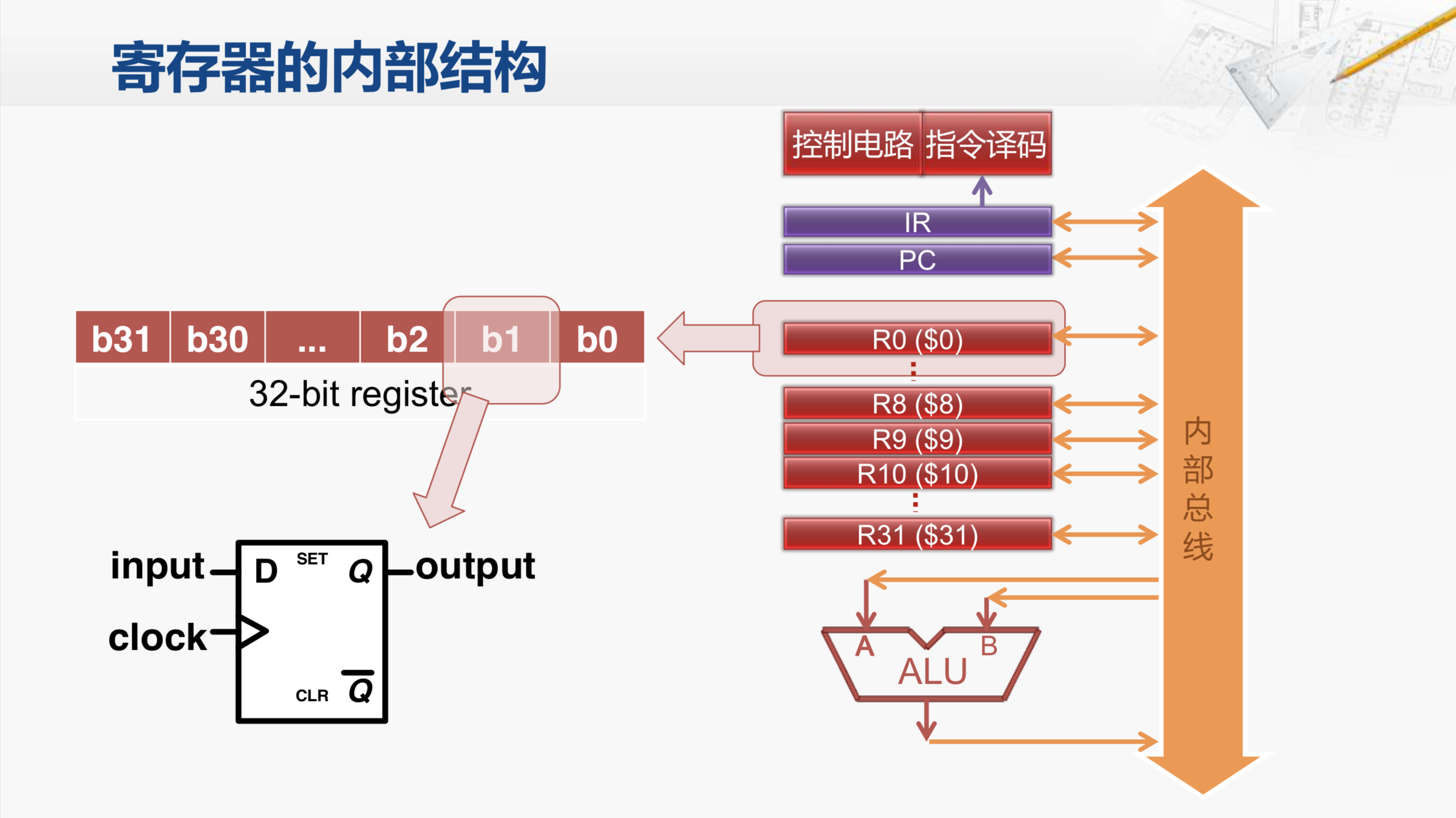

CPU中有很多的寄存器,有临时保存数据的通用寄存器,也有专门保存指令编码或者指令地址的寄存器。它们都有存储信息的能力。 那在这一节,我们就来分析这些寄存器是如何实现的。

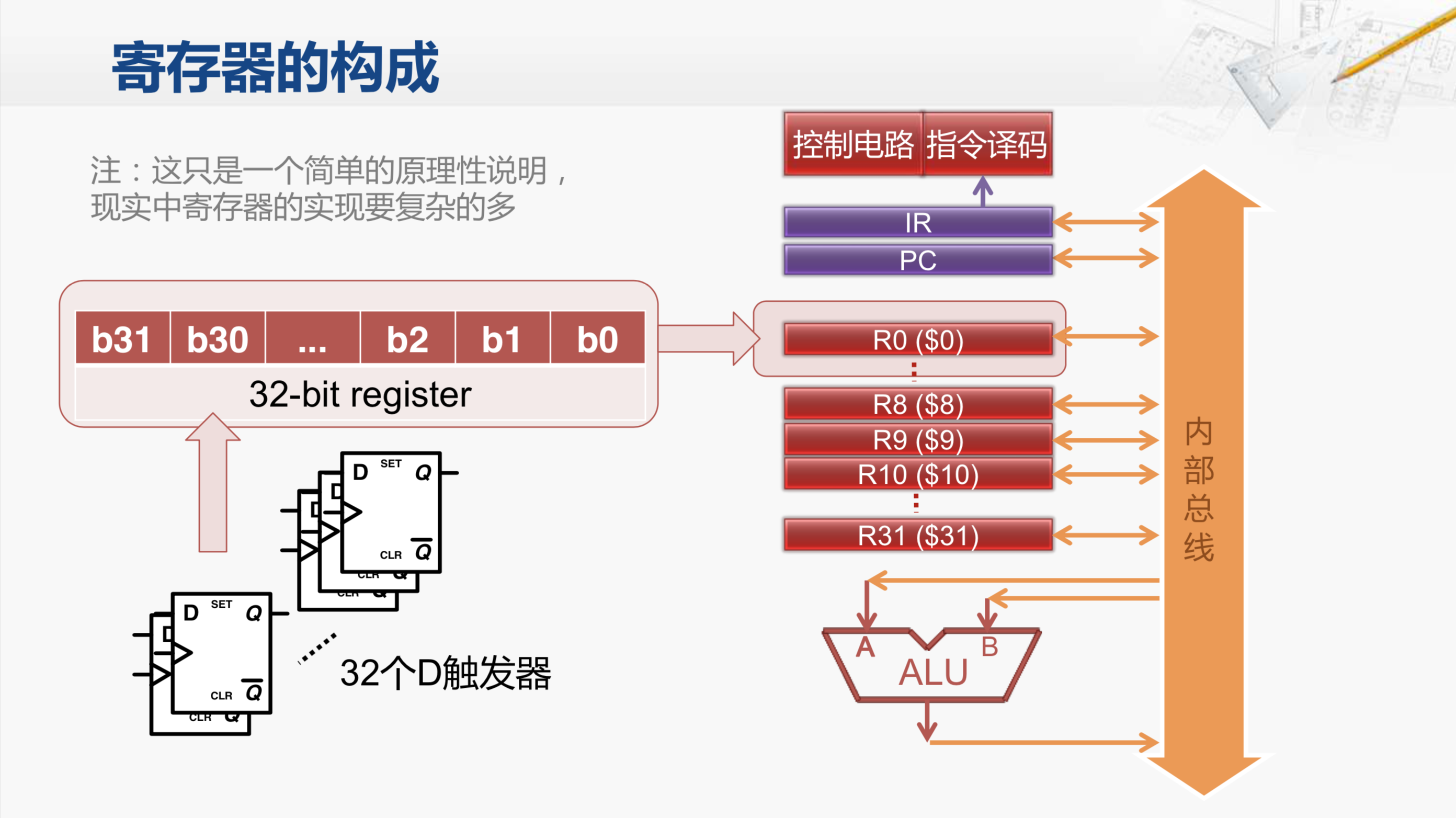

在CPU当中用来存放信息的非常重要的部件就是通用寄存器。比如说零号通用寄存器,在mips的体系结构中,它就是一个32位的寄存器,从电路实现上来说这32个比特都是同样的。

我们来看其中一个,它就可以用左下这样一个结构来实现。这个结构就是我们将要介绍的D触发器。

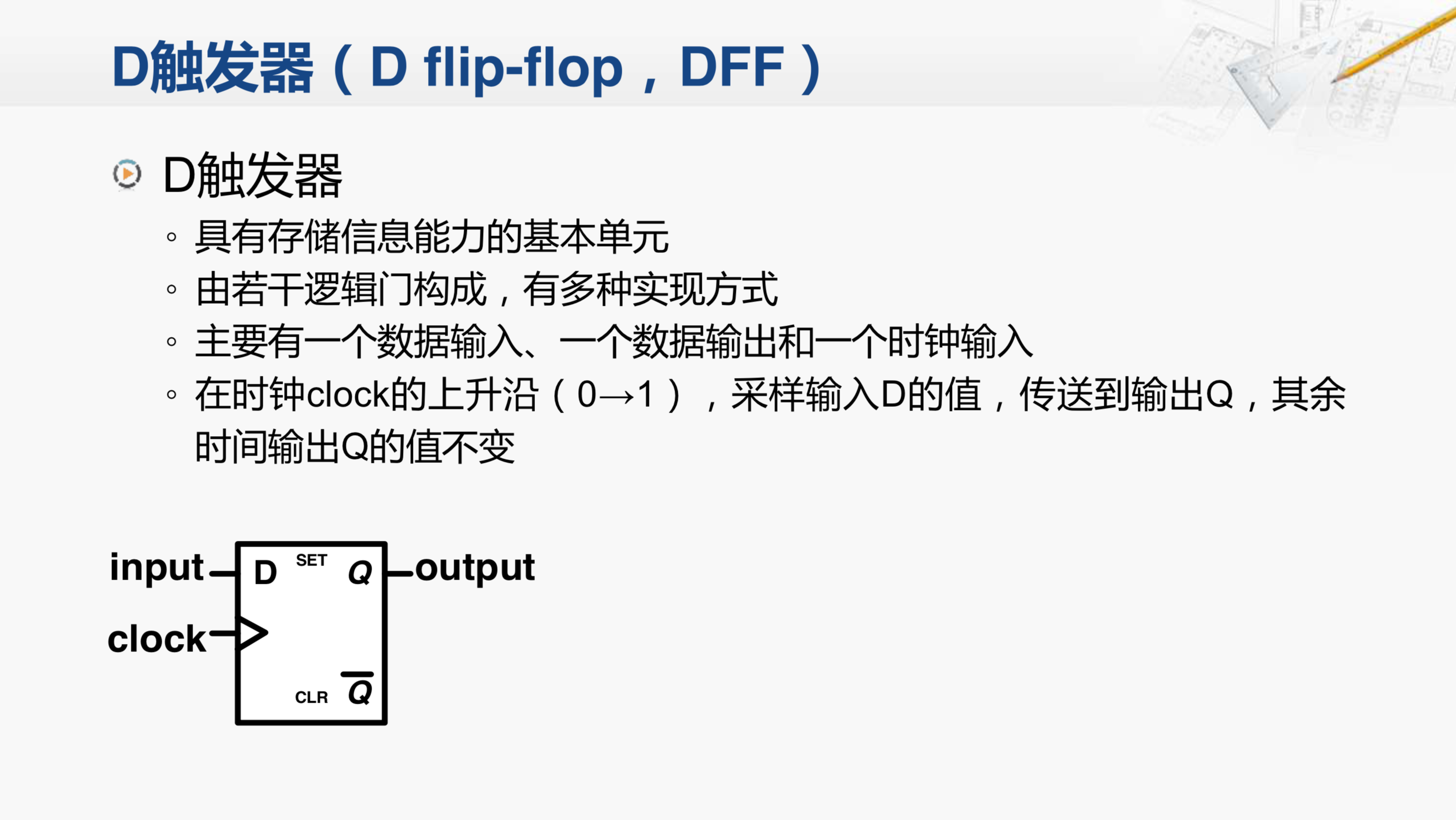

触发器是具有存储信息能力的基本单元,它有很多种类型,D触发器是其中一种。

其实触发器也没有那么神秘,它也是由与或非这样的逻辑门构成的。

仅就D触发器而言,以后有很多的实现方式,在这里我们就不深入到它的内部实现细节,而重点关注它对外提供的功能。这个D触发器主要有这三个接口,一个数据输入,一个数据输出和一个时钟输入。

它的功能表现是这样的,在时钟clock的上升沿,也就是clock从低电平变为高电平,也可以说是从0变到1的时候,这是一个很短的时间,在这时D触发器会采样输入端口D的值,经过一段很短的时间会将这个值传送到输出端口Q。在其它的时候也就是不在时钟信号的上升沿的时候,无论输入端口D如何变化,其输出端口Q的值都是保持不变的。

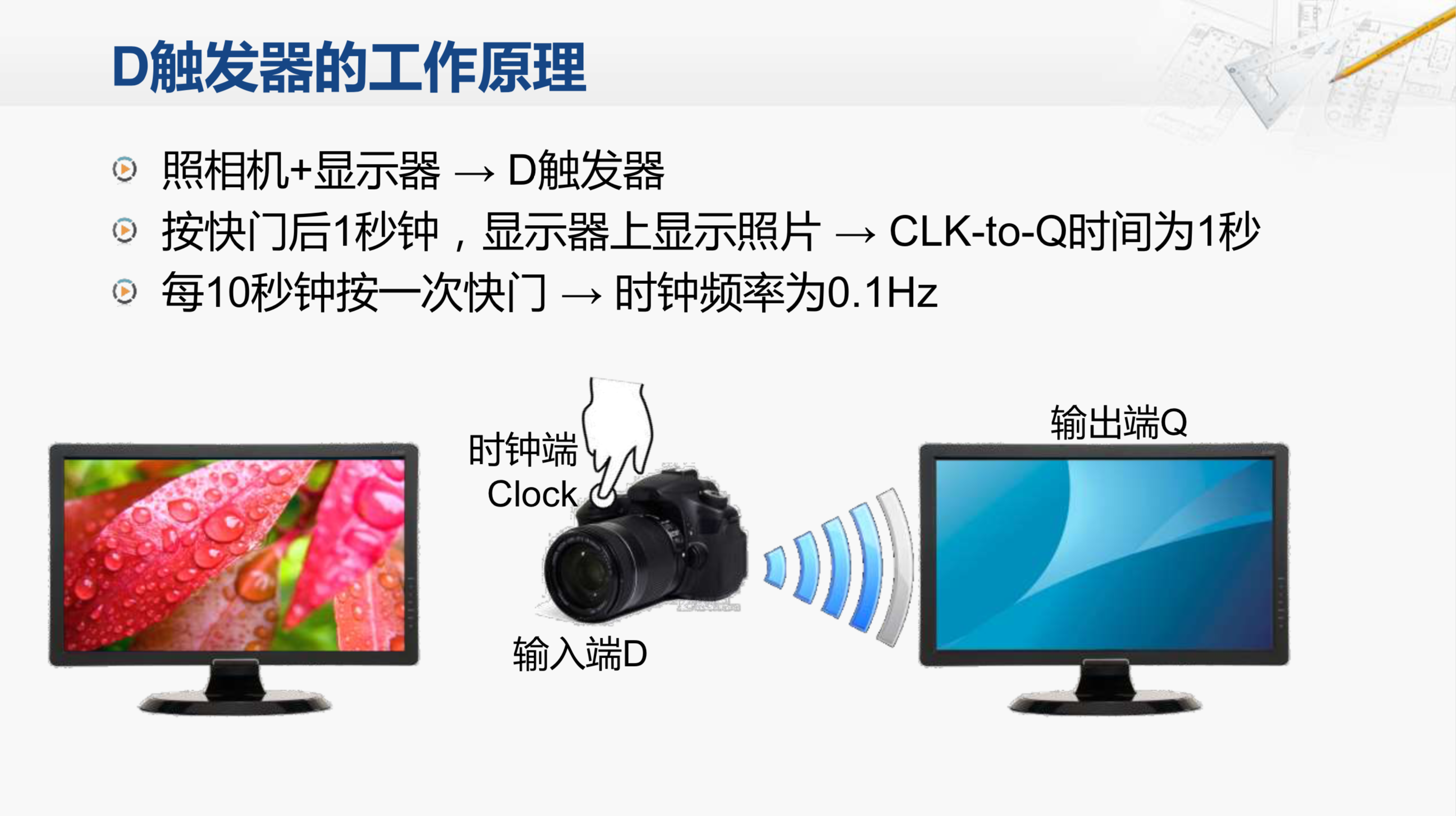

当然这样说起来还是很抽象,我们通过一个形象化的描述来做进一步的说明。

就好比我们平常使用的照相机,我们把镜头比作D触发器的输入端D,拍照的快门比作时钟端clock。这台相机内部带有无线传输的模块,可以将其拍摄的照片传送到一个显示器上,这个显示器就好比D触发器的输出端Q,那这样我们就把D触发器比作这个照相机和这个显示器。当按下照相机的快门后,照相机会拍一张照片,过一秒钟后显示器上显示出这张照片,对于D触发器来说,这就叫做 clock-to-Q 的时间,也就是从时钟的上升沿到来开始直到数据出现在输出端为止,这个时间是属于D触发器自身的特性。那对于这个D触发器所在的整个芯片还有一个重要的特性就是时钟频率,在这里就好比我们约定每十秒钟会来按一次快门,那这个系统的时钟频率就是零点一赫兹。

最后我们再给这一套由相机和显示器构成的D触发器加上一个输入也就是另一台显示器,这样就会拍摄左边这台显示器上的画面, 并将它显示在右边这台显示器上。

那好,现在我们就假设十秒钟到了,我们会按动一次快门,按动快门后照相机会拍摄下左边这台显示器上的画面,并在一秒钟后将拍摄的照片传送到右边这台显示器上,这个过程就体现了在时钟的上升沿D触发器采用输入端的信号,并在时钟上升沿之后 clock-to-Q 的时间,将采样的信号从输出端口送出来,那之后输入端也就是左边这台显示器上的画面可能会发生变化,但是只要不按动快门,右边显示器上的内容是不会发生变化的。也就是在下一个时钟上升沿来临之前无论输入怎么变化,输出都不会发生变化。

现在假设十秒钟又到了,我们要按动一次快门。需要注意的是就和现实中的照相一样,在按动快门的前后很短的时间内通过镜头看到的画面不应该发生变动,否则就可能造成拍出的照片是模糊的。对于D触发器来说,在时钟上升沿前后很短的时间内,输入端的信号也不能发生变化,否则就可能造成无法正确的采样。那么这也是D触发器的一个重要的特性,要求输入信号在时钟上升沿之前有一段很短的稳定时间,很短的稳定时间称为Setup时间,在时钟上升沿之后也需要有一段很短的稳定时间,称为hold时间。

好我们假设在这一次按动快门时左边显示器上的画面是稳定的,

现在我们来按动快门,再过一秒钟,这次采样的信号就被送到了输出端。这就是一个D触发器简单的工作原理。

我们再来看一看两个D触发器相连的情况,左边这个A相机就是第一个触发器,它的输出连到了右边这个B相机的输入,我们还是用同样的约定,每隔十秒钟来按动一次快门,那当十秒钟到了的时候,这两台相机的快门会被同时按动。

一秒钟后,它们的输出画面都发生了改变。但我们要注意的是A相机拍摄下来的这个绿叶是经过了clock-to-Q时间才传送到了它的输出。而在此之前B相机已经拍摄到了A相机此前的输出,也就是现在显示在最右边的显示器上的这个红色的叶子。所以我们要注意的是这两个相连的相机虽然是同时按动了快门,但并不意味着最左边的画面(绿色叶子)会一直传递到最右边的显示器上,而是将左边的相机之前存储的画面(红色叶子)依次向右传递。那么在一个复杂的系统中是有很多的D触发器用各种不同的方式相连,这样就可以在不同的触发器中存放不同的信息,并且可以在时钟的控制下进行传递,而同样在时钟上升沿没有到来的时候,无论输入发生什么样的变化都不会影响到后面触发器的输出。

通过这个例子,我们应该对D触发器的行为有了更加深入的了解。我们再来看这些解释的时候应该不会觉得那么的陌生。

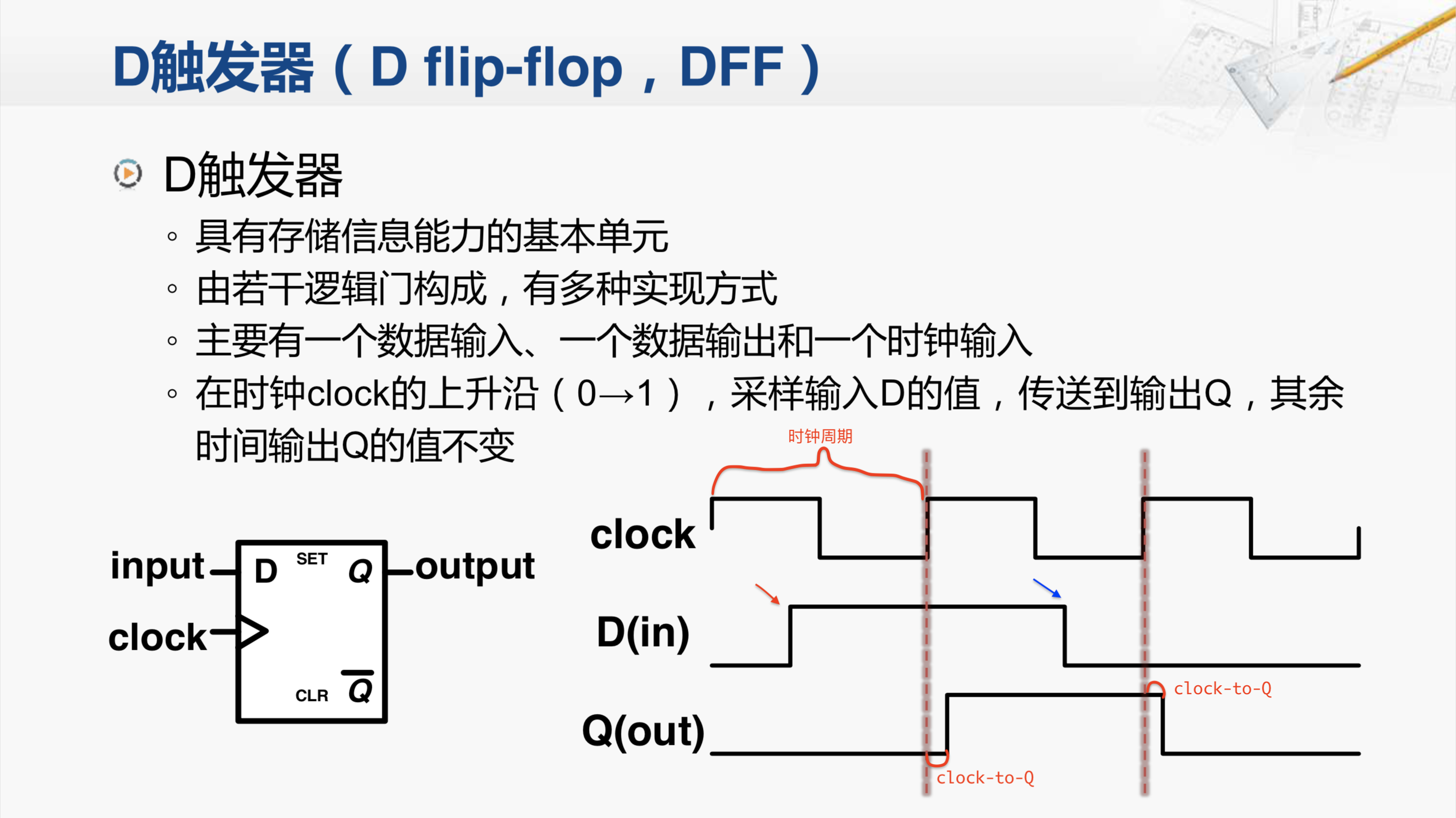

我把刚才说的这个过程用一个时序图的方式表达出来。

第一行是时钟信号,它是有规律的进行变化,两个上升沿之间的间隔时间就称为时钟周期。

输入信号D则可能在任何时候发生变化。比如在这个时候(红色箭头)它由0变到了1,但是因为时钟上升沿没有到来,所以输出端Q并没有发生变化。直到时钟上升沿到来的时候(图中第一条红色虚线),D触发器会采样输入端的信号,并经过很短的clock-to-Q的时间在输出端体现出来,因为这时候输入端D(in)是1,所以输出端D(out)也变成了1。然后时间再继续,在这个时钟周期内,输入D(in)又发生了变化(蓝色箭头),由1变成了0,但是同样输出端Q(out)没有发生变化,直到下一个时钟上升沿到来,采样到了新的输入端的指令,再经过Clock-to-Q输出端也变成了0,这就是一个D触发器的基本工作行为。

那我们如果把很多个D触发器组合起来,比如就是这32个D触发器,那就可以构成一个32位的寄存器,当然这只是一个很简单的原理性实现。用这样一个32位的寄存器就可以做成CPU当中的一个通用寄存器,用同样的方法可以作出其它的通用寄存器以及PC,IR 这样的寄存器,再将这些寄存器与由逻辑门构成的电路相连, 就构成了我们这个复杂的CPU了。

现在我们对寄存器的工作原理有了一个基本的了解,我们也对寄存电路是如何运行的有一点点非常浅显的认识。如果你还想了解更多就需要去学习其它的专门课程了。