论述"Cache-主存"层次,我们首要考虑一下四个问题:

(1)当把一个块(页)调入到高一层(靠近CPU)存储器时,可以放到哪些位置上?(映像规则)

(2)块的标志,如果一个块在较高层中,如何找到它?(查找算法)

(3)块的替换,如果块发生缺失,哪个块被替换?(替换算法)

(4)写时策略.写操作时会发生什么?(写策略)

一个块可以被放置到cache的什么地方?

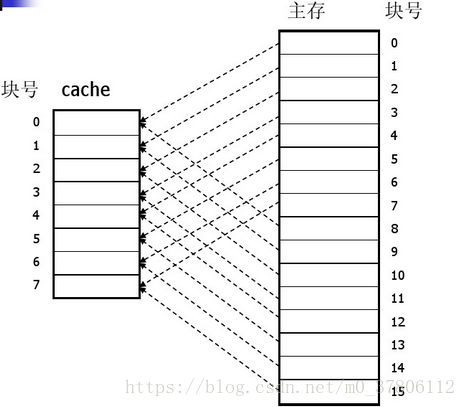

直接映射:(块地址)MOD(cache中的块数),每个块只能出现在唯一位置上,如下图所示

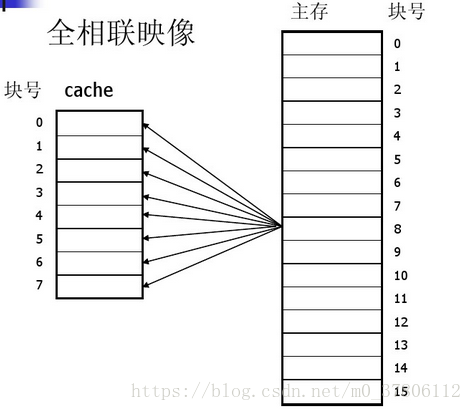

全相连映射:一个块可以放置在cache中的任意位置上,如下图所示:

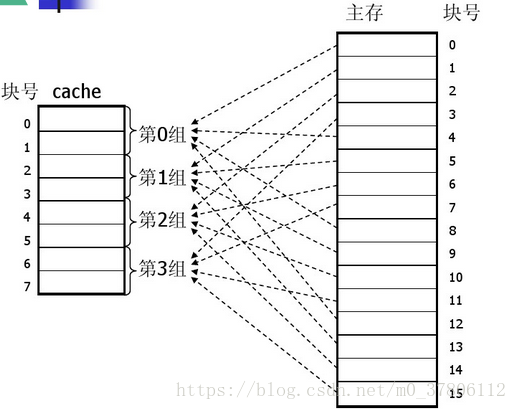

组相连:(块地址)MOD(cache的组数), 一个块首先被映射到一个组中,然后它可以被放置在组中的任何一个块中,如下图所示

直接映射,全相连与组相连的关系:

直接映射是一个简单的1路组相联

一个有m块的全相联cache可以称为m路组相联

大多数处理器的cache采用直接映射,2路组相联或是4路组相联.

如果一个块在cache中,如何找到它?

这是通过查找目录表来实现的。Cache中设有一个目录表,每一个Cache块在该表中都有唯一的一项,用于指出当前该块中存放的信息是哪个主存块的。

块地址:块结构中有一个地址标志给出块地址,对每一个块标志进行检查,看其是否与来自处理器的块地址相匹配.考虑到速率,采用并行检查.

有效位:确定块中是否包含有效信息.

cache地址:块地址与块偏移

块地址:标志字段和索引字段

块内偏移是从块中选取数据,索引字段用来选择组,再通过比较标志字段来判断是否命中,标志字段是检查所有的块,全相联没有索引字段.

并行查找的实现方法:

- 相联存储器

- 单体多字存储器的比较器

如果cache缺失,哪个块将被替换?

直接映射:直接替换不命中的块

在组相联与全相联中需要在多块中进行选择,主要的替换算法主要有如下四种:

(1) 随机替换,产生伪随机数块号

(2)LRU,记录块的访问次数,替换长时间没有被访问的

(3)FIFO,最早进入cache的块被替换

(4)OPT,优化算法

写操作时会发生什么?

读操作在 cache的访问占大多数.所有的指令都是通过读操作来获得的,而且大部分的指令是不需要进行存储器写操作的。

块可以在标志位读和比较的同时被读出,读块操作与获得块地址的同时就开始了.如果读命中,块中所需要的信息立刻被传送到处理器,如果发生读取失,只需要将读到的信息丢失即可.

而对于写操作来说,这样做并不适合,只有在标志位有效而且地址命中时,块才能修改。检查标志位不能与写操作同时进行

写操作比读操作花费时间更长.

处理器必须给出写数据的大小,通常在1~8个字节之间,块中只有这个部分的数据能被更改.但是读数据可以读取比所需字节数更多的信息.

cache写策略:

写直达:信息被同时写到cache块和更低一层存储器中

写回法:信息只被写到cache块,只有cache中的该块被替换出去时,信息才会被写回主存中.

重写脏位:

一个块是脏的(在cache中被修改过)

干净的(在cache中没有被修改),如果是干净的,则在下层存储器中与cache包含的信息相同,因此不必被写回.

优点:

写回法:写操作与cache存储器的速度是一致的,而且对于同一块的多次操作仅需要对下一层存储器进行一次操作。

写回法:写操作与cache存储器的速度是一致的,而且对于同一块的多次操作仅需要对下一层存储器进行一次操作。

写回法需要较小的存储器带宽,对于其他层次的存储器与存储总线的使用较少,节省了功耗,适用于嵌入式应用程序.

写直达法:cache总是干净的,当发生读缺失的时候,无需对下一层存储器进行写操作(相对于写回法)

下一级存储有最新的当前数据副本,简化了数据一致性,数据一致性对于处理器和IO均很重要.

我们需要利用写回法来减少访问存储器的通信量,有希望通过写直达法来保证存储器层次结构中cache和低层存储器的数据一致性.

在写直达法中:

处理器的操作必须等待写操作完成,此时处理器称为写停顿,减少写停顿的策略是写缓存技术,允许处理器把数据写入到缓冲区之后立即继续工作.

处理器的操作必须等待写操作完成,此时处理器称为写停顿,减少写停顿的策略是写缓存技术,允许处理器把数据写入到缓冲区之后立即继续工作.

写缺失策略:

写分配:写缺失发生时,内存的块被读到cache中,然后执行上个写命中时的操作

不按写分配:写缺失发生时,仅修改低层存储器的该块,而不将该块取到cache中