1、制作原理图一般使用Orcad组件中的capture CIS,Orcad Capture CIS是Prcad组件中功能最强大的一个原理图制作工具。

2、布线时网络变压器下面做一块死铜皮,网络变压器下面最好不要有走线。

3、原理图网表输出:Tools -> Create Netlist,更改放置网表的路径后输出即可。

4、开始画PCB之前的准备:新建PCB文件、网表导入、快捷键设置、鼠标右键快捷键、设置叠层、设置线宽约束。

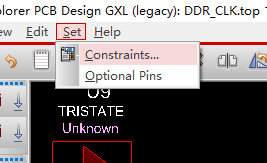

5、画PCB的时候选择ALLEGRO PCB中的ALLEGRO PCB Design GXL(legacy)组件。

6、新建完PCB文件之后,要先设置元件封装库的路径:Setup -> User Perferences,在这个里面设置封装的路径以及封装所用的pad的路径,选择Paths -> Library,在这里面需要设置两项:padpath和psmpath,这两项的路径都设置为元件封装所在的路径。

7、网表导入:File -> Import -> Logic,在Import logic type下面选择Design entry CIS(Capture),在最下面选择存放网表的路径,然后点击右上角的Import Cadence按钮开始导入。

8、网表导入成功之后设置板层叠层:Setup -> Cross-section,

按照如下表格来设置叠层:

设置叠层的类型:

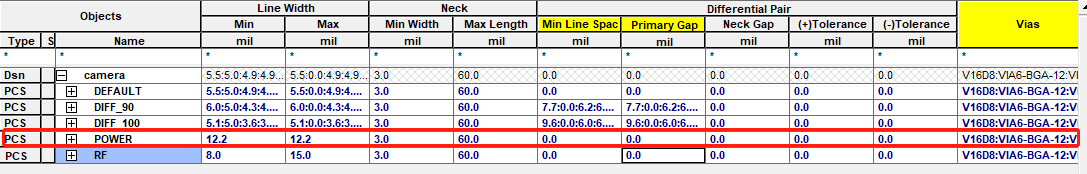

9、根据阻抗表设置布线规则约束:Setup->Constraints->physical,在这里进行线宽的设置:

注意:上图中设置的单端走线的线宽,不含差分走线。

下面是添加过孔:

新建并设置差分对布线规则约束:

创建并设置共面和隔层(即射频)约束:

另外还有可能在信号平面走电源线,因此需要设置一个电源线的规则:

设置线到线以及线到焊盘、铜皮、孔的间距:

10、设置画PCB时常用的一些快捷方式:

鼠标右击的快捷方式设置:Tools->Utilities->Stroke Editor

快捷方式设置好之后,需要把启用鼠标右击快捷方式的开关打开:Setup->User preference->Ui->Input中,no_dragpopup后面的框勾选上:

键盘快捷方式设置:

需要把env文件放在pcbenv文件下面,正常情况下这个pcbenv文件夹是位于安装目录下的SPB_Data文件夹下的,如图:

但是在我的安装目录Cadence下面并没有SPB_Data这个文件夹,在整个电脑中全局搜索也没有找到这个文件夹。当时就认为是我安装的有问题,之前本来是安装好SPB16.6的,然后又使用吴川斌博客中阿里狗自动安装了sigrity软件,在播放购买的加密视频的时候是不能打开allegro软件的,当时不知道,还以为我之前安装的allegro有问题,就又卸载了,然后使用阿里狗重新安装了一下,我以为是这个阿里狗安装问题呢。然后就把sigrity和SPB16.6全部卸载了,按照普通的方法自己安装和破解了一次SPB16.6,安装完成之后还是没有SPB_Data/pcbenv/这个文件路径,在电脑上全局搜索也没搜出来。然后百度中发现:

于是我查看电脑环境变量中的HOME指向的路径是:C:\Users\SIGMA\AppData\Roaming\SPB_Data\pcbenv

既然是有的,为什么全局搜索的时候没有搜索出来呢,是因为这个AppData文件夹是个隐藏的文件夹:

现在原因找到了,就是这个HOME变量指向的路径不对,于是干脆再卸载了,使用吴川斌博客中的阿里狗再安装一次,这次安装完成之后,首先查看在Cadence目录下面有了这个SPB_Data的文件夹,但是打开看里面是空的,于是去查看HOME的环境变量:

说明这个环境变量指向的路径没有问题,说明阿里狗在破解的时候已经把环境变量修改了,那么为什么这个文件夹是空的呢?

是不是需要先打开一下allegro软件之后,里面才会有一些东西?尝试一下,确实是。

于是将env文件放在SPB_Data/pcbenv文件夹下,测试发现快捷键可以使用了。

11、如果在测距的时候只是显示mil可以通过设置使其同时显示mil和mm:

Setup->User Preferences->Element:

测距效果:

12、有时会出现旋转快捷键不可用的情况,解决参考链接:https://jingyan.baidu.com/article/fec7a1e5cba21f1191b4e773.html

13、Skill对齐工具。

14、PCB层叠颜色设置:Display->Color/Visibility->Stack-Up

15、设置在PCB中只显示我们需要的颜色,在命令框中输入color,弹出旧版的颜色设置命令框,通过Display->Color/Visibility打开的颜色设置对话框是新版的。

注意:需要将上图中的Place_Bound_Bottom也要选中。这个place bound相当于元器件的封装外边框(元件大小)。

16、导入PCB板框:File->import->dxf

17、设置禁止放置器件区,导入进来的边框是放在Package Geometry层上的,这一层相当于PCB的外边框。我们的禁止放置器件区是放置在Package Keepout层上,当然放置的时候需要选择是放置在顶层还是底层,还是两层都需要。

18、放置螺丝孔:让PCB处于放置元器件的界面:

然后去原理图上依次点击需要放置的螺丝孔,比如要放置3个,就依次把这3个点击一下,然后回到PCB,在PCB上依次点击3下,就把这3个螺丝孔放到PCB上了。

然后去原理图上依次点击需要放置的螺丝孔,比如要放置3个,就依次把这3个点击一下,然后回到PCB,在PCB上依次点击3下,就把这3个螺丝孔放到PCB上了。

19、将螺丝孔放到PCB板框的对应位置,使用吸附功能:首先按下键盘上的快捷键m,进入移动器件的模式,点击某个螺丝孔封装后,这个封装就会随着鼠标移动,然后移动到对应的位置,在放置螺丝的那个圆上面右击->Snap pick to ->Arc/Circle Center.

20、结构件(螺丝孔、要放在固定位置的元器件等)放置完以后,要将其锁定,防止后续的误操作将其移动了位置:

21、电路板倒圆角。

直接从cad倒过来的板框是一个shap,shape是不能倒圆角的,要先将其打散:

执行:Shape->Decompose Shape

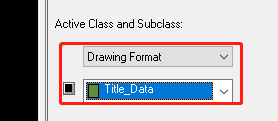

接下来设置打散之后的线归属于哪个层:

然后选中要打散的shape。这样shape就打散成功了,将原来的shape删除掉。

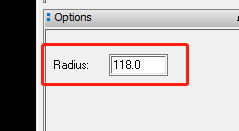

开始倒圆角操作:Manufacture->Drafting->Fillet

设置倒圆角的直径,一般为3mm,118mil

然后依次单击相交的两条边即可导出圆角。

圆角导完之后将打散的板框再组合为一个shape:

执行:Shapes->Compose Shapes

选择组合之后的shape放在哪一层

然后依次选择哪些打散的线,也可能选一条线之后系统就自动把封闭图形选上了。

最后将打散的线再删除掉。

22、器件导入:

方法:首先在pcb板框旁边建一个网格,将PCB元器件放在网格中间,每一个格点放置一个功能,根据原理图中的页来设置网格的行数,根据每一页中的功能数量来设置网格的列数。

随便选出一个来画网格的层:

大概按照一行5个功能区的话,需要画一条长5000mil的线。键盘快捷键e画没有电器属性的走线,在命令行中输入ix 5000是长度为5000mil。

注意:在复制之前不能有东西处于选中状态,一定要运行了复制命令之后再去选择要复制的元件,否则不能修改要复制出的数量。

在change状态下,右击可以cut断一条线。

建好的网格:

接下来将器件导入到对应的网格

查看器件是否已经完全导入:Display->Status

接下来查看一下总共有多少个pin:Tools->Quick Reports->Summary Drawing Report

2000个左右的pin大概需要6天把PCB做完。

23、合成Groups:可以对整个group进行操作,也可以单独对group里面的器件进行操作,对后面的模块化布局很有用。

这个功能类似于AD中将器件合成一个模块

首先进入布局模式:

然后把需要group的器件全部选中,右击->add to group,会弹出给group命名的对话框,命一个名字,确认即可。这个命名对后续操作没什么影响,后续也不会用到这个命名,因此可以随便命名。

24、设置PCB的自动保存功能:Setup->User Preferences

25、注意,已锁定的部件是不能删除的,必须要先将其解锁之后才可以进行删除。

26、布局及布线:

(1)注意布局的时候DCDC尽可能布在一起,保证其背面有一块完整的铜皮,其它信号走线尽可能不要靠近DCDC,因为DCDC中都有电感,而电感对信号的影响较大。

(2)DDR可能会影响电路板上射频信号,估算方法为看DDR的速度,然后乘以3,看看成完之后的频率是否会落在射频的受影响频率范围内,或者接近这个范围。如果有可能影响到射频,那么就需要在DDR上面加一个屏蔽罩。

(3)对于DCDC中的反馈线,如果空间允许的话,最好将其做一个包地处理。

(4)产看某个网络链接情况:

(5)通过点击原理图中的元件将PCB中的某些元件高亮:

首先在PCB中执行高亮的命令(或者改变颜色的命令),然后在PCB左侧选中symbols,然后切换到原理图,依次单机需要高亮的元件,点击完回到PCB,发现已点击的元件被高亮了。

(6)BGA封装的器件要在其某一边上留出3mm或者5mm的空间不能放置元器件,考虑返修使用。

(7)考虑到测试夹具的制作,最好把测试点放在PCB的一侧,集中放置。

(8)架筋加屏蔽罩的方式,架筋1mm的宽度,架筋左右两边的器件离架筋0.4mm。

(9)DDR的拓扑方式有T拓扑和FLY-BY拓扑,两颗DDR的话,两个拓扑方式相差无几,T拓扑在时序控制上更有优势,FLY-BY拓扑在布局上面更有优势,它能使用一个更小的布局空间,大概可以节省25%的布线密度。如果DDR颗粒的数量大于2片的话推荐使用FLY-BY。在使用FLY-BY拓扑之前要先确认DDR是否支持时序补偿,如果支持的话才可以使用FLY-BY。FLY-BY拓扑经验值,两个DDR颗粒之间的距离5mm(最近的两个pin之间的距离,不是元件体)比较方便走线,无论正反贴还是大于两个。DDR颗粒和主控芯片的距离推荐大于8mm(最近的两个pin之间的距离,不是元件体)。

(10)注意原理图中引脚的属性如果是power,那么默认名称相同的引脚会链接到一起。在原理图上修改某个元件的某个引脚的属性:首先选中该元件,右击->Edit Part,然后在弹出的窗口中选中需要修改的引脚,右击->Edit Properties...

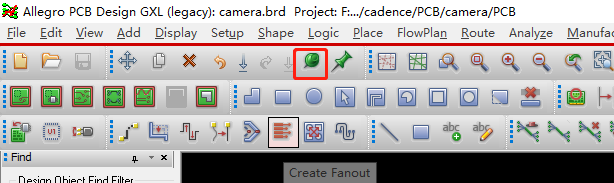

(11)fanout可以将BGA的孔全部扇出:Route->Create Fanout

注意,过孔的大小要视BGA引脚的间距而定。

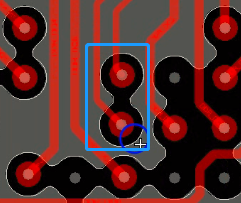

BGA扇出后不容易看出哪个是焊盘,哪个是扇出的孔:

需要设置一下,Setup->Design Parameters

设置完成以后,就能分清楚哪个是BGA的焊盘,哪个是扇出的过孔:

(12)设置区域规则,执行命令Setup->Constraints->Physical

新建的区域规则命名为BGA,设置最小和最大线宽:

设置区域规则的间距:

在PCB上面添加区域规则:

(13)走DDR的地址和时钟线的时候可能需要两个层走线,那么尽量让两个层走线数量想当,这样绕等长的时候好绕一些。

(14)串扰耦合度在工程上一般控制在5%左右,allegro17.2中耦合度查询工具已经从sigrity的power SI放到了allegro中,可以在allegro中直接查询串扰耦合度。

(15)ALLegro中内层无盘过孔的设置:Setup->Unused Pads Suppression

点击Close后可能弹出一个警告的对话框,点击确定即可。

在ALLEGRO中关于无盘工艺还需要设置一个地方,否则走线从过孔上经过,不会报DRC错误:Setup->Constraints->Modes

内层无盘工艺的优势:增大走线之间的安全间隙,增大布线的空间。

(16)设置差分对:执行命令Setup->Constraints->Physical

选中需要设置差分对的两个网络,右击->Create->Differential Pair

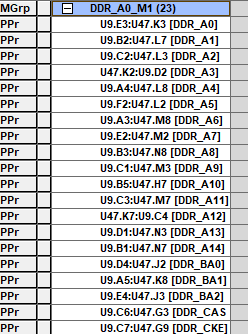

(17)将DDR的信号线做一个分组:

右击->Create->Net Group

(18)DDR地址信号中的复位信号不用等长,可以从地址信号分组中移开。地址信号线(DDR中除了数据线之外的所有线)中可以细分为地址信号和控制信号,控制信号线的等长要求没有地址信号线那么严格,地址信号线的等长要求又没有数据信号线那么严格,即数据信号等长要求最严格,地址信号次之,控制信号再次之。

(19)将设置好的差分对赋予差分100的规格(差分的阻抗):

(20)设置3W规则:

(21)将设置好的3W规则赋予给DDR网络:

(22)设置相对传播延迟:

合成对应的Match Group

(23)计算线长

(24)调整差分走线,规则设置完毕,回到PCB,将差分线change到对应的宽度,然后调整位置,调整的时候如果想只是调整单根走线,可以在修线状态下,单机某条线使其处于移动状态,右击->Single trace mode,这样就可以移动单条线,再单机一下跳出移动单条线的模式。

(25)走线绕等长的时候,如果走线有跨层(过孔),需要把过孔的长度考虑进去,跨越的层数不一样,过孔的长度也不一样。

执行Setup->Contraints->Modes

(26)设置地址走线的规则,因为是FLY-BY拓扑,所以设置规则相对会复杂一些,Setup->Constraints->Physical

【注意,一定要将这个删掉。第一次设置完这个地址走线规则后,拉等长的时候发现不对,右下角不出现绿色的等长区间,检查规则发现这个group没有删掉,将其删掉之后就正常了】

会弹出一个简单的仿真界面,当然这里的仿真不如Sigrity,如下:

执行上图中的Set->Constraints

【注意,这个截图是分两次截的,名称可能不对应】

弹出的警告选择“是”

将上面设置的规则适用于所有的地址线(除了那个差分对)

然后单独设置那个差分对的规则:

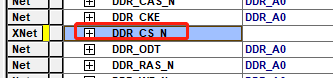

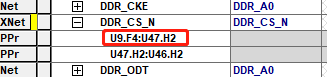

(27)设置无源器件,串阻的XNet:

这里有一个22Ω的串联电阻,位号是R48,要先把它设置一下

点击OK后,在弹出的对话框中找到电阻R48:

然后点击Auto Setup,让系统自动从已有模型中匹配模型:

如果系统中匹配不到,可以自己创建一个模型,点击Create Model

在弹出对话框中:

这样就创建完成了。

设置成功之后,回到PCB就能看到XNet

(28)回到规则管理器,继续设置规则:

如下图,DDR地址线的拓扑规则DDR_A0对于更改为XNet的网络已经不再适用了。

所以要将这个网络的规则更改一下,

在这里右击->SigXplorer,弹出这个网络的模型:

设置方法和上面相同:

然后更新到规则管理器:

将下面这一段

添加到这段中,都是U9到U47的

添加方法:

另一个需要添加到M1中,M1中是从U47传输到U46的

(29)接下来再去设置时钟,即那个差分对:

打开差分对模型:

这个R47是放在末端的一个端接电阻,可以忽略不计

至此,地址线需要等长的设置完毕,如下图,从U9到U47共26条线,从U47到U46共26条线。

方便看网络线长,可以做个分析模型设置:

就会显示出长度信息:

这些地方需要修整一下:

整理后:

下面这个从U47到U46的走线也要整理一下:

修改后:

至此,地址线的规则设置完毕。

(29)等长DRC的显示开关:

(30)DDR芯片之间连接的DQ走线,即参考电压走线,推荐使用粗的走线,而不是铜皮,使用粗走线的效果是要好于一个平面的,如果是在电源层布一个平面的话,容易是其它平面或者网络参考的这个平面,将其它的噪声耦合到这个DQ平面。下面这两根线是DDR电压参考的线,DQ和CA,使用10mil的走线相连接。

27、对于多层板来说(6层、8层),它的电源滤波电容主要起一个平板滤波的作用,布局的时候均匀分布就行,没必要必须靠近要滤波的引脚放置。电容都有它的滤波半径。应该是在电路板上一颗电容对于周围一定半径内是有滤波作用的。

28、要把BGA扇出的孔,引脚和孔之间的连线,电源和地线做一下加粗处理,一般加粗到10mil。

29、主CPU阻容器件布局的时候,先布左上四分之一,这四分之一范围内从上往下依次放置。

30、晶振布局走线的时候要留出一个能够包地的空间范围,晶振包地处理,晶振相关的地焊盘,通过过孔下主地,不和晶振包地的地相连。两条晶振线之间串接一个阻值较大的电阻,有利于降低它的功耗。

31、使用快捷键8对齐后,对齐的引脚会被高亮,按j取消高亮即可。

32、铺铜时铜皮和焊盘之间连接方式,将十字连接修改为全连接:以前工艺的不成熟,考虑到散热的需要,使用十字连接,现在工艺很成熟了

33、一个8-16的过孔,长时间可以通过400-500mA的电流,短时间可以过大概700mA的电流。

34、滤波电容放置的时候,最好让电容引脚和过孔做一个对齐,这样方便连线。

35、CPU的滤波电容等走线走完以后再放置。

37、长距离的走线最好留给比较好的层,如本例程中的Si2层。

38、在BGA下面的过孔,会要求有一个塞孔的工艺。

39、对于一些局部的电源走线,可以先用线将网络走通,最后一步再将线换成铜皮。

40、安规方面,通过一个0欧电阻相连的两个GND,铜皮之间的距离为2.8mm,也就是88mil。

41、铺铜皮的时候,按下s键,在对应位置画出铜皮,然后按下d键,在画好的铜皮上单机一下,让该铜皮处于被修改的模式,然后再在这个铜皮需要连接到的网络上单机一下,这个铜皮就会连接到对应的网络。

42、网络变压器对应的所有层都要挖空。比如说要防一个4000kV的电压,对于板材RF4的抗压性能,可以计算出需要挖空几层。

43、对于高电压走线或者铜皮在电流上面最好不要留有过多余量,比如12V点电压走线,要求走3A的电流,但是你设计留有过多余量,可以走5A,那么这样反而会对其它信号造成一定的影响。

44、电源芯片的地引脚要尽可能的多打一些进地孔,电源芯片的反馈线最好粗一些。

45、网线要用差分对来走,网络变压器到网口的走线一般不用控阻抗,也不用做等长(最好等长),网络变压器到主控芯片的修线需要控阻抗。网线是要过安规的,具体线宽要根据过多少的安规计算出来。

46、射频线最好走曲线,不要走直线,长度不能发生在射频波长的四分之一或者二分之一处。对于6层板,假如射频线走在第一层,其参考的层为第三层,但是第二层为GND,那么就需要把第二层在射频线下面的区域挖空,假如射频线宽是12mil,挖空的宽度可以为36mil。射频线周围打孔的孔间距,一般要求为波长的二十分之一的范围内,个人习惯孔间距为37mil。如果视频线周围铜皮相对较少的话,可以在线的周围打两排间距为37mil的孔,错落放置。

47、一般非机械孔周围的避让区为孔径的1.5倍左右。

48、内电层的过电流能力要比表层差一些。

49、电源尽可能使用铜皮链接。

50、电源网络拉线的时候,对于一些比较分散的网络,可以先用走线连起来,这样就知道了大概的路径和过层,然后再使用铜皮将这个走线替代。

51、最后放置滤波电容的时候,由于BGA下方空间有限,可以适当将地泛出的孔进行和孔。

52、电源层的分割:

(1)按下快捷键e,然后:

注意这个线宽,也就是间距,一般为10/12/15mil,这个是根据压差来的,压差大的话就设置大一点。

(2)

走在Si3层的DDR走线,参考的是Power层,在Power层做分割的时候应该避免造成Si3层的DDR走线跨分割,跨分割走线会在夸分割的区域产生杂波,对信号造成影响。

(3)对于较窄的电源铜皮,如果中间有很多其它网络的过孔,这些过孔会将这个电源的铜皮打烂,导致其通流变得很差。

(4)对于Power层,并不需要将整个层都铺成电源,只在比较集中的地方铺就行,其它小网络的电源可以通过其它层的铜皮或走线接过来,然后power层其它区域留着铺地。

(5)一定要保证信号参考平面的完整,尽量减少信号的跨分割区域。

(6)铺铜区域分割好以后,还要做一个禁止布线区,

通常电源层有一个20H的原则,它是相对于它的参考层来说,比如:Si3层参考的是Power层,Si3层的走线间隔是4mil,那么Power层就需要相对板框内缩80mil。这个内缩的量有点大,通常我们做电源层切割的时候,不会把整个Power层都作为电源层,而是会把最外面这一层作为GND,作为GND的话只需要内缩20mil就行:

然后再来切割铜皮:

铺完以后的:

后续如果需要调整某部分的铜皮,只要调整Anti Etch层上的走线即可,调整再将上面步骤操作一下,铜皮就更新了。

53、在设置规则的时候,从一开始就应该将电源的规则设置好。

54、长距离的平行走线是最容易发生串扰的。

55、像下图这种情况,如果是速率更高的信号,会考虑将反焊盘挖去一部分,让走线出来就有参考,当然DDR的速率不高,不用这样处理。一个20mil的反焊盘影响的谐振大概在15G左右。

56、USB3.0走线有必要做一个包地处理。

57、最后将各层的线推一推,尽可能留出大的地方来铺地。

58、铺铜的时候,BGA区域尽可能不要把铜铺进去,如果把铜铺进去的话会导致它散热很快,导致焊接的时候出现虚焊等问题,让BGA的地通过fan out的孔和地链接。

59、在顶层,铺地的GND铜皮不要和晶振包地的铜皮链接在一起。

60、安规上要求,GND_Earth和GND铜皮的距离为88mil。

61、铺铜的原则,只包GND,不包其它的网络,包GND引脚周围尽可能大的空闲空间。

62、

63、调整铜皮的明暗程度:

64、通过焊盘往铜皮上打GND孔的时候,可以使用12mil的线连接焊盘和孔。

65、晶振的GND要用一个单独的孔下主地。

66、DCDC接地如果过孔少了会出问题。

67、补地孔主要是补滤波电容和一些功耗比较大的地方,一些走线的旁边平行走线打一些地孔。

68、ESD器件的GND引脚虽然接到了地的铜皮上,但是在引脚旁边也要打一个过孔接到主地上,让浪涌能够迅速的被主地吸收。

69、差分走线在换层的地方,要在周围加一些过孔,即回流过孔。

70、尽量保证每个GND引脚旁边有一个过孔。