前言

这一篇文章将遵循pcb设计的规则,记录规则设定的方法。

此外,由于allegro对于新手学习特不友好,尤其是用惯了AD的用户,初次上手会有明显落差。因此本篇结束后我将暂时结束按照pcb设计流程来讲解操作的记录,转而去写一些更为基础但是在操作上影响深远的,比如快捷键设置这种。毕竟本人也是初学,在第一次设计中遇到了数不清的困难,还需要从头系统性地捋一捋。

规则设置

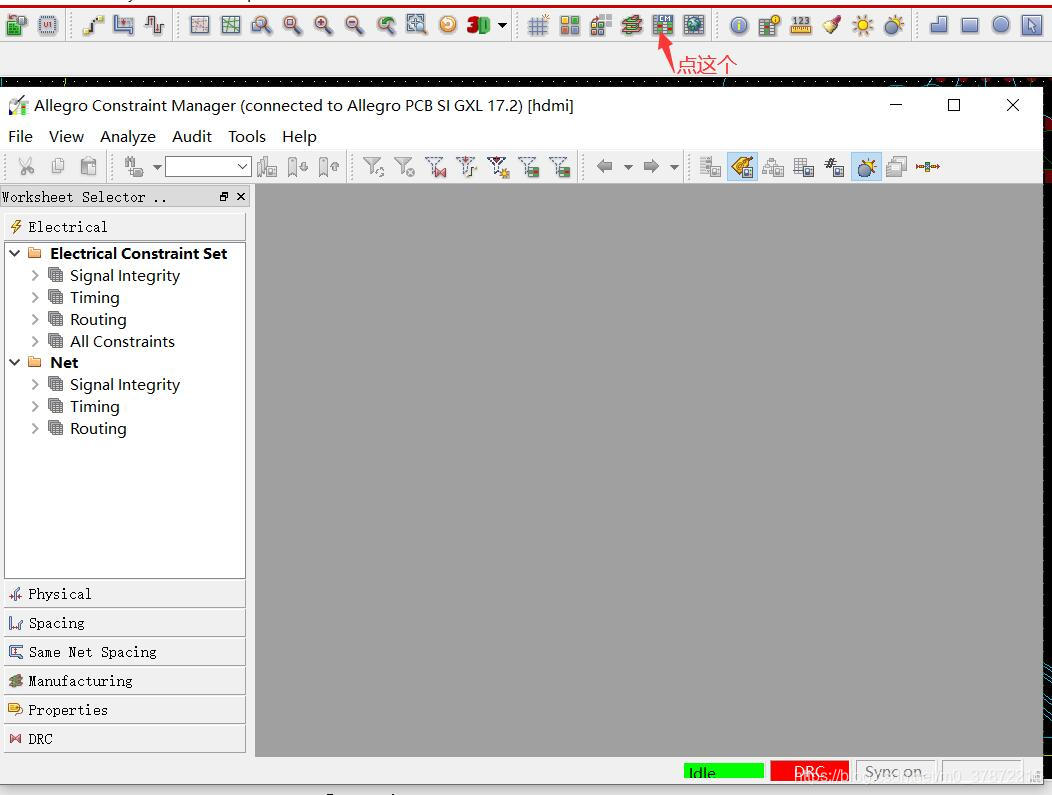

allegro里面的规则管理器叫constraint manager(约束管理器)。打开方式如下图所示:

设置线宽

按照下图所示,先对所有层的基本信号线宽进行设置,设置成6mil。

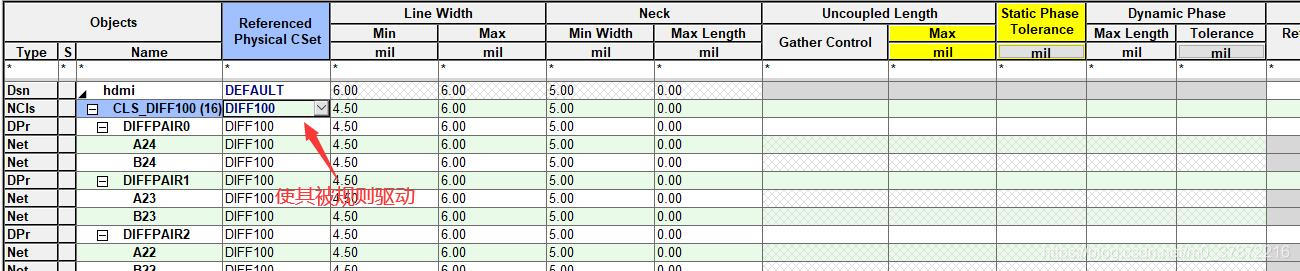

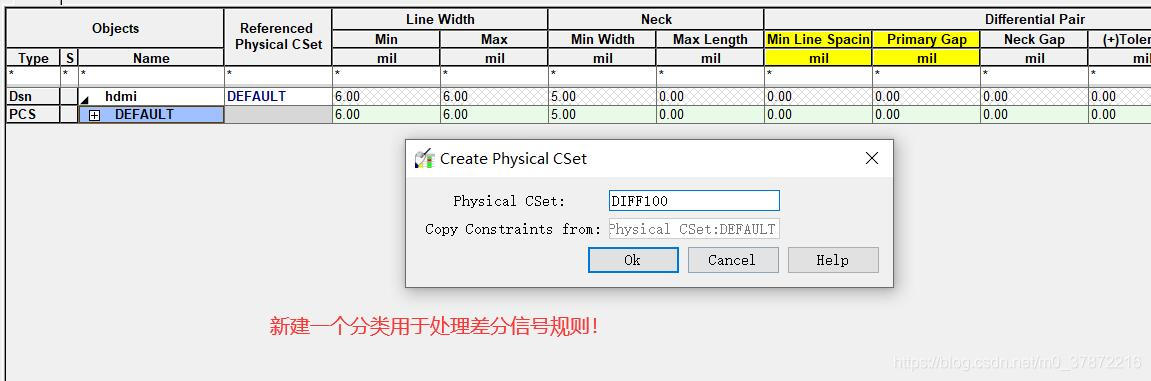

由于这次设计包含差分线,所以我们需要为满足阻抗匹配的需求而为差分线单独设定规则。这里首先新建一个规则,右键点击deafult选择create physical Cset,如下图所示。差分对需要100欧姆阻抗匹配,因此这里把名字设定为“DIFF100”,易懂。

这里修改,令线宽为4.5mil,间距为8mil,这样阻抗匹配值为100欧。

这样是不是差分线的规则就OK 了呢?

这样是不是差分线的规则就OK 了呢?

显然没有,不信自己去画一下。至于为什么没有,因为allegro里有个所谓的“约束使能”这个概念,之后会处理。

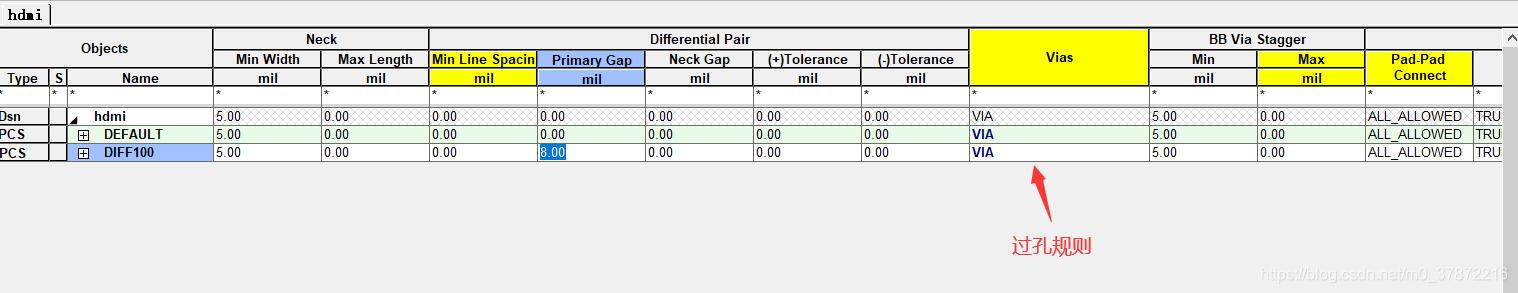

设置过孔

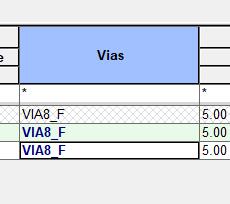

继续上面的页面,往右移动,可以看到vias这一栏,设定过孔规则。

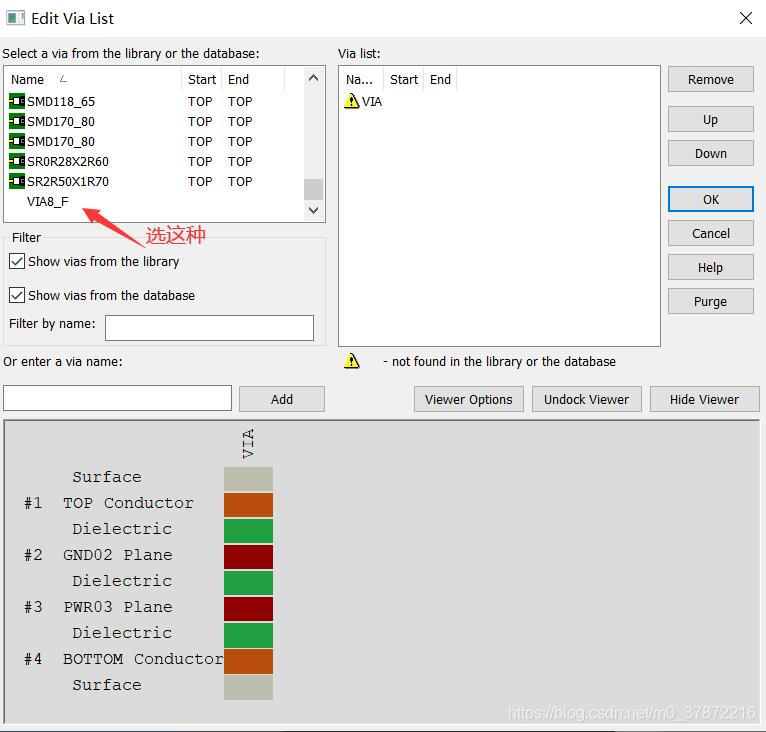

双击VIA,弹出以下窗口,这里采用VIA8_F过孔

双击VIA,弹出以下窗口,这里采用VIA8_F过孔

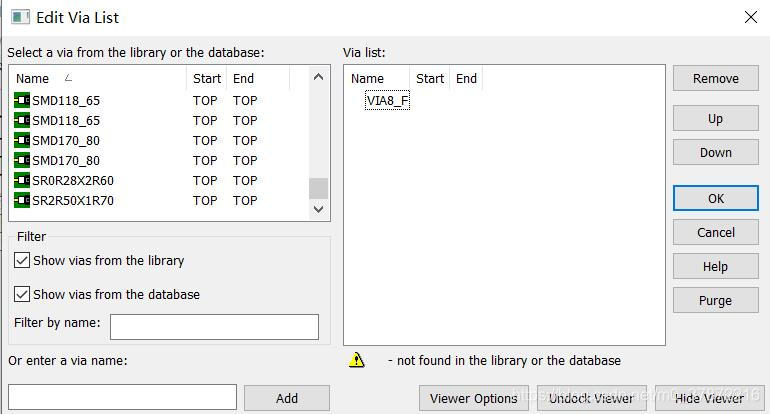

选中之后可以看到选好的过孔类型被移到了右边,然后点击OK即可。

规则设定,只需要一种尺寸的过孔就够了,如下图所示:

规则设定,只需要一种尺寸的过孔就够了,如下图所示:

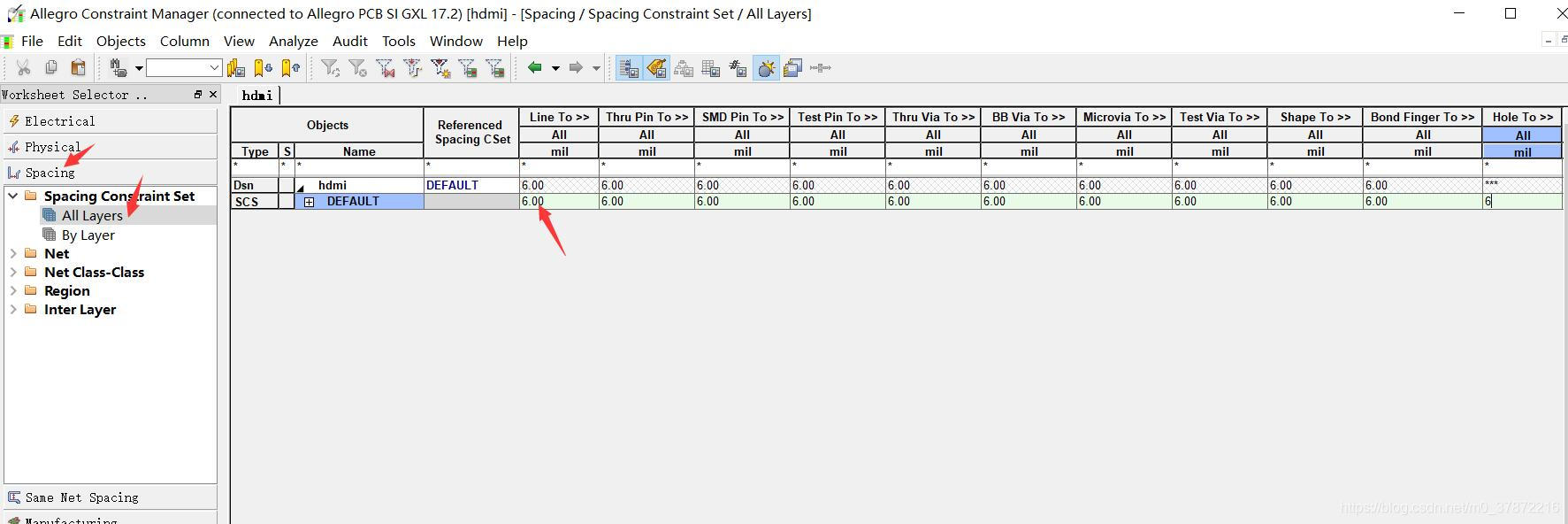

间距设置

间距设置的界面如下图所示,这里先设定所有的最小间距为6mil。

铜皮最好与其他的间距大一点,因此设定为10mil,如下图所示:

规则使能

刚才说过了,差分对的规则其实没有使能,那么使能是怎么一回事呢。

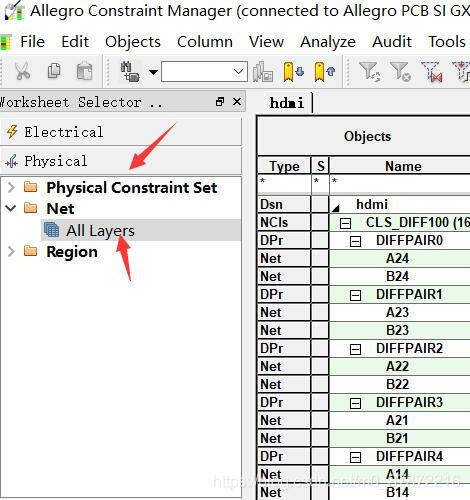

先按下图所示进入网络界面:

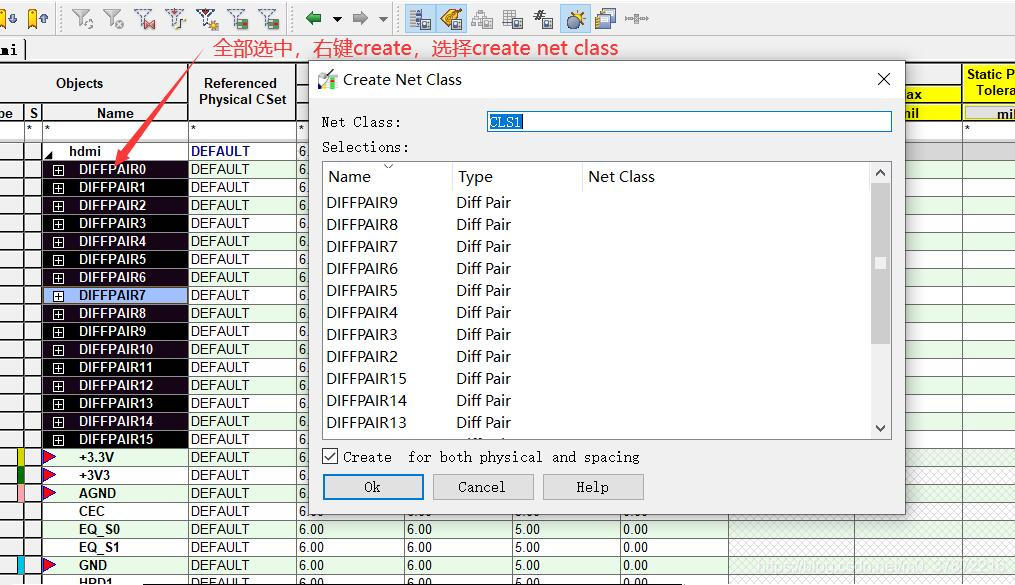

这里可以看到之前添加的差分对们都在这里了。用shift键多选选中所有的差分对,随后右键单击,选择create ->create net class。如下图所示:

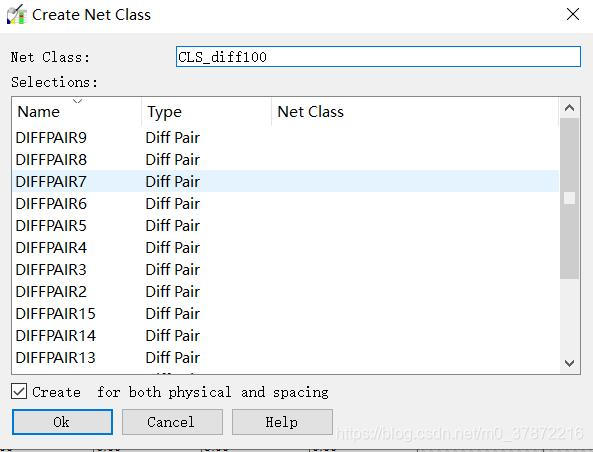

起个言简意赅的名字:

这样就等于新建了一个类(和AD的class一样的),然后在这个类的属性栏目里将其使能为“DIFF_100”规则。

这样就等于新建了一个类(和AD的class一样的),然后在这个类的属性栏目里将其使能为“DIFF_100”规则。

综上,allegro的约束使能目前来看是这么一回事:

1.你的这部分只需要满足基本约束就够了,那就不需要特意去改,因为默认情况下所有网络都是基本约束。

2.你的这一部分网络需要另设规则,比如差分对,电源网络等,那么你首先需要新建规则,随后在网络这边手动为其使能,令其匹配上相应的新规则。