二週間の研究を締結し

、我々は彼自身のコンピュータの第四はじめとコンテンツの第五章を教え今週、4、5つの章では、私はゲートと回路についての何かを学び、学ぶためにこれらの章を通して、コンピュータのハードウェア層についての知識に私たちを紹介します知識のメンバーの計算。

/第IV章ゲートおよび回路/

回路:ゲート回路は、指定された論理機能を実現するため、相互に組み合わせたものです。

:ドアと私の回路はまた、三つの異なる表現を学びました

。1.ブール代数を:それは英国の数学者ブール発明によって代数計算され、その発現は、回路の活性を実証するための優れた方法です。

2.論理図:それは回路のグラフ図です。特定グラフィック記号でドアの各タイプ。

3.真理値表は:これは、入力とドアが発生することができる対応する出力のすべての組み合わせを示し、ドア機能の包括的及び特定の定義そう。

ドア:

1. NAND:NANDゲートは、それが入力されていた値を反転し、インバータと呼ばれます。

2.ザANDゲートの2つの入力信号同一の出力は1であり、そうでなければ出力は0です。

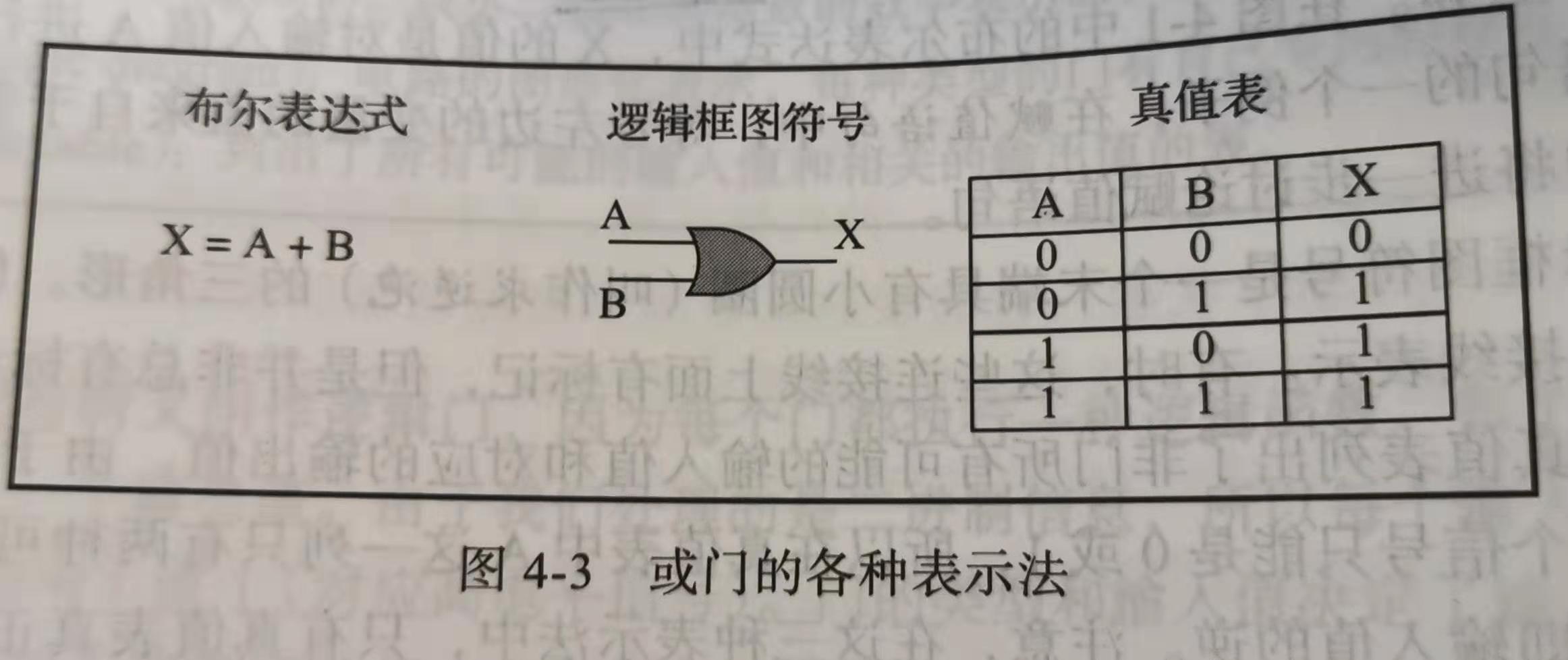

前記ORゲートの2つの入力値が0である場合、出力値は0であり、そうでなければ1。

前記XORゲート:同じ2つの入力と、出力は出力として0または1です。

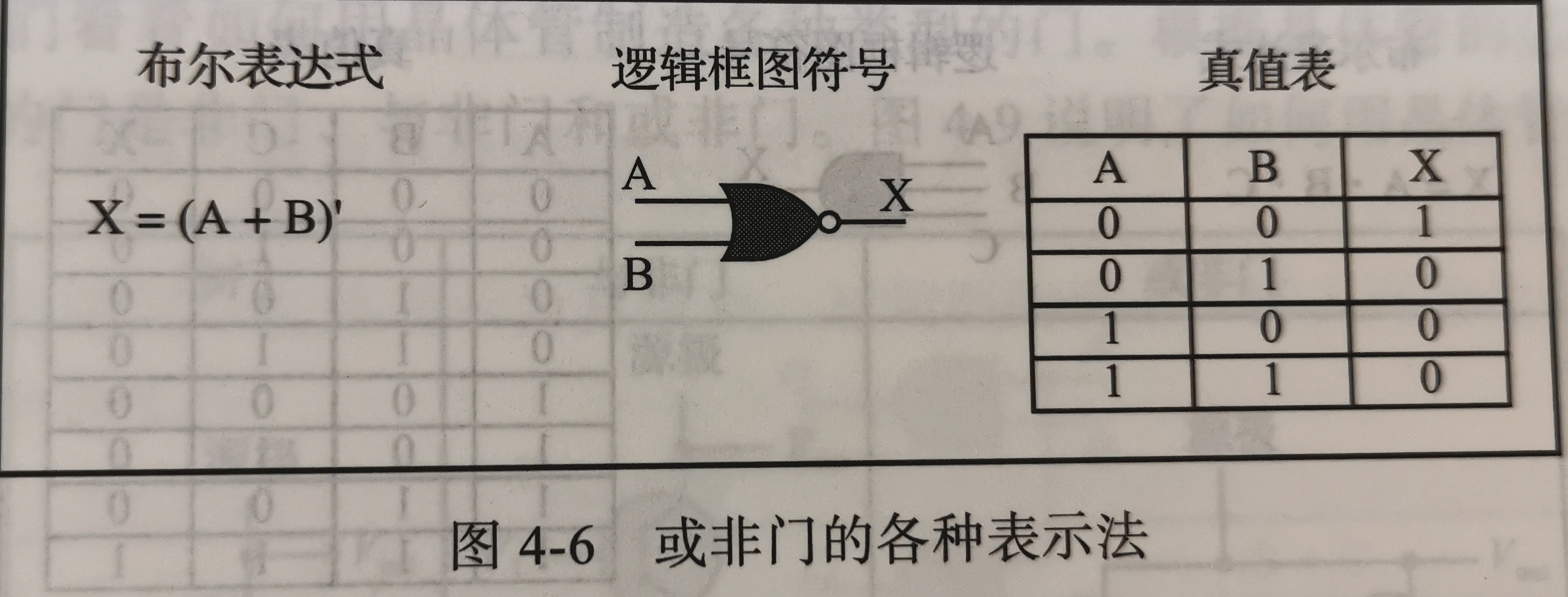

NANDとNORゲート:NANDとNORゲートであるANDゲートとORゲートの反対のドア。

ドアハンドルの評価:

二つの入力値は、1である1とゴールキーパーを生成する場合。

入力値が1の場合、入力値は、1つまたは2つ、またはゴールキーパーを生成しています。

唯一の入力値は、排他的ORゲートを生成するために、代わりに2つのうち、1である場合。

NANDゲートとANDゲートで生成された結果は、反対を生成します。

結果とは対照的とORゲートの結果が生成されたNORゲートを生成し、

ドアを構築する方法:?

トランジスタ:抵抗ワイヤまたは装置が、その役割は、入力信号のレベルによって決定されます。トランジスタは三つの端子、すなわちソース、ベース及びエミッタを有しています。

半導体:シリコンなどの良好な導体でも絶縁体材料、どちら。

回路:回路は、一方は組み合わせ回路と呼ばれ、2つのカテゴリに分けることができる、および他の順序回路と呼ばれています。

合成回路:出力回路のみを入力値の値によって決定されます。

タイミング回路:出力回路は、入力値の関数と回路の現在の状態です。

(等価回路と呼ばれる概念がある場合:入力の各組み合わせに対応する出力値は、二つの同一の出力回路を生成します。)

ブール代数分配法則:(B + C)= AB + AC

プロパティまたは

可換:AB = BAのA + B = B +

分配プロパティ:(AB)C = A( BC)(A + B)+ C = A +(B + C)

アイデンティティ:A1は、A +を= 0 =

補体を:(A ')= 0 A +(A')= 1

ド・モルガンの法則:(AB) '= A'ORB' (A + B) '= A'B'を

加算器

加算器(加算器):バイナリ値を実行するための加算演算回路。

半加算器(ハーフアダー):2桁演算回路と右とキャリーを生成します。

全加算器(全加算器)2桁を計算し、考慮回路のキャリー入力を取ります。

マルチプレクサ

マルチプレクサ(多重化器):いくつかの入力制御回路を用いて、入力データ線の信号の送信判定信号を出力します。

デマルチプレクサ回路は、逆の操作を行うことです。すなわち、それは、唯一の入力、制御線に応じてnの値を有している、入力信号の値が出力2 ^ nに送信されます。

メモリ回路

集積回路

IC:また、チップとして知られているが、複数のゲートのシリコンウェーハに埋め込まれています。

- SSI(小規模統合):1から10枚の扉

- MSI(中規模集積回路):10〜100の扉

- LSI(大規模集積回路):100 100,000ゲート

- VLSI(超大規模集積回路):10万の以上の扉

CPUチップ

CPUは、入力ラインと出力ラインを有する高レベルの回路です。

/章算出手段/

会員別のコンピュータ・

プロセッサ、ディスプレイ、画像処理装置、カメラ、ランダムアクセス記憶装置、ハードドライブ、DVDドライブ、等

保存されたプログラムのコンセプト

コンピューティングの歴史上で定義された主要なポイントである論理の一貫性データ及び運用データのための1945年に、命令1944、およびそれらが一緒に保存することができ、。この原理はノイマン型として知られ、この原理に基づいて、コンピュータ設計は、まだ現在のコンピュータの基本です。

ノイマン型

コンポーネント:

メモリセルは、データおよび命令を格納する

算術論理ユニットデータに対して算術論理演算実行

のコンピュータの入力部に外部からデータを転送するために

、外の世界に内部コンピュータからの結果出力部

の他の構成要素であることを保証するために、ステージ・マネージャとして作用します制御ユニット性能に関与

メモリ

メモリは、メモリセルの集合であり、各メモリセルは、固有のメモリ・アドレスを持っています。

アドレス指定:各アドレス可能なメモリ位置にアドレスのビット数を格納します。

算術論理ユニット

算術論理装置:コンピュータは、算術演算(加算、減算、乗算、および除算)を実行するための手段、及び論理演算(2つの値を比較する)の。

レジスタ:中間データまたは特別な値を格納するための小さな記憶領域にCPU。

入力/出力ユニット

入力部:受信データをメモリデバイスに格納されるコンピュータのコンピュータに入力された外部データとプログラムを作成することです。

現代の入力装置は、走査装置、キーボード、マウスを使用し、スーパーマーケットを含みます。

出力装置:メモリ内のデータを格納するための装置は、表示または印刷、あるいはメモリまたは他のデバイスに格納された情報の永続的なコピーで作られ、結果がコンピュータ上で外界がストレージデバイスを使用することです。

最も一般的な出力デバイスは、プリンタやディスプレイです。

制御ユニット

制御ユニット:それによって、レジスタに他の命令を実行し、他のコンポーネントの動作を制御します。

命令レジスタ:現在のレジスタを実行中の命令を格納します。

プログラムカウンタ:保存されて実行される次の命令のアドレスを登録します。

CPU:算術論理ユニットと制御ユニットとの組み合わせ、の命令を解釈及び実行するコンピュータ「脳」。

バス幅:バス上で並列に送信されるビットの数。

キャッシュ:保存するには、頻繁に小さな高速メモリのデータを使用しました。

パイプライン:小さなステップ命令は重複し得る技術的実行に分解されます。

ボード:パソコンの主回路基板。

読む - 実行サイクルを

ステップ:

次の命令を読みます

命令の解読

、必要に応じて、データ取得

の実行命令を

RAMとROM

RAM(ランダムアクセスメモリ)は、メモリの各(典型的には1バイト)分のメモリセルに直接アクセスすることが可能です。

注:各メモリセルの自然へのアクセスは、このストレージユニットを書き換えています。

コンテンツ(読み出し専用メモリ)、ROMは、操作がそれらを変更することはできません保存、恒久的で、変更することはできません。

注意:ビットパターンは、バーンインROMと呼ばれています。製造または組立ROMコンピュータの間の唯一のビットの組み合わせを燃焼させます。

二次記憶装置

例:

テープ

短所:あなたはディスクの途中でデータにアクセスしたい場合は、データの前にこのすべてのデータにアクセスし、それらを破棄しなければなりません。

ディスクの

ディスク・ドライブは、CDプレーヤー、テープレコーダーの混合物です。

トラック:同心ディスク表面。

セクター:トラックのエリア。

ブロック:部門に格納されている情報。

シーク:過ごし指定されたトラックの時間にヘッドを位置決め。

待機時間:配置されているヘッド下の指定されたセクタに時間がかかります。

アクセス時間:データのブロックを読み取り開始前に費やした時間は、すなわちシーク時間と時間を待って。

転送速度:メモリにディスクからのデータ転送レート。

シリンダー:ディスク表面の全ての同心トラックのコレクション。

CDやDVD

フラッシュメモリ

フラッシュメモリを消去することができる書き込み可能な不揮発性のコンピュータメモリです。

フラッシュメモリは、ソリッドステートディスク(SSD)を作るために使用され、ソリッドステートドライブは、直接、通常のハードディスクで置換することができます。

タッチスクリーン

それは、画面上の指またはスタイラスでユーザタッチを検出することができ、および応答に加えて、従来のディスプレイと同様に、テキストやグラフィックスを表示します。

タッチスクリーンは、タッチスクリーンの位置を知ることができ、タッチが検出されただけではありません。

タッチスクリーン技術を実装します。

抵抗性タッチスクリーン

静電容量式タッチスクリーン、

赤外線タッチスクリーンの

表面弾性波(SAW)タッチスクリーン

組込みシステム

並列アーキテクチャシステム

並列コンピューティング

フォーム:

Bit-

パラレルビットレベルは、コンピュータベースのワード長を増大しています。

命令レベルの

命令レベル並列性を同時にかつ独立して行うことができるプログラムの一部の命令に基づいています。

データレベル

データレベルの並列は同時に同じ命令セットに基づくデータ群の異なるセットに対して行わ。

同期マルチプロセッサの複数のプログラムとデータセットに適用されます。

タスクレベル

並列タスクレベルは、同一又は異なるデータセットに異なる操作を実行することができ、異なるプロセッサに基づいています。

共用メモリ並列プロセッサ:ケース全体のメモリを共有する複数のプロセッサ。

並列ハードウェアのカテゴリー

並列計算の種類を反映並列ハードウェアのカテゴリ。通常、中央処理(CPU)である独立したマルチコアプロセッサコア、複数の。マルチコアプロセッサは、異なる実行ユニットにおいて異なる命令を発行することができながら、スーパースカラプロセッサは、実行ユニットに複数の命令を発行することができます。つまり、各個々のコアが複数の実行ユニットを含むことができます。

同じコアを複数個含む対称型マルチプロセッサ(SMP)。彼らは、メモリを共有し、バスを介して接続されています。対称型マルチプロセッサ・コアは、典型的には32未満に限定されるもの。ネットワークを介して接続された複数のメモリセルを含む分散コンピュータ、。クラスタは、独立機のセットによって、既存のネットワークに接続されたコンピュータによって形成されています。このようなデバイスは、一般的に1000人以上のプロセッサを含みます。

問題:理解することはより困難な様々なシステムとの間に、あまりにも平野バックその章のVを認識しながら、ルールのいくつかの扉の役割と操作は、丸暗記メモリ法よりも効果的ではない明確な十分なメモリが、まだ見つかっ具体的な関係と動作原理。

概要:本研究の第四及び第五章を通して、私はこのコースの知識は徐々に彼らは具体的な部分を見ることができることを理解することが成長してきたので、私が最初にこの一見コンピュータを学んだ、コンピュータハードウェアの知識を学びました機器を実行しているマシンの非常に複雑でハイエンドコンポーネントと、一方で私を助けて、適切な構成を使用するコンピュータの深化私の理解に反映、それはまた、私は本当にこのコースの日常生活の中で収穫製利点は、私は最終的に奇妙なパラメータや構成のコンピュータの口を販売するいくつかのセールスマンを理解することができます。最後に、我々は彼らの将来の専門的な学習のために独自のハードウォンのコンピューターへの関心を維持、無尽蔵の原動力にそれを置くことを願っています。