Requerimientos de diseño

Un conjunto completo de esquema de servocontrol incluye la computadora superior, el controlador de control y accionamiento integrado y la placa de alimentación. operador

Envíe varias instrucciones a través de la computadora host y luego el controlador ejecutará la función servo correspondiente después de analizar las instrucciones y luego controlará

El controlador transmite la señal de accionamiento al motor de accionamiento de la placa de alimentación y, finalmente, el controlador recopila información de retroalimentación para el control de circuito cerrado y las cargas.

transferir datos.

Combinado con el estado de desarrollo y los requisitos funcionales de los servocontroladores integrados en el país y en el extranjero, se formula el sistema de servocontrol en este documento.

Los principales requisitos funcionales son los siguientes:

(

1

) Desarrollar un tablero de control integrado de control de accionamiento.

(2) Al desarrollar el sistema de servocontrol de la plataforma de acoplamiento rígido-flexible, también se tiene en cuenta el control de la plataforma rígida ordinaria.

(3) Compatible con varias retroalimentaciones de codificador digital.

(4) Capaz de accionar

motores rotativos y motores lineales con una potencia inferior a

1KW .

(5) Puede accionar dos o más motores síncronos de imanes permanentes.

(6) Puede admitir múltiples modos de control, como un servo de circuito cerrado único o un servo híbrido de circuito cerrado múltiple.

(7) Apoyar a los desarrolladores para que desarrollen algoritmos de control personalizados.

(8) Puede admitir el control en línea de la computadora host de soporte, incluido el control de arranque y parada del motor, reinicio y función y configuración de cero.

Control de objetivos y otras funciones. Como establecer la posición objetivo, la velocidad objetivo y la corriente objetivo, etc.

(9) Recopile información de retroalimentación y cárguela en la computadora host para su visualización, como información de posición, información de velocidad e información actual.

La calidad del efecto de control involucra muchos factores y este artículo se centra en el desarrollo básico de la arquitectura de software y hardware.

El objetivo es desarrollar un controlador integrado de control de accionamiento completamente funcional. El algoritmo de control básico adopta el algoritmo

PID tradicional

.

Este algoritmo de control más avanzado no es el objetivo de este artículo.

3.2

Descripción general de los sistemas integrados

Los sistemas integrados se utilizan cada vez en más campos de la sociedad actual

[41]

, desde el aeroespacial hasta lo portátil.

Los dispositivos y productos integrados se pueden ver en todas partes. Especialmente su alta flexibilidad, el diseñador puede ajustar el

El sistema agrega o elimina funciones, lo que genera cada vez más desarrollo de productos integrados.

Dado que el sistema integrado no requiere funciones sólidas y buena versatilidad como el sistema informático, el sistema integrado es principalmente

Un sistema informático dedicado que se organiza de forma flexible según los requisitos funcionales del usuario. Los proyectos reales a menudo se ven afectados por el medio ambiente,

Los requisitos como el costo, el consumo de energía y el volumen son limitados, por lo que muchos factores han provocado diferentes diseños, por lo que es difícil

Elaborar un conjunto de soluciones adecuadas para diversas aplicaciones. Por lo tanto, de acuerdo con las necesidades reales del proyecto, el software requerido se puede adaptar de manera flexible.

Módulos de hardware para formar un sistema que en última instancia cumpla con los requisitos de producción.

Los sistemas integrados se pueden resumir en las siguientes etapas de desarrollo:

La primera etapa: los sistemas integrados en esta etapa se centran principalmente en los campos de bajo precio y funciones simples. La mayoría de las aplicaciones de este sistema.

En ocasiones de gama baja, como funciones de monitoreo simples, funciones de indicación y campos de control industrial con requisitos de baja precisión.

La segunda etapa: marcada por un kernel integrado de alto rendimiento y un sistema operativo integrado. Bajo consumo y alto rendimiento en esta etapa.

El kernel es capaz de ejecutar sistemas integrados y de realizar eventos multitarea complejos. Y la compatibilidad y extensibilidad se vuelven

Muy mejorado, lo que permite la creación rápida de prototipos, acorta el tiempo de desarrollo y reduce los costos.

La tercera etapa: las características principales de esta etapa son importantes avances en la tecnología de fabricación de chips. Cada vez se integran más funciones en un solo

Se forma un sistema en un chip en un chip, y el sistema en un chip está cada vez más integrado, y la función se reduce mientras que el volumen y el consumo de energía se reducen.

más fuerte. Con el rápido desarrollo de Internet, se acerca la era del Internet de Todo. Tecnologías como el control industrial y

La combinación de Internet se está acercando cada vez más y la tecnología integrada está marcando el comienzo de un período de rápido desarrollo.

El núcleo de la industria manufacturera radica en el control industrial, junto con el rápido desarrollo de Internet industrial y

la popularización de las comunicaciones

5G .

Y los requisitos de respuesta rápida y en tiempo real del sistema operativo también son mayores. Por lo tanto, para cumplir con los requisitos de ingeniería para tiempo real

Para cumplir con los requisitos de seguridad, es necesario trasplantar un sistema operativo en tiempo real adecuado, y los requisitos de seguridad y confiabilidad también aumentan día a día.

El principio de funcionamiento del sistema operativo en tiempo real es aproximadamente completar la función establecida dentro de un cierto período de tiempo, por lo que tiene una alta confiabilidad.

confiabilidad y tiempo real. Cuando hay una emergencia externa o un evento de interrupción del sistema interno, puede responder y solucionarlo rápidamente.

razón. Determina el orden de ejecución de tareas múltiples a través del modo de trabajo del programador de tareas, juzga el estado de varias tareas y

Hace cumplir la urgencia, respondiendo lo más rápido posible a un evento. Al mismo tiempo, el uso de un sistema operativo en tiempo real puede

Para dividir el proyecto en varias subtareas independientes, es muy fácil agregar nuevas funciones sin grandes cambios,

Simplifica enormemente el diseño de programas y facilita el diseño y la extensión del programa.

3.3

Diseño general del esquema de hardware

3.3.1

Diseño de arquitectura de hardware

La precisión del procesamiento de la industria de fabricación de productos electrónicos actual mejora constantemente, ya sea por la complejidad del algoritmo o la complejidad del procesamiento.

Ambos plantean grandes desafíos para el cálculo y el rendimiento del control del núcleo de control principal. Núcleos de control único anteriores como

ARM

,

DSP

y

Ninguna

FPGA por sí sola puede cumplir plenamente los requisitos de trabajo. La especialidad de

ARM es la función de gestión de transacciones, con el sistema operativo en tiempo real.

El sistema puede realizar procesamiento de múltiples tareas en tiempo real sin afectarse entre sí;

DSP

tiene buena potencia informática y puede procesar datos rápidamente.

Procesamiento, cifrado y modulación, etc.; la ventaja de

FPGA

radica en su gran flexibilidad y capacidad de procesamiento paralelo, que es muy adecuado para el procesamiento de datos.

Alta velocidad, requisitos estrictos en tiempo real y diseño de interfaz de comunicación y otras ocasiones. Para satisfacer las necesidades de desarrollo de la industria del control industrial, hoy

Las principales soluciones de control suelen combinarse entre sí para complementarse. En la actualidad, la arquitectura de control principal del servocontrolador integrado de alta gama es principalmente

Existen los siguientes tipos:

ARM+DSP

,

DSP+FPGA

y

ARM+FPGA

.

(

1

) Arquitectura

ARM+DSP

. Combinando la función de gestión de transacciones y la función de procesamiento de datos,

la CPU

realiza la ejecución de la tarea.

presión de línea mientras que

DSP

comparte tareas de cálculo de datos, asegurando el rendimiento en tiempo real del sistema. Pero también trae la capacidad de expandirse

Funciones deficientes, una vez que se complete la asignación de recursos periféricos, será muy problemático si desea agregar nuevas funciones en el futuro, o incluso simplemente

Se puede sustituir por un chip con más recursos.

(

2

)

Arquitectura

DSP+FPGA .

DSP es responsable de la función de operación del algoritmo, mientras que FPGA es responsable de la adquisición y comunicación de datos.

La función de interfaz transmite los datos recopilados al

DSP

para un cálculo unificado y, finalmente,

el DSP

emite la señal de control. pero desventajas

Se trata de una mala capacidad de gestión de tareas, que obviamente falta en la industria del control industrial con cada vez más funciones.

(

3

)

Arquitectura

ARM+FPGA .

Teniendo en cuenta tanto las funciones de gestión de transacciones como las funciones de procesamiento de señales digitales, no solo el procesamiento en tiempo real

La capacidad de gestión es sólida y también se ha mejorado la escalabilidad. Hoy en día, existen muchas herramientas auxiliares de diseño de alto nivel, a través del lenguaje de alto nivel.

O cree un modelo para el desarrollo

de FPGA

, que puede simplificar efectivamente

el

proceso de diseño de FPGA. Por lo tanto, en este esquema

FPGA

puede reemplazar la función de cálculo de datos de

DSP

. Después de la optimización, el tiempo de cálculo puede ser más rápido y en tiempo real

más fuerte.

Por supuesto, también existen en el mercado arquitecturas como

ARM+DSP+FPGA

y

SoC

. Estas soluciones más avanzadas no tienen

La función de consulta es más completa y potente, pero las deficiencias también son muy obvias. Aunque teniendo en cuenta la capacidad de procesamiento de tareas, los datos

potencia de procesamiento y capacidades de expansión de interfaz, pero la complejidad del sistema también ha aumentado linealmente, no solo teniendo en cuenta el diseño del hardware, sino también

Considerar la cooperación en software. Por otro lado, no es rentable considerar los costos de mano de obra y de materiales.

La dificultad y el mantenimiento son relativamente pobres, por lo que estas arquitecturas no se consideran en este artículo.

El propósito del sistema de servocontrol diseñado en este artículo es desarrollar un servosistema que pueda adaptarse a las características de la plataforma de acoplamiento rígido-flexible.

Sirviendo a los controladores para cumplir con el diseño funcional requerido y las pruebas de rendimiento. Comparando las ventajas y desventajas de varias arquitecturas y combinando varias

Teniendo en cuenta los factores, finalmente se decidió elegir

la arquitectura ARM+FPGA

como objeto de desarrollo. Las razones específicas son las siguientes:

(1)

El sistema de servocontrol desarrollado en este documento debe cumplir con la función multitarea, por lo que se selecciona el

núcleo de control principal

ARM

Corazón y junto con un sistema operativo en tiempo real, para cumplir con los requisitos funcionales del sistema de control.

(2)

Para adaptar el algoritmo de control de la plataforma de acoplamiento rígido-flexible, es necesario muestrear datos de sensores multicanal sincrónicamente, lo que requiere práctica

La importancia de la puntualidad y el paralelismo. Debido a la estructura especial de

FPGA

, determina su rendimiento en tiempo real en muchos núcleos de control principales.

Puede ser el más potente y tiene las ventajas del procesamiento paralelo, que cumple con los requisitos funcionales y de expansión del sistema.

(3)

El rápido desarrollo de los semiconductores hace que el rendimiento del núcleo

ARM

sea cada vez más fuerte y los envíos de microprocesadores

También aumenta año tras año y la variedad es rica para elegir.

El núcleo ARM

avanzado

no solo mejora en gran medida la frecuencia de trabajo, sino que también

También integra una unidad informática de punto flotante de núcleo duro, por lo que el chip

ARM avanzado

tiene suficiente rendimiento para procesar datos y cooperar con

El poderoso paralelismo y la escalabilidad de FPGA cumplen con los requisitos de rendimiento del sistema.

(4)

El último punto es considerar la relación entre rendimiento y costo: el rendimiento común genera un alto costo y el bajo costo también es limitado.

rendimiento controlado. El alto rendimiento y el bajo costo son como la pata de un oso y un pez: no se pueden tener ambos, por lo que es necesario elegir un compromiso.

en el esquema.

Después de un cierto proceso de diseño, la solución

ARM+FPGA es comparable en función y rendimiento.

Soluciones avanzadas como ARM+DSP+FPGA

o

SoC

, pero el coste es mucho menor.

En resumen,

la arquitectura ARM+FPGA

está más en línea con el sistema de servocontrol diseñado en este artículo.

3.3.2

Selección del chip de control principal

El núcleo de control principal es el cerebro de todo el sistema y ocupa una posición importante. Un núcleo de control principal adecuado facilitará el desarrollo posterior.

El desarrollo resulta sencillo y fiable, por lo que es muy importante elegir un núcleo de control principal adecuado. Sin embargo, debido a la aparición de varios tipos de microprocesamiento

Existen miles de tipos de chips de diferentes marcas y series, lo que trae grandes desafíos a la selección. Entonces

Puede considerarse desde los principios de versatilidad, rentabilidad, sostenibilidad, sustitución y conveniencia de adquisición. un procesador adecuado

No solo considere sus propios problemas de rendimiento y recursos, sino que también debe considerar las instalaciones de soporte completas del procesador. Coincidencia del procesador

Las instalaciones incluyen si las herramientas de desarrollo están completas, si los recursos de aprendizaje son abundantes y si existen ejemplos de implementación exitosa.

Como se muestra en la imagen

*

Muestra la cuota de mercado nacional de los microprocesadores de los principales fabricantes de semiconductores.

Como se puede ver en la figura, la empresa con mayor participación de mercado es

ST

, con una participación de mercado de hasta el

21%

. El principal producto de la empresa es

STM32.

Serie de microprocesadores.

Los chips STM32

se pueden dividir en diferentes series según las diferentes arquitecturas centrales

, entre las que se encuentran

M4 y M7

de alto rendimiento.

Las series kernel son muy versátiles y pueden sustituirse entre sí con sólo un pequeño cambio.

Además, el entorno de desarrollo del chip

STM32

es relativamente completo y maduro, no solo tiene una gran cantidad de manuales oficiales y rutinas de desarrollo,

Y también hay muchos sistemas integrados que han sido trasplantados. Por lo tanto, después de varios análisis y resúmenes, utilizando

el microprocesamiento

STM32

El microcontrolador es una mejor solución, que puede cumplir con los cinco principios de selección de un microcontrolador.

Teniendo en cuenta los requisitos de diseño, el modelo de selección final es el chip

STM32H743IIT6

como núcleo de control principal del

lado

ARM.

Corazón. El chip es un producto de serie de alto rendimiento del núcleo

Cortex-M7

, con ricos recursos periféricos de hardware y su

Con un reloj de trabajo de alta frecuencia, puede ejecutar varias instrucciones de forma rápida y eficaz.

La selección de chips FPGA

es

relativamente simple: los dos

fabricantes

de FPGA

más grandes del mundo, Intel y Xilinx .

El rendimiento de los chips de referencia de producción es similar, por lo que la consideración principal es si los recursos lógicos son suficientes y elegir un chip con el que esté familiarizado.

desarrollo de chips.

El modelo de chip FPGA

seleccionado en este artículo

es

EP4CE22F17C8

. El chip tiene rico

Recursos en chip, recursos de memoria y múltiples redes de reloj global y bucles de fase bloqueada.

3.3.3

Diseño de arquitectura del sistema de hardware

La arquitectura del sistema de hardware se puede dividir en

partes

ARM

y

FPGA , como se muestra en

la Figura 3-2 . La FPGA integra principalmente

El controlador principal, el módulo

FOC

y el módulo de retroalimentación son tres módulos principales. El controlador principal es responsable del control de todo el sistema

FPGA

, cada uno

La configuración de parámetros, el control del variador y el intercambio de datos de cada módulo son manejados por el controlador principal;

el módulo FOC es el motor

El algoritmo central del control realiza el procesamiento de transformación de coordenadas y el procesamiento de modulación de ancho de pulso en la corriente muestreada y, finalmente, genera

La

onda PWM se envía al módulo de potencia inteligente para controlar el motor; el módulo de retroalimentación integra los tipos de codificador requeridos.

Hay codificadores digitales y codificadores analógicos respectivamente. Al configurar el tipo de codificador y luego filtrar, el resultado final

Después de eso, los datos se envían de vuelta al controlador principal para su procesamiento unificado.

ARM

se compone principalmente de una capa de aplicación, una capa de controlador y una capa de sistema, y los periféricos están conectados al núcleo a través de un bus de alta velocidad.

Se tratan algoritmos de control, funciones de comunicación y gestión de tareas. Los métodos de comunicación incluyen puerto serie,

RS485

,

CAN

y Ethernet.

Cuatro tipos, para instrucción y transmisión de datos con la computadora host;

SPI_FLASH

,

EEPROM

y

SDRAM

se utilizan para tareas del sistema

gestión de tareas, información de configuración necesaria del sistema de almacenamiento y una gran cantidad de caché de datos informáticos; finalmente, todos los eventos de tareas son manejados por

El sistema operativo FreeRTOS realiza una programación unificada.

ARM

y

FPGA

están interconectados y comunicados a través de un bus llamado Controlador de Memoria Flexible (denominado

FMC

). Su diagrama de bloques funcional específico se muestra en la Figura

3-3

, que incluye el controlador de chips de memoria de uso común. controlador

Las operaciones de lectura y escritura del chip en la unidad de almacenamiento se realizan a través

del bus AXI

y el bus

AHB .

FPGA

puede verse como

ARM

Una SRAM

externa

, por lo que

la FPGA se puede leer y escribir en el modo de control

SRAM .

FMC

integra las características de las señales de lectura y escritura de varios chips de memoria y, de acuerdo con los parámetros de rendimiento de diferentes chips de memoria, establece

Los principales parámetros de tiempo: tiempo de configuración de la dirección, tiempo de configuración de los datos y tiempo de retención de la dirección. Los núcleos se utilizan en la ingeniería práctica.

Chip indicadores de rendimiento, calcule el tiempo requerido y finalmente configure los registros correspondientes. En este artículo,

se selecciona el modo

A.

El modelo de temporización, el modo

A

admite control de temporización de lectura y escritura independiente, y su temporización de lectura y escritura se muestra en las Figuras

3-4

y

3-5

.

El núcleo de control principal utilizado en combinación con la solución de hardware en este artículo es

STM32H743IIT6

, por lo que la elección final es más adecuada.

FreeRTOS

se utiliza como sistema operativo de este servocontrolador.

Como sugiere el nombre, FreeRTOS

es un sistema operativo gratuito en tiempo real, que es muy amigable para un producto.

, puede reducir efectivamente el costo.

FreeRTOS

tiene las ventajas de ser escalable, compacto y fácil de usar, y tiene una variedad de

El modo de programación de tareas, lo que es más importante, el usuario puede asignar artificialmente prioridad de ejecución a cada tarea de acuerdo con el grado de ejecución de la tarea en tiempo real.

A nivel de línea, el sistema puede dar prioridad a la ejecución según la prioridad de la tarea, por lo que es muy adecuado para ocasiones de control industrial.

3.4.2

Diseño de la arquitectura del sistema de software

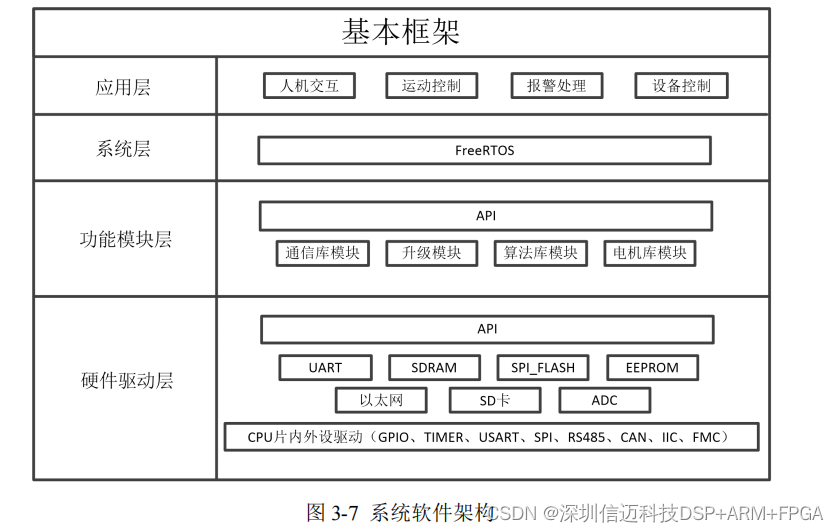

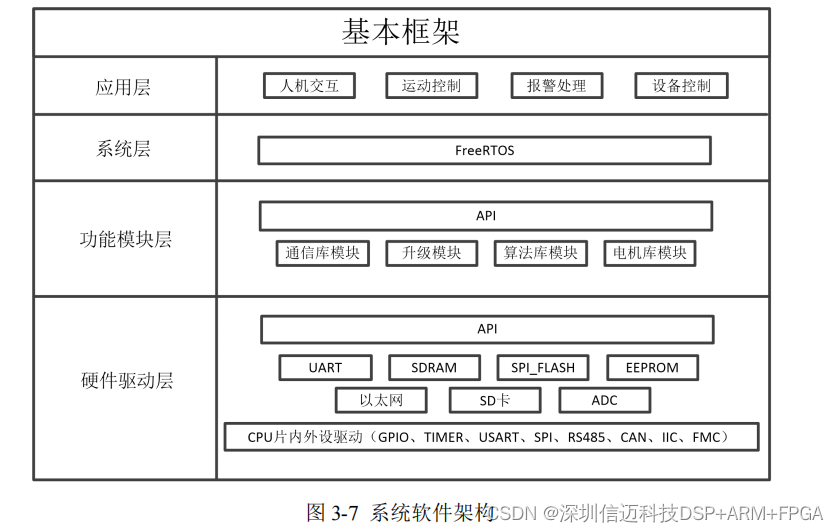

La Figura

3-7

muestra la arquitectura de software del controlador integrado del variador diseñado en este documento. El sistema de software de menor a mayor total.

Está dividido en cuatro niveles y no es posible exagerar las llamadas de capa entre capas. Además, el acoplamiento entre cada módulo es bajo y los módulos proporcionan

La interfaz

API unificada

es llamada por la capa superior.

La capa de controlador de hardware se utiliza para controlar los recursos de hardware de la placa para garantizar su funcionamiento normal y proporcionar

la API

para la función.

puede ser llamado por el módulo. Esta capa se compone principalmente de la parte de comunicación y la parte de gestión de transacciones.El servocontrolador puede

Interacción de datos con la computadora superior a través de comunicación, y la otra parte se usa para la administración de archivos del sistema y se usa para guardar datos de información de configuración.

Variables intermedias generadas durante las operaciones de datos y caché.

La capa de módulo de funciones incluye la implementación de funciones funcionales específicas, que incluyen principalmente módulos de biblioteca de comunicación, módulos de biblioteca de algoritmos y módulos de biblioteca de motores.

y módulos de actualización. La biblioteca de comunicación se utiliza para analizar el marco de datos de comunicación entre la computadora superior y el controlador, a fin de realizar las operaciones correspondientes.

operación; el módulo de actualización se utiliza para aumentar las funciones posteriores del sistema, a través de la actualización remota del firmware del servocontrolador; el modelo de biblioteca de algoritmos

El módulo de biblioteca de bloques y motores contiene algunos algoritmos avanzados de control de movimiento para controlar servomotores y el posterior desarrollo de nuevos

Los algoritmos de control se pueden agregar directamente a los archivos de biblioteca correspondientes sin afectar a otros módulos.

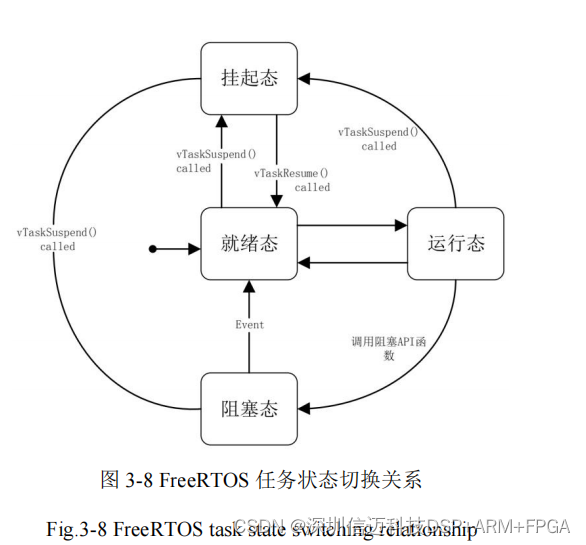

La capa del sistema utiliza

el

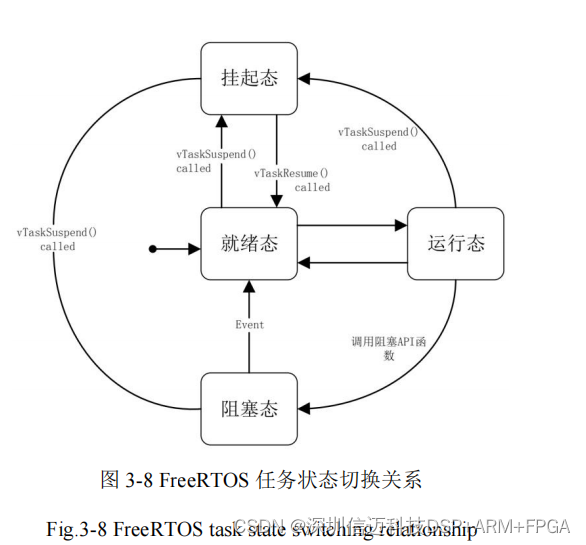

sistema operativo en tiempo real FreeRTOS y el mecanismo de programación de tareas es su tecnología central. existir

El estado de la tarea en FreeRTOS siempre está en uno de los cuatro estados en la figura siguiente, y la relación de cambio se muestra en la figura.

3-8 mostrados.

El objeto de la capa de aplicación es el operador, y el operador utiliza el software de la capa superior para realizar el sistema operativo en tiempo real.

Programación de tareas, luego llama a la función

API correspondiente

y finalmente realiza la llamada y el control del hardware subyacente.

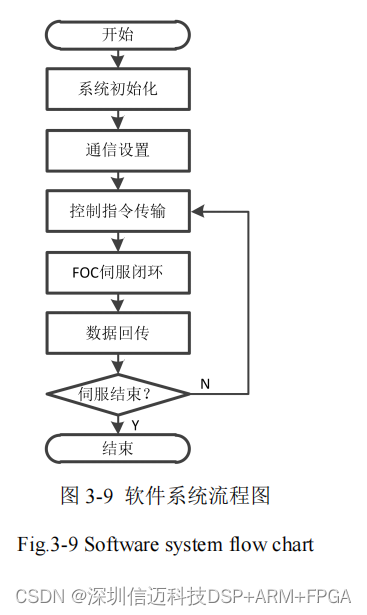

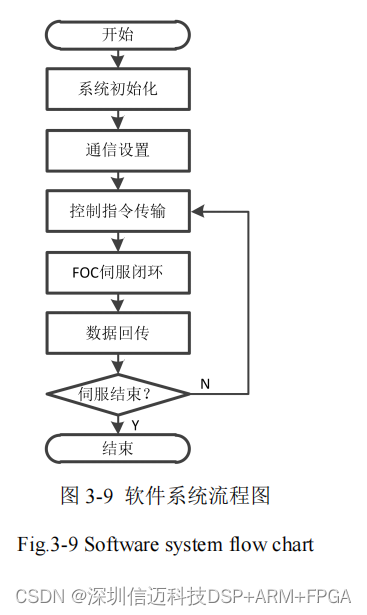

El flujo de control de todo el sistema de software se muestra en la Figura

3-9

. Inicie el encendido del sistema para la configuración inicial,

lectura

ARM

Obtenga

la información de configuración en

EEPROM

y

SPI_FLASH ,

El chip

FPGA se puede configurar a través de

ARM o

Configure a través del chip

EPCS

; luego conéctese con la computadora host para configurar algunos parámetros en la computadora host

Configure y luego transmita a

ARM

;

ARM luego

transmite el comando de control actual al registro de FPGA

a través del bus

FMC

en el módulo de memoria, y luego el controlador host configura los datos recibidos en

cada módulo en

la FPGA ;

Bajo el control del circuito paso a paso,

la FPGA lee la señal de posición del codificador y la señal actual de forma sincrónica y luego realiza la transformación de coordenadas.

Finalmente module la onda

PWM de salida

; al mismo tiempo,

la FPGA

coloca los datos recopilados en el módulo de registro y

el ARM

se comunica

Lea los datos en el módulo a través

del FMC

para operaciones avanzadas del algoritmo de control de movimiento y devuelva los datos al host

Máquina para el análisis de datos.