El servosistema completo contiene muchos módulos, por lo que no se puede presentar en detalle uno por uno, por lo que este capítulo se centra en la introducción.

Diseñe la parte

FPGA más difícil

e introduzca brevemente

el flujo de trabajo del lado

ARM .

La parte FPGA incluye principalmente FOC

El algoritmo, el algoritmo de muestreo de corriente y el algoritmo de muestreo del codificador son la base de todo el sistema de control y determinan directamente el control del motor.

El efecto es bueno o malo. Debido a la particularidad del trabajo

de FPGA

, es necesario considerar la racionalidad del tiempo de diseño y coordinar racionalmente varios

El orden de ejecución de las tareas ha incrementado enormemente la dificultad de su diseño. Lo siguiente configurará

la parte importante del programa

FPGA.

Según la descripción del diseño, se divide principalmente en

módulo de algoritmo

SVPWM , módulo de retroalimentación del codificador y módulo de muestreo actual.

4.1

Programación del algoritmo SVPWM

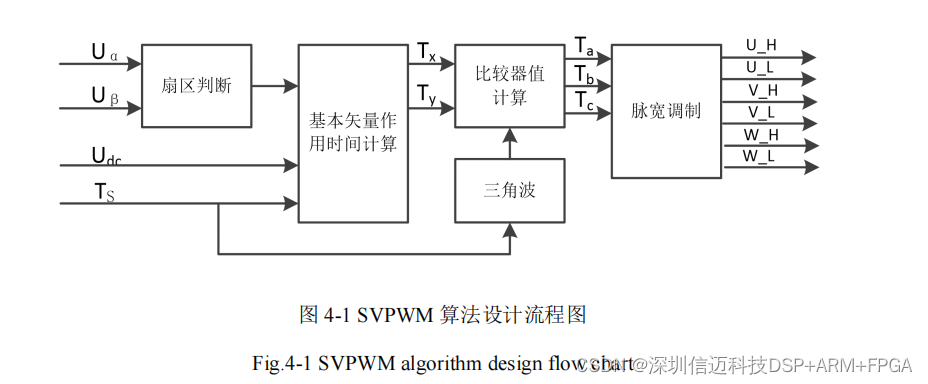

Según la cuarta sección del Capítulo 2,

el flujo de trabajo del algoritmo

SVPWM se muestra en la Figura

4-1 . Primero que nada la entrada.

Decodificando

y juzgando el sector actual, y luego calculando el tiempo de acción requerido para el vector básico del sector actual, el siguiente paso

es

En el momento del valor de comparación PWM

, finalmente realice la modulación de ancho de pulso y agregue el tiempo muerto para formar

un inversor de control de accionamiento de onda

PWM complementario.

El interruptor funciona de manera que genera el voltaje sinusoidal requerido.

4.1.1

Diseño del módulo de software

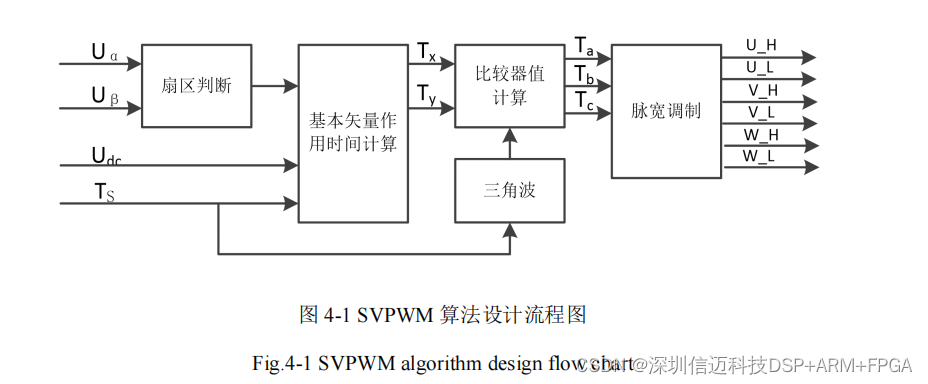

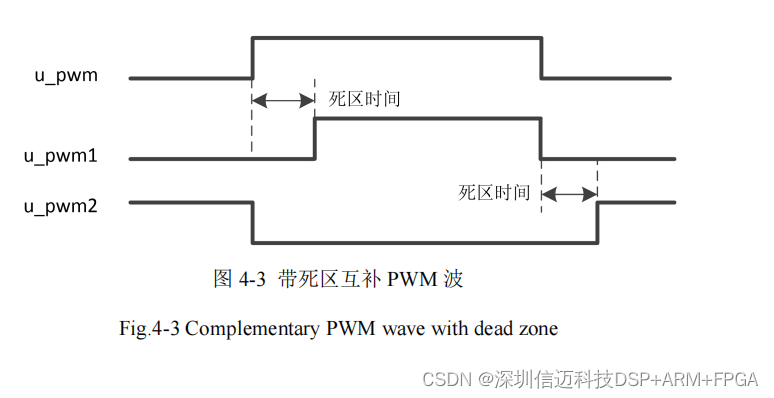

El diagrama de estructura funcional del módulo

SVPWM se muestra en la Figura

4-2

. Las señales del módulo se interpretan de la siguiente manera:

(

1

)

sys_clk

: Reloj del sistema, la frecuencia de funcionamiento es de

50MHz

.

(2)

sistema_primero

: Reinicio del sistema, activo bajo.

(3)

svpwm_en

: Señal de habilitación del módulo.

(4)

ualpha

,

ubeta

: la señal de salida del módulo de conversión

Park inverso

.

(5) Otros

: Seis ondas

PWM complementarias

.

El principio de funcionamiento y la fórmula de cálculo de este módulo se elaboraron en el segundo capítulo, por lo que no entraré en detalles aquí.

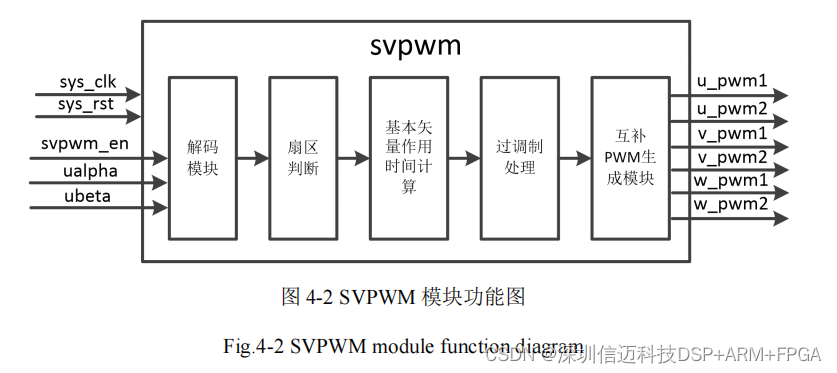

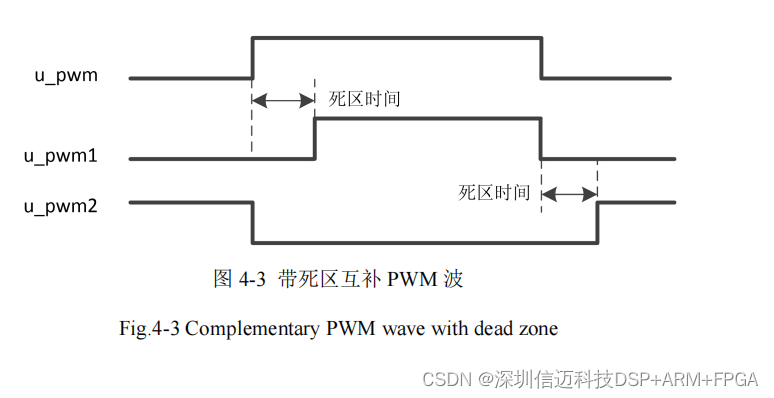

Sin embargo, cabe señalar que debido al retraso mecánico de la conmutación del inversor, es necesario generar un complemento

Onda PWM

, que puede evitar cortocircuitos y lesiones causadas al abrir los brazos del puente superior e inferior al mismo tiempo.

El principio de generar una onda PWM complementaria

con zona muerta

es utilizar la onda

PWM calculada

como objeto de referencia y luego de acuerdo con

La situación actual marca un tiempo muerto razonable. Suponiendo que la señal de entrada del inversor está activa en nivel alto, cuando el objeto de referencia cambia de nivel bajo

Cuando el nivel salta a un nivel alto, primero cierre el brazo del puente inferior, luego retrase el tiempo muerto y finalmente abra el brazo del puente superior; al referirse a

Cuando el objeto salta de un nivel alto a un nivel bajo, primero cierre el brazo del puente superior, luego retrase el tiempo muerto y finalmente abra el brazo del puente inferior.

El efecto se muestra en la Figura

4-3

. Tomando

la fase U

como ejemplo,

u_pwm en la figura

es la

onda

PWM de referencia calculada,

u_pwm1

es la onda PWM

del brazo del puente superior

y

u_pwm2

es la onda PWM del brazo del puente inferior.

4.1.2

Prueba de simulación

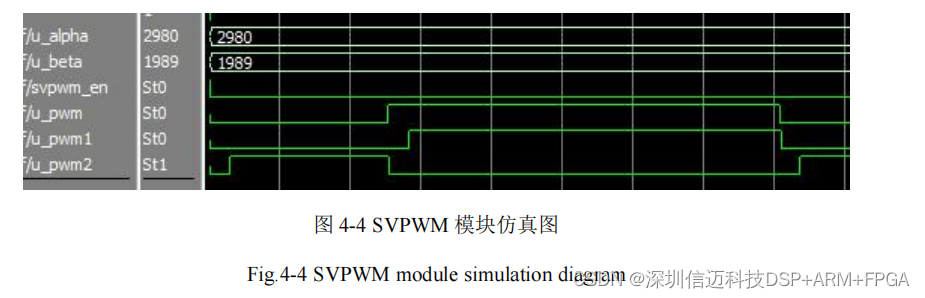

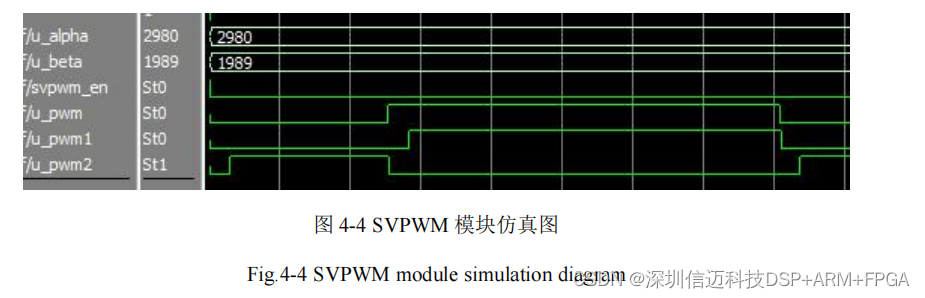

Realice la verificación de simulación en el módulo

SVPWM y los resultados se muestran en la Figura

4-4 . Se puede ver en la figura que cualquier

El valor se asigna a

u_alpha

y

u_beta

, y luego el sistema genera una

señal de ciclo de reloj

svpwm_en , después de la operación.

Obtenga

u_pwm

como onda

PWM de referencia

.

Genera ondas PWM complementarias u_pwm1 y u_pwm2 según

la señal u_pwm

,

Hay un tiempo muerto entre ambos. De los resultados de la simulación se puede ver que el módulo normalmente puede generar ondas PWM complementarias.

4.2 Diseño del programa del protocolo BISS-C

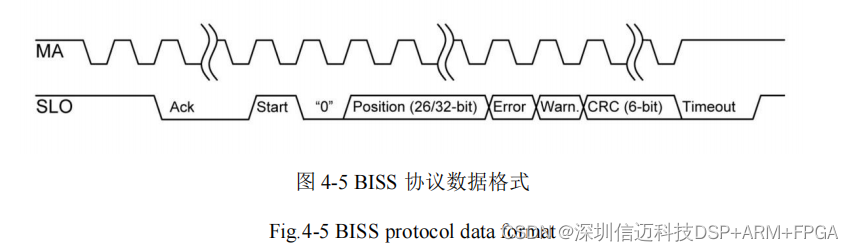

4.2.1 Estructura de datos del protocolo BISS-C

El protocolo BISS

proviene de la empresa

iC-Haus

, es adecuado para la interfaz serial bidireccional del sensor y tiene

calibración

CRC .

La función de verificación garantiza que los datos transmitidos sean correctos. En comparación con otros protocolos de comunicación similares,

el protocolo BISS

tiene ventajas en cuanto a compatibilidad y estructura de red.

Tiene más ventajas en términos de alta velocidad y retardo que

SSI

, y la velocidad de comunicación puede alcanzar hasta

10 Mbps

. Al mismo tiempo,

BISS

La longitud de los datos del protocolo se puede modificar según la situación real y tiene buena escalabilidad.

El

protocolo BISS tiene dos modos de trabajo

[43]

El modo de trabajo diseñado en este artículo es el modo sensor y

el

FPGA

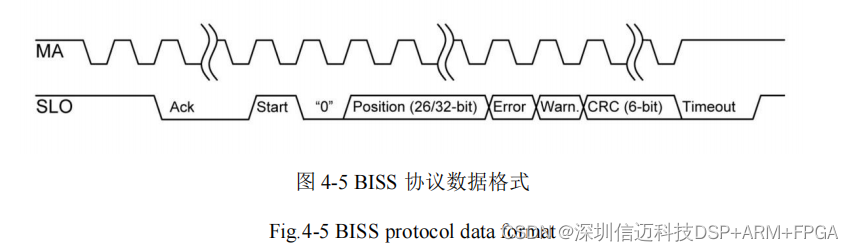

El codificador envía un comando de solicitud de posición y el codificador devuelve información relevante. En modo sensor,

datos

BISS-C

El formato se muestra en la Figura

4-5 a continuación

. El host envía

la señal del reloj MA

a la escala de rejilla y el codificador serializa a través de la

línea de datos

SLO

Devolver información de datos.

La trama de datos BISS-C consta de ocho partes, que son la fase de respuesta "Ack" , el bit "Inicio" , el bit "0",

Varios bits de datos de posición, un bit de error, un bit de advertencia, seis códigos de verificación

CRC

y

el resultado del tiempo de espera

"Timeout"

Etapa final. El ciclo de solicitud de comunicación específico es el siguiente

[44]

:

(

1 ) Cuando no es una solicitud de posición, la señal del reloj está en un nivel alto y

la línea de datos SLO

del host que lee el codificador

está en un nivel alto

Normalmente, significa que el codificador está listo.

(

2 ) Cuando el codificador está listo, el host comienza a transmitir la señal de reloj

MA

de frecuencia fija

a la escala de rejilla.

(

3

) El codificador pondrá la

línea SLO en nivel bajo cuando detecte el segundo flanco ascendente del reloj

MA enviado por el maestro.

nivel como respuesta.

(

4

) El codificador avisa al host tirando hacia abajo

de la línea de señal SLO

. El codificador actual está en

el estado de respuesta Ack

y el host

La máquina debe cambiar al estado de recepción a tiempo.

(

5

) El host se sincronizará con

la señal del reloj MA

para recibir el codificador y enviar los datos, y el formato del marco de datos es de bits altos.

El bajo delantero está detrás.

(

6

) Después de recibir todos los datos, el host eleva

la línea del reloj MA

. Cuando el codificador está listo para la siguiente posición

Cuando se solicita, el codificador establece

la línea SLO

en un nivel alto para avisar al host; de lo contrario, permanece bajo.

4.2.2

Diseño del módulo de software

El diagrama de estructura funcional del módulo

BISS se muestra en la Figura

4-6

, que se compone principalmente del

módulo

MA , el módulo

SLO y el módulo CRC .

Las señales del módulo se interpretan de la siguiente manera:

(

1

)

biss_es

: Señal de habilitación del módulo, utilizada para obtener información de posición del codificador.

(2)

longitud_datos

: Configuración del ancho de bits de datos del codificador.

(3)

SLO

:

Línea de datos del protocolo

BISS .

(4)

MA

:

Línea de reloj del protocolo

BISS .

(5)

datos_abs

: Valor absoluto de una sola vuelta, utilizado para el conteo de varias vueltas y el cálculo de ángulos eléctricos de codificadores circulares.

(6)

pos_abs

: Los datos de posición total real del codificador.

El principio de funcionamiento específico de este módulo es el siguiente: primero,

la FPGA

establece el ancho de bits de los datos de posición de acuerdo con el modelo de escala de red real

Valor data_lentgh

, este módulo cumple con el requisito de diseño de que la longitud del ancho de bits de los datos de posición esté dentro de

32 bits

. A través del módulo de control principal

Envíe la señal de habilitación

biss_en

al módulo

MA

,

el módulo de reloj MA

comienza a funcionar y envía una frecuencia fija a la regla de rejilla

La señal del reloj

MA

solicita obtener el valor de posición actual.

Después de que la FPGA

reciba los datos devueltos por la escala de rejilla, ingresará

Vaya al módulo de verificación

CRC

para verificar los datos y finalmente envíe los datos de posición correctos al módulo del siguiente nivel.

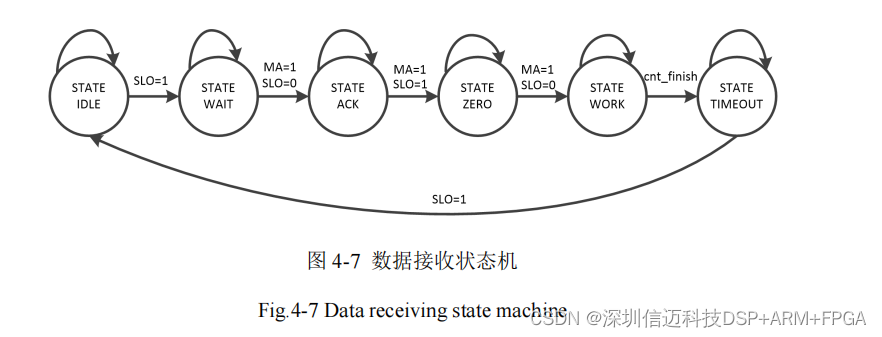

De acuerdo con las características del diagrama de tiempos del protocolo

BISS

, este artículo divide el proceso de recepción de datos por parte del módulo

SLO

en seis estados,

La máquina de estados funciona como se muestra en la Figura

4-7

. Al principio, el módulo de función está en estado inactivo y entra en estado de espera; cuando

Cuando la regla de rejilla baja

la

línea de señal SLO, ingresa al

estado de respuesta

Ack ; cuando

el SLO cambia de nivel bajo a nivel alto, el estado

La máquina de estado ingresa

al

estado STATE_ZERO; cuando se detecta que

la línea de datos SLO

está baja, el módulo ingresa al estado de funcionamiento y comienza

Reciba datos e ingrese al estado "TIMEOUT" después de recibir los datos de ancho de bits establecidos.

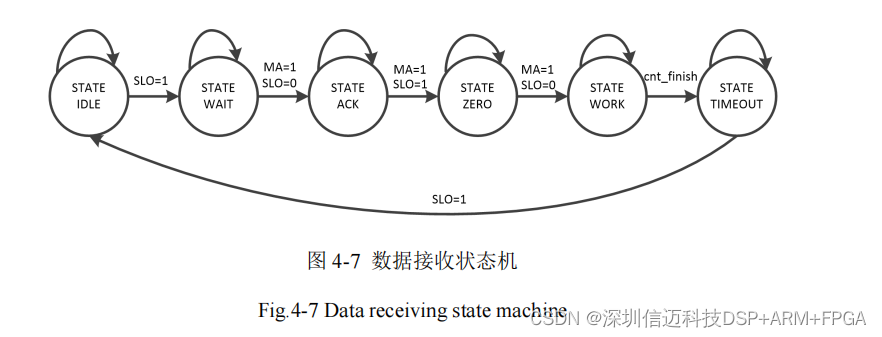

En la ingeniería real, hay fallas o fenómenos metaestables en el nivel de datos, si de acuerdo con

el flanco ascendente del reloj

MA

La señal obtenida al leer el estado de nivel de la línea de datos SLO actual no es confiable.

Generalmente, durante la transmisión

El estado de nivel en el medio de los datos es relativamente estable y confiable. Por lo tanto, el método adoptado en este trabajo es: en la parte media

Muestrear

la línea de datos SLO

varias veces y juzgar qué nivel tiene el número más grande y, finalmente, el valor de la señal de nivel con el número más grande

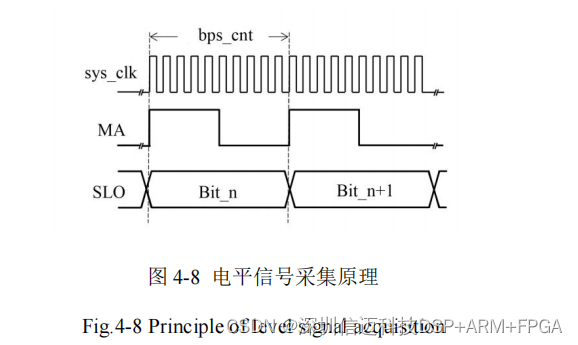

Sentencia asignada al registro. El principio de implementación específico se muestra en la Figura

4-8

, donde

sys_clk

es el reloj del sistema y

bps_cnt

es un

El número de muestras del nivel de línea de datos SLO en un ciclo de reloj

MA .

La frecuencia de reloj MA real se compara con la frecuencia interna de FPGA.

La frecuencia operativa es un reloj de baja velocidad, por lo que se pueden realizar múltiples muestreos en un

ciclo de reloj

MA .

en cada

Durante los ciclos del reloj

MA , cuando

se detecta el flanco ascendente del reloj

MA

,

El registro bps_cnt

comienza a contar muestras desde cero,

Luego juzgue si la cantidad de niveles altos es grande o la cantidad de niveles bajos es grande, y finalmente se acumulará el valor del lado con la mayor cantidad de niveles.

Asignar a un registro. Repita este proceso para recibir todos los datos.

Después de que el módulo

SLO

recibe los datos, devuelve una señal de finalización de recepción al módulo

MA

y al módulo de verificación

CRC

.

modo

MA

Después de que el bloque reciba la señal de finalización,

la FPGA

elevará

la línea de reloj MA

y

el

módulo CRC configurará el

modo

SLO en

La trama de datos transmitida por el bloque está sujeta a la operación de verificación

CRC

.

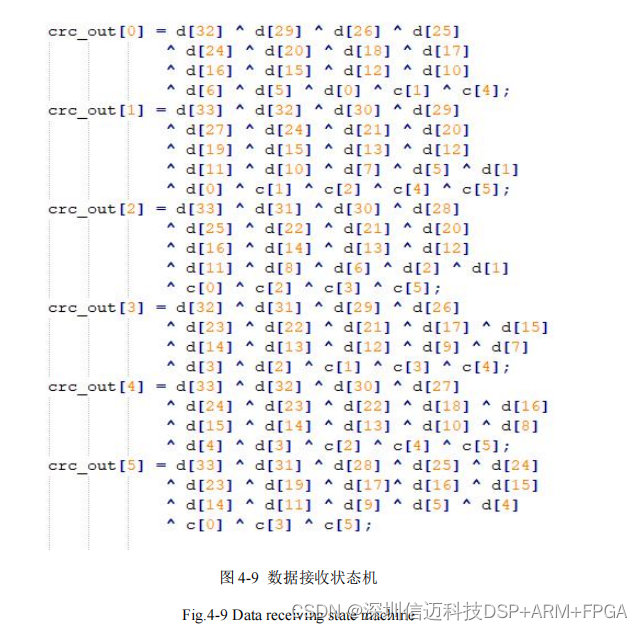

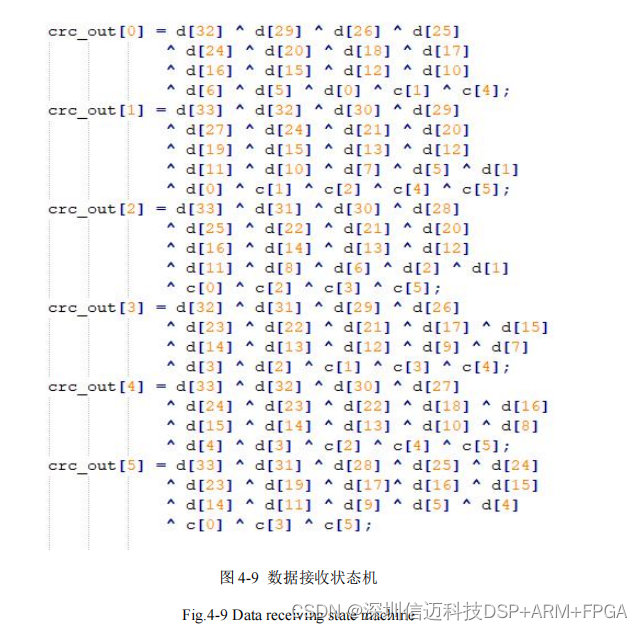

El polinomio CRC del protocolo

BISS-C es

G ( x ) x 6 x 1 ,

Es decir, el campo de verificación es

1000011

. Para aprovechar al máximo las características de trabajo del procesamiento paralelo

FPGA

y mejorar aún más la eficiencia del trabajo

velocidad, este artículo utiliza un algoritmo de verificación

CRC paralelo

para obtener el código de verificación

CRC

en un ciclo de reloj, el código principal

Como se muestra en la Figura 4-9:

Entre ellos,

d [33:0]

son los datos que deben verificarse y

crc_out [5:0]

es

la operación del módulo

CRC en los datos que deben verificarse.

El resultado obtenido después del cálculo, el valor inicial de

c[5:0]

es cero y finalmente el resultado del cálculo se compara con el

código de verificación

CRC recibido.

coincidencias de línea. Si los dos son consistentes, significa que el módulo

SLO

recibe los datos correctamente y actualiza los datos de posición correctos para

En el módulo del siguiente nivel, de lo contrario, actualice los datos correctos reservados la última vez y prepárese para iniciar la siguiente solicitud de posición del ráster.

4.2.3

Prueba de simulación

Finalmente, escriba un archivo de prueba para

simular y verificar el módulo

BISS

en el software

ModelSim y aplicarlo en ingeniería real.

La estabilidad juega un papel importante.

Por lo tanto, se seleccionan los 5 Mbps más altos

en términos de velocidad de comunicación

, por lo que el modelo en el archivo de prueba

El codificador virtual transmite datos a

la FPGA a una velocidad de comunicación de

5 Mbps

. Este artículo es para posiciones de 26 y 32 bits de uso común.

Se prueban los modelos de codificadores de ancho de bits de datos.

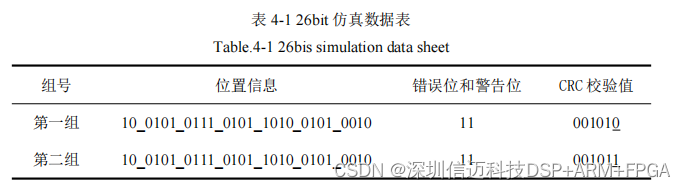

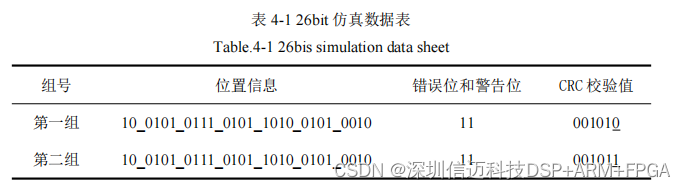

Primero, configure dos conjuntos de datos para modelos

de 26 bits de ancho como

se muestra en la Tabla 4-1, donde el primer conjunto y el segundo conjunto de datos son solo

Sólo el último bit del código de verificación

CRC

es diferente y el segundo conjunto de datos es completamente correcto. A través de este artificial

Los datos establecidos pueden probar

si los dos conjuntos de información de datos recibidos por el módulo

BISS son consistentes y también detectar el

modo de verificación CRC.

bloque para que funcione correctamente. Cabe señalar que

el valor de verificación CRC del protocolo

BISS-C

es el primero

Se envía al host mediante inversión, por lo que

el valor de verificación CRC

en la tabla se ha invertido. así que haz una combinación

Al comparar y verificar,

la FPGA

debe invertir el valor de verificación

CRC calculado

y compararlo con el valor recibido. El conjunto

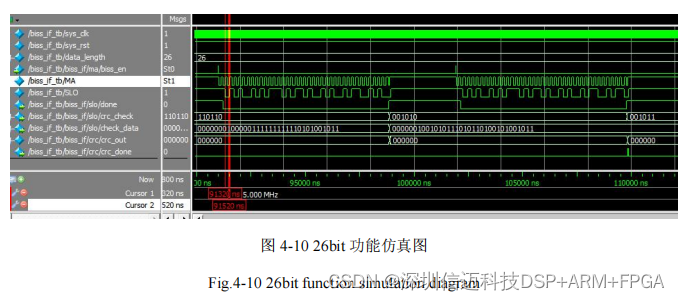

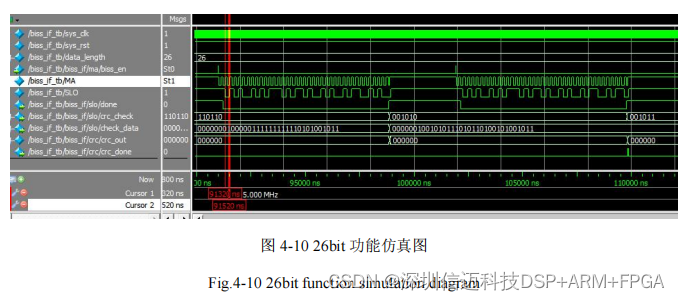

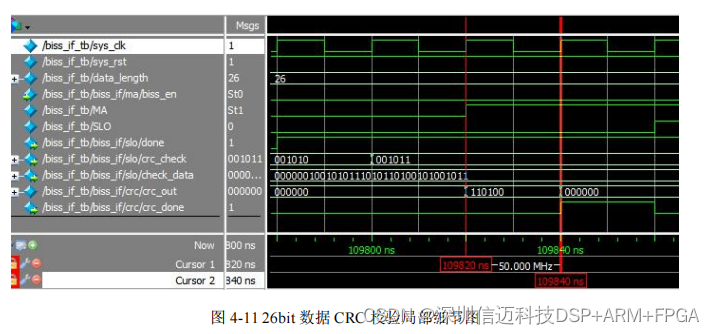

Los resultados de la prueba corporal se muestran en la Figura 4-10.

El diagrama de tiempo del lado izquierdo de la figura es el primer conjunto de datos, mientras que el de la derecha es el segundo conjunto de datos. En la figura,

crc_check

está recibiendo

Valor CRC , check_data son los datos a verificar, done es la señal de finalización de recepción de datos, crc_out

es

la verificación

El

valor

CRC calculado,

crc_done, significa que la verificación está completa, es decir, los datos recibidos son correctos. Se puede ver en la imagen.

En el modo de datos donde

data_length

es

de 26 bits

, después de que el módulo recibe la

señal de habilitación

biss_en ,

la FPGA envía el

El codificador envía una señal de reloj

MA con una frecuencia de

5MHz

. El codificador pasa los datos SLO después de detectar la señal del reloj MA .

La línea devuelve datos al host y cuando

la

FPGA

termina de recibir los datos,

transmite el valor de verificación

CRC recibido

y

Es necesario verificar los datos y

se envía una señal de finalización para que

el módulo

CRC funcione. Entonces el módulo CRC necesita verificar el

Los datos verificados se procesan y, después del procesamiento , se comparan con el valor de verificación

CRC recibido, si los dos coinciden correctamente.

Luego se genera una señal de marca exitosa

crc_done con un pulso de nivel alto

; de lo contrario, la señal crc_done permanece baja.

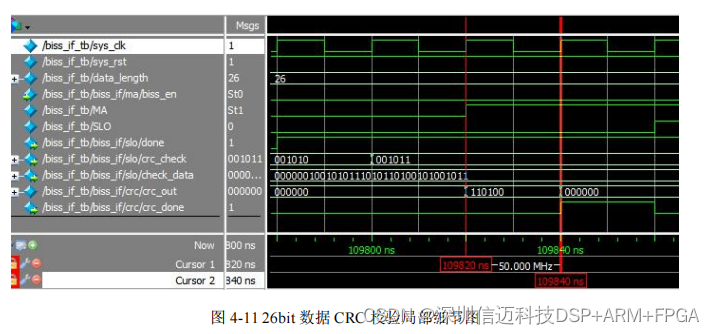

Verifique más a fondo

los detalles de la verificación

CRC , como se muestra en la Figura

4-11 . El valor de verificación CRC recibido crc_check en la figura

es

001011

y

crc_out es 110100 después de realizar la verificación

CRC en los datos que se van a verificar

. sección anterior también

Hablando de eso, el valor de verificación CRC

del codificador

primero se invierte y se envía al host, y los datos obtenidos después de la operación de verificación

crc_check

no está invertido, por lo que se puede ver que es consistente con el valor de verificación

CRC recibido

después de la inversión. También se puede ver en la figura.

El tiempo requerido para la verificación

CRC

es un ciclo de reloj del sistema, por lo que se puede concluir que el módulo de verificación CRC puede funcionar normalmente.

De los dos diagramas de resultados de simulación anteriores, se puede ver que

cuando el módulo

BISS

normalmente puede enviar MA a una velocidad de comunicación de 5 Mbps

La señal del reloj y los datos del codificador se reciben por completo y, finalmente,

la operación de verificación CRC

se completa en un ciclo de reloj. Por lo tanto todos

El módulo

BISS diseñado

ha pasado la prueba de simulación de función en modo

de 26 bits

.

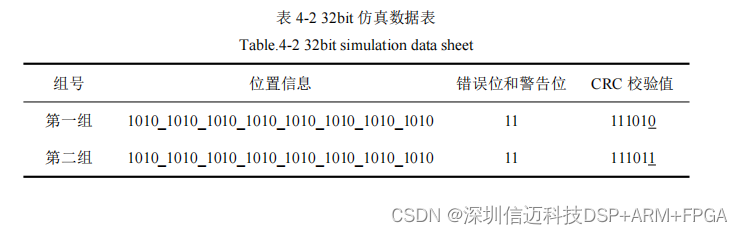

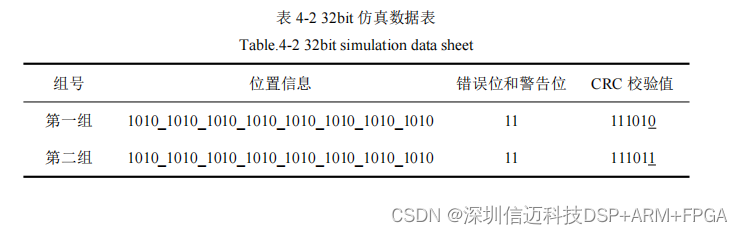

De manera similar, se establece la prueba de simulación del modelo

de 32 bits de ancho

, y el conjunto de datos de simulación se muestra en la Tabla

4-2

, y la simulación de función

Las Figuras 4-12 y 4-13 muestran la imagen real y los detalles de la verificación

CRC

. Se puede ver en la figura que el módulo BISS diseñado también es

Pasó la prueba de simulación de función en modo de 32 bits.

Por lo tanto, se puede concluir que el módulo BISS

diseñado en este trabajo

puede cambiar

el

registro data_lentgh para poder

Comunicación de 5 Mbps

para recibir completamente

los datos del codificador con un ancho de bits de datos de

32 bits .

4.3

Diseño del programa del protocolo Tamagawa

4.3.1

Estructura de datos del protocolo Tamagawa

El acuerdo de Tamagawa proviene de la Corporación Tamagawa de Japón y utiliza un método de comunicación de "una pregunta, una respuesta".

De esta manera, el host envía diferentes comandos de solicitud al codificador para obtener información de datos diferente

[45]

. Se comunica con una cuerda.

La comunicación del puerto es consistente y al enviar un byte de datos , se transmitirá desde el bit bajo a una velocidad de transmisión fija de

2,5 Mbps .

Este artículo solo se centra en el modo de funcionamiento del protocolo Tamagawa para leer la información del codificador.

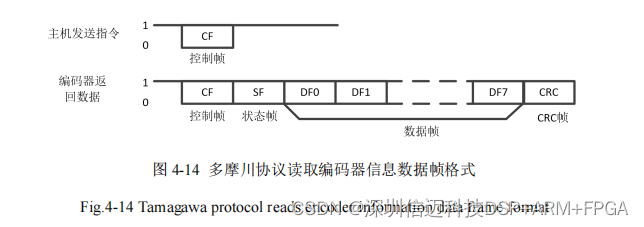

El formato del marco de datos para leer el modo de información del codificador se

muestra en la Figura 4-14. Su principio de funcionamiento es: el host envía

Se dan diferentes comandos del marco de control al codificador para obtener la información correspondiente y luego el codificador devuelve un conjunto de datos como respuesta.

Este grupo de datos consta de marcos de control, marcos de estado, varios marcos de datos y

marcos

CRC .

Entre ellos, según los diferentes modelos de codificador,

La cantidad de marcos de datos variará.

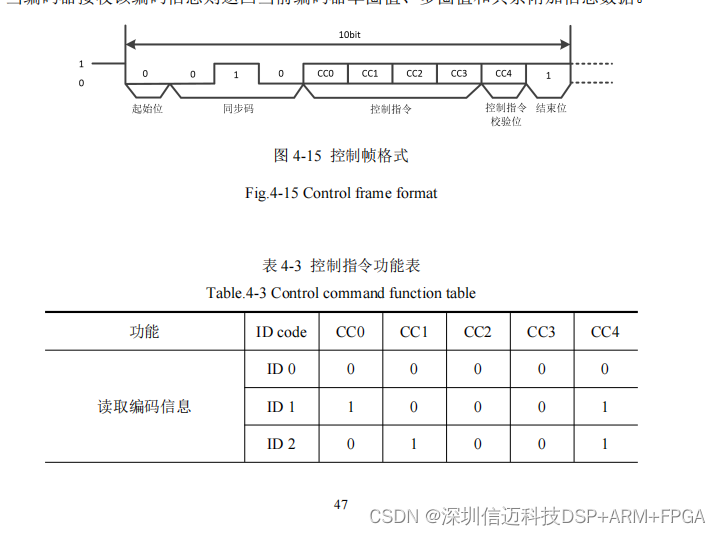

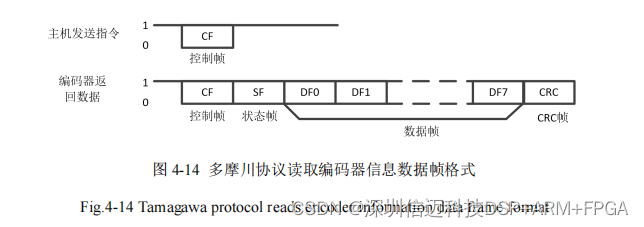

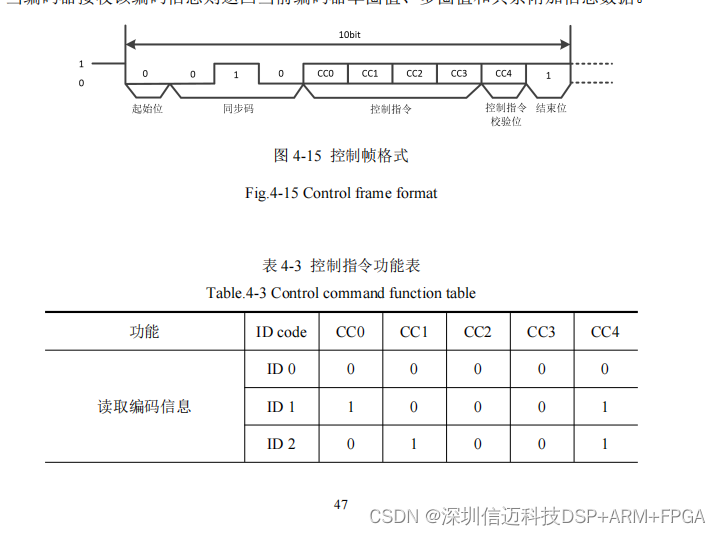

El formato de datos del marco de control se muestra en la Figura

4-15

. La parte del sujeto de datos del marco consta de código de sincronización, instrucción de control y control.

El dígito de control de instrucciones consta de tres partes. Entre ellos, el código de sincronización es fijo, mientras que el comando de control y su dígito de control tienen características específicas.

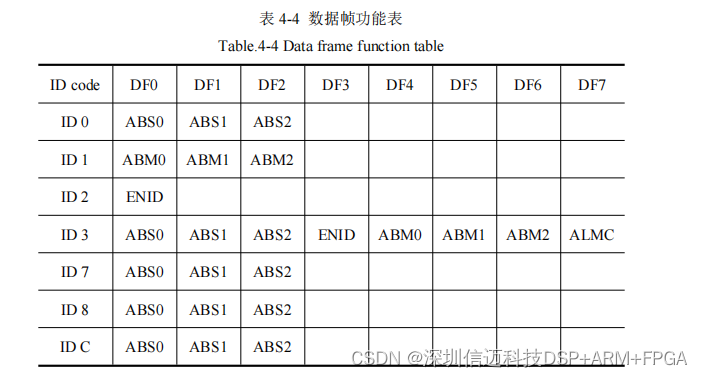

código de comando, como se muestra en la Tabla

4-3

. Diferentes códigos de instrucción representan diferentes funciones y los tipos de datos devueltos por el codificador también son

diferente. Por ejemplo, si el usuario desea obtener el valor de una sola vuelta y el valor de varias vueltas del codificador, consulte la Tabla

4-4

para saber que la

instrucción numerada

ID 3

El código corresponde al codificador que devuelve un valor de una sola vuelta y un valor de varias vueltas, por lo que el host puede enviar el código al codificador como:

01011000

,

Cuando el codificador recibe la información codificada, devuelve el valor de una sola vuelta del codificador actual, el valor de varias vueltas y otros datos de información adicional.

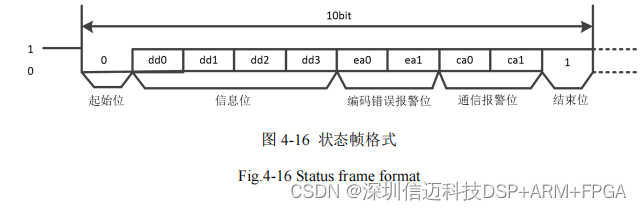

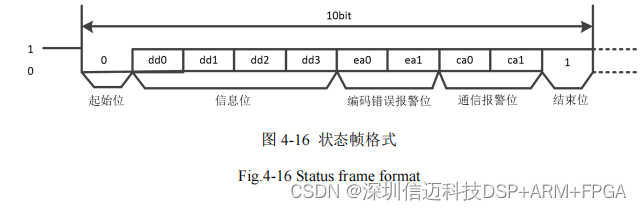

El formato de datos del marco de estado se muestra en la Figura

4-16

, que consta de bits de información, bits de alarma de error de codificación y bits de alarma de comunicación.

Diferentes modelos de codificador corresponden a diferentes bits de información. Para significados específicos, consulte el manual del codificador correspondiente.

introducir. Si el código del codificador es incorrecto o hay un problema con la fuente de alimentación externa del codificador, el bit de alarma de error del codificador

ea0

Si es

1

, significa que la información de codificación actual es incorrecta, y cuando

ea1

es

1

, los datos del valor de múltiples vueltas del codificador son incorrectos. Bit de alarma de comunicación

Cuando ca0

es

1

, significa que el bit de verificación del comando de control en la trama de control recibida tiene un error, mientras que

ca1

es

1

, significa que todos

Se produjo un error en el bit final de la trama de control recibida.

El codificador absoluto Tamagawa puede realizar datos de codificación de posición de alta resolución con un ancho de bits de hasta

39 bits

, incluidos

Valor de una sola vuelta de 23 bits

y

valor de múltiples vueltas

de 16 bits .

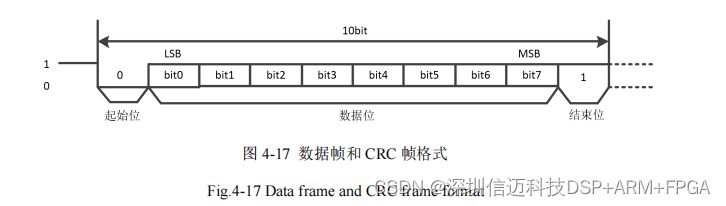

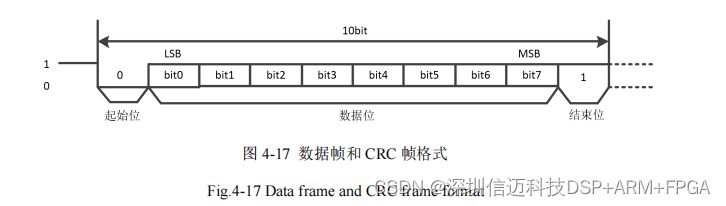

Pero la comunicación con el protocolo Tamagawa solo envía datos

de 8 bits

a la vez, así que envíe

Para enviar información de ubicación completa, se debe desmontar y luego enviar en un orden determinado. Un byte de datos específico

El formato de trama y el formato de trama

CRC

se muestran en la Figura 4-17.

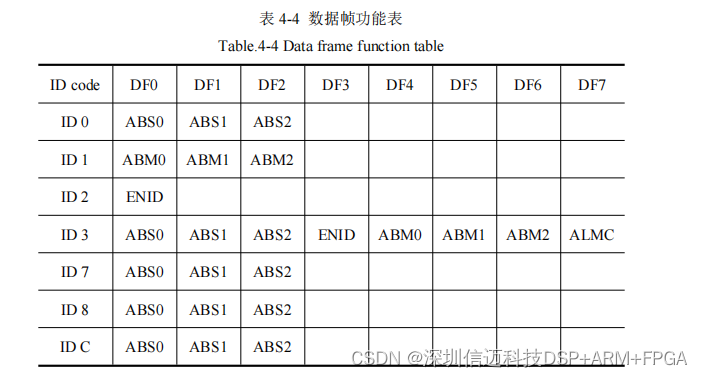

Dado que el host envía diferentes códigos de comando al codificador, los tipos de datos devueltos por el codificador también son diferentes. Según codificador

Con diferentes resoluciones y códigos de comando, el número de tramas de datos efectivas devueltas por el codificador también es diferente. Por ejemplo, solo se puede obtener el valor de una vuelta.

o valor de múltiples vueltas, devuelva un marco de datos válido de

3 bytes y devuelva

8

si necesita obtener tanto el valor de una sola vuelta como el valor de múltiples vueltas

Un marco de datos válido de bytes. El marco de datos correspondiente al código de función específico se muestra en la Tabla 4-4.

En la tabla,

ABS

representa el valor de código absoluto de una sola vuelta,

ABS0

son los ocho bits inferiores de los datos de posición de una sola vuelta y

ABS1

es la posición de una sola vuelta.

Los ocho bits del medio de los datos,

ABS2

son los ocho bits superiores de los datos de posición de una sola vuelta, si el número de valores de código de una sola vuelta del codificador es inferior a

24 bits

, los bits altos se rellenan con

0

. De manera similar,

ABM

representa el valor del código absoluto de múltiples vueltas,

ABM0

son los ocho bits inferiores de los datos del valor de vuelta,

ABM1

Son los ocho bits del medio de los datos del valor del círculo y

ABM2

son los ocho bits superiores de los datos del valor del círculo. Si el número de valores de código de múltiples vueltas del codificador es menor que

Para 24 bits

, los bits altos se rellenan con

0

. Entonces, para un codificador de alta precisión, el codificador combinará el valor de una sola vuelta de varios bits y el valor de varias vueltas.

Cada valor se divide en

3

bytes de datos y luego se envía secuencialmente desde los ocho bits inferiores hasta que se completa el envío.