Este capítulo presenta primero la situación general del sistema

PLC existente

y luego presenta el controlador industrial general diseñado en este documento.

La arquitectura general de la solución, analiza las funciones que deben realizarse en el hardware y el software, y finalmente analiza las funciones de cada parte y propone

planes de implementación específicos.

2.1

Introducción al sistema PLC

El controlador lógico programable (

controlador lógico programable

,

PLC

) se basa en el microprocesador,

Un nuevo tipo de control automático universal desarrollado combinando tecnología informática, tecnología de control automático y tecnología de comunicación.

dispositivo

[14]

. Utiliza un tipo de memoria programable para su almacenamiento interno de programas, ejecución de operaciones lógicas, control de secuencia,

Instrucciones orientadas al usuario, como

sincronización, conteo y operaciones aritméticas, y

control de varios tipos de

El proceso mecánico o de producción es la parte central del control industrial

[15]

.

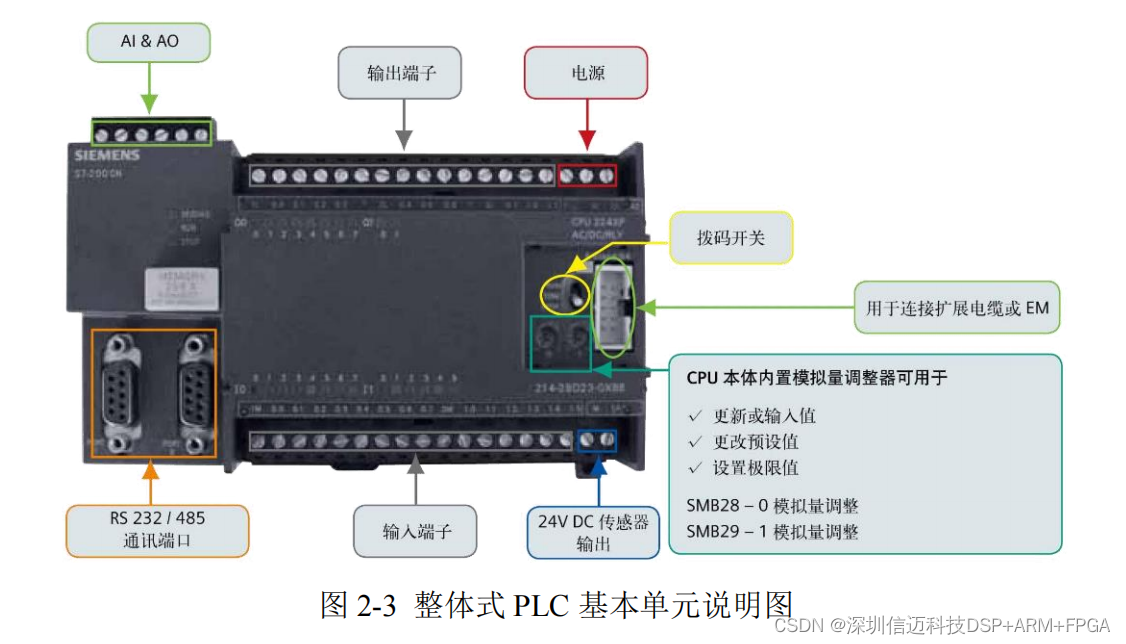

El PLC de la serie Siemens

S7-200

es un PLC integral y la Figura 2-4 muestra el interior de una de las unidades básicas del PLC .

Diagrama estructural, su estructura se compone de tres partes: la parte superior es la placa central o

CPU

, que incluye el interruptor de dial, unidad de expansión

interfaz; la parte central es la placa de interfaz, que incluye la interfaz

de E/S

, la interfaz de comunicación

RS485

, la interfaz de entrada de alimentación

de 220 V

CA,

Interfaz de salida de alimentación de 24 V

CC, etc.; la parte inferior es la placa de alimentación conmutada, entrada

de 220 V

CA, salida de 24 V CC.

2.1.3 Sistema de software PLC

El software PLC

incluye programas del sistema y programas de usuario. El programa del sistema se solidifica dentro del chip de la CPU.

El usuario no puede modificar directamente el programa y el programa del sistema incluye detección de estado anormal y operación de la unidad

de E/S

.

Operación, ejecución del programa de usuario, comunicación con el mundo exterior y otras funciones. El usuario utiliza el programa de usuario para que coincida con el

controlador

PLC.

El programa desarrollado por el software de desarrollo, el lenguaje de desarrollo más utilizado es el lenguaje de diagrama de escalera (

LD

), además del lenguaje de instrucción.

lenguaje (

IL

), lenguaje de diagrama de bloques de funciones (

FBD

), lenguaje de diagrama de flujo de funciones secuenciales (

SFC

), lenguaje de texto estructurado (

ST

).

Para el usuario, no es necesario comprender el programa del sistema en detalle, solo necesita escribir el programa de usuario de acuerdo con los requisitos de producción reales para realizar la lógica.

El control de edición puede ser

[28]

.

Muchos bloques de funciones ya preparados se utilizan a menudo al editar diagramas de escalera, como módulos de temporizador, módulos de contador, alta velocidad.

Módulo contador, módulo de entrada analógica, módulo de salida analógica, módulo

PID

, módulo de comunicación y otros bloques funcionales, estos

El proceso de realización de los bloques de funciones está incluido en el programa del sistema y el programa de usuario solo llama a estos bloques de funciones cuando utiliza estos bloques de funciones.

Proceso de implementación

[29]

.

2.2

Arquitectura general del programa

Este artículo adopta la estructura

PLC integral

, como se muestra en la Figura

2-7

, la estructura general se divide en el controlador principal y el módulo remoto, el principal

El controlador se compone de una placa central, una placa de interfaz, una fuente de alimentación conmutada, una unidad de procesamiento central integrada (

CPU

), una unidad

de E/S

y una fuente de alimentación.

En uno. Como módulo de expansión, el módulo remoto se utiliza en sitios industriales con área grande y amplio rango, de modo que el controlador principal necesita

Para controlar dispositivos de campo a larga distancia, al mismo tiempo, se puede aumentar el número de puntos de

E/S para el controlador principal

, de modo que el controlador se pueda extender a una gran distancia.

y acercarse en la dirección de la modernización y la multifuncionalidad. El módulo remoto incluye principalmente módulo de entrada digital (

DI

), módulo de salida digital (

DO

),

Módulo de entrada analógica (

AI

), módulo de salida analógica (

AO

) y módulo de comunicación Ethernet (

EN

), entre los cuales Ethernet

El módulo de comunicación es el principal responsable de comunicarse con el controlador principal, enviando el estado y los datos de cada módulo remoto al controlador principal y

Reciba comandos de control del controlador maestro.

El controlador diseñado en este artículo realiza principalmente las siguientes estructuras y funciones:

En términos de hardware: la placa PCB

de hardware

debe incluir la placa central, la placa de interfaz, la fuente de alimentación conmutada, el módulo de comunicación Ethernet y el módulo digital.

Módulo de entrada de cantidad de palabras, módulo de salida de cantidad digital, módulo de entrada de cantidad analógica, módulo de salida de cantidad analógica. La placa de interfaz necesita paquete

Incluye interfaz de entrada y salida digital, interfaz de entrada y salida analógica, interfaz de entrada y salida digital de alta velocidad,

USB de alta velocidad

Interfaz de comunicación, interfaz de comunicación

RS485

, interfaz de comunicación Ethernet, etc.

Software: protocolo de comunicación

Modbus

, como protocolo de datos cuando el controlador principal se comunica con el módulo remoto;

El protocolo de comunicación interno del módulo se utiliza como protocolo de datos para la comunicación entre módulos remotos. Diseñar funciones de control modulares,

Incluyendo el control de movimiento y el control de procesos que se utilizan a menudo en sitios industriales, y el algoritmo de control

PID

se utilizará al mismo tiempo, si es necesario.

Para accionar un convertidor de frecuencia o un inversor

también se utilizará

el algoritmo SPWM

y el algoritmo

SVPWM .

Diseño de un contador de alta velocidad

Módulo para adquirir señales de sensores como codificadores rotativos. Diseñe la interfaz de interacción persona-computadora, que sea conveniente para que la operen los trabajadores en el sitio.

controlador. Diseñar el lenguaje de programación del programa de usuario, como puente entre el lenguaje natural humano y el lenguaje de programación del chip subyacente,

Es conveniente para los trabajadores comunes y corrientes sin ninguna base en lenguajes de programación realizar programación y pruebas en el sitio.

2.3

Diseño del esquema del controlador principal

El diseño del esquema general del controlador principal se muestra en la Figura

2-8

, que se divide en placa central, placa de interfaz y fuente de alimentación conmutada.

Symmet proporciona soluciones de control de movimiento STM32+FPGA.

Casi todas las interfaces externas del controlador principal están diseñadas en la placa de interfaz, solo está diseñada la interfaz conectada al módulo de expansión local.

Cuente con el tablero central.

Debido al volumen limitado del controlador principal, el número de interfaces y puntos

de E/S

incluidos son limitados, como

Si se necesitan más puntos

de E/S

, la interfaz Ethernet debe conectarse al módulo remoto para su uso. La interfaz externa del controlador principal incluye

16

Interfaz de entrada digital de 16 vías,

interfaz de salida digital

de 16 vías (salida de relé),

interfaz de salida digital de alta velocidad de 8 vías (cristal

Salida del tubo del cuerpo),

interfaz de entrada de alimentación

de 220 V CA, interfaz de salida de alimentación

de 24 V CC, interfaz de comunicación USB de alta velocidad ,

Interfaz de comunicación RS485

, interfaz de comunicación Ethernet. Dentro del controlador principal, la fuente de alimentación conmutada está conectada a la placa de interfaz y la placa de interfaz

Introduzca la entrada de alimentación

de 220 V CA desde

el exterior a la placa de la fuente de alimentación conmutada y luego se estabilizará después de pasar a través de la fuente de alimentación conmutada.

Una fuente de alimentación fija

de 24V DC.

La placa de interfaz está conectada a la placa central, una es de

5 V y se obtiene reduciendo

24 V

a través de

CC/CC.

La energía se transmite a la placa central y la segunda es transmitir señales

de E/S

y comunicación del puerto serie con el chip de control en la placa central.

2.3.1

Diseño del esquema del tablero central

La estructura de hardware de la placa central incluye un circuito de chip de control, un circuito de descarga, un circuito de oscilador de cristal, un circuito de reinicio y una fuente de alimentación del chip.

circuito,

circuito de comunicación

RS485 , circuito de selección de estado, circuito de indicación de estado,

circuito de indicación de E/S , circuito de conversión de nivel

esperar.

El chip de control se controla mediante el método actualmente popular "

MCU+FPGA "

[32] . MCU es un microcontrolador

Unidad (

Micro Controller Unit

), también conocida como microcomputadora de un solo chip o microcomputadora de un solo chip, es la unidad central de procesamiento, memoria,

Contador,

USB

,

conversión

A/D ,

UART , PWM , DMA y otras interfaces periféricas están integradas en un chip para formar

Las computadoras a nivel de chip se utilizan en campos de control como teléfonos móviles, controles remotos, automóviles y brazos robóticos.

Los FPGA

son programables en campo

Matriz de puertas (

Field Programmable Gate Array

), que es un circuito semipersonalizado en ASIC, generalmente

La matriz de puertas lógicas de bajo nivel se combina mediante programación para realizar

la conexión entre los módulos internos y

las E/S .

FPGA

tiene las siguientes ventajas: alto paralelismo, puede admitir múltiples módulos para realizar cálculos independientes al mismo tiempo; se puede personalizar, es decir,

Realice su propio circuito lógico a través de la programación y se puede programar infinitamente; la velocidad de operación es rápida y la tarea generalmente está en

La ejecución en hardware es más rápida que la ejecución en software. Por ejemplo, comparando

el tamaño de

64 bits,

32 bits

alto

y 32 bits bajo, la CPU

Lo siguiente requiere

2

instrucciones de número de área, dos instrucciones de bits y, una instrucción de desplazamiento, una instrucción de comparación y una instrucción de reescritura, y

Según

la FPGA,

sólo se requiere un comparador.

Al mismo tiempo,

FPGA también tiene desventajas: todas las funciones dependen de la implementación del hardware.

Ahora, operaciones como condiciones de bifurcación y saltos no se pueden realizar y, al mismo tiempo , hay pocos periféricos como conversión

A/D ,

flash , etc., que simplemente se pueden realizar.

Suficiente para confiar en

MCU

para compensar. Por lo tanto, este artículo utiliza la combinación de

MCU

y

FPGA

para maximizar las ventajas de ambos.

Autoventaja

[33]

.

La MCU elige

el microcontrolador STM32 de 32 bits

desarrollado por STMicroelectronics , que se basa en

ARM

El microcontrolador integrado con núcleo de procesador Cortex-M

tiene las características de alta integración y bajo consumo de energía.

selección

de FPGA

Los chips de la serie Cyclone IV

de

ALTERA , que se basan en Cyclone , CycloneII y CycloneIII

Basado en la mejora del rendimiento y la reducción de costes.

STM32

utiliza sus propios periféricos ricos como chip de control principal, utilizando

UART

Comunicarse con el mundo exterior;

FPGA

procesa señales de E/S

utilizando las características de velocidad informática rápida y buena concurrencia .

STM32

Los métodos de comunicación con

FPGA

incluyen comunicación en serie, comunicación paralela y comunicación de memoria compartida. Botas necesarias para la comunicación en serie

Hay menos pines, pero la velocidad no es tan rápida como la de los otros dos métodos de comunicación; el método de comunicación de memoria compartida es más complicado en el circuito de hardware.

Generalmente se usa en ocasiones con una gran cantidad de intercambio de datos, y es un poco excesivo usarlo aquí; aunque la comunicación paralela ocupa más pines,

Pero la eficiencia de la comunicación es alta

[34]

. En general, elija el método de comunicación paralela.

El circuito de alimentación debe determinarse de acuerdo con el voltaje requerido por el chip de control. El chip de control

STM32

seleccionado en la placa central

El modelo específico es

STM32F103ZET6

, el voltaje de funcionamiento es

3,3 V

, el modelo específico de

FPGA

es

EP4CE6E22C8

,

Los voltajes de funcionamiento son

3,3 V

,

2,5 V

y

1,2

V.

Los métodos de descarga de STM32

incluyen los métodos

SWD

y

JTAG

. El modo

SWD

es más eficiente que

JTAG

en el modo de alta velocidad.

Más confiable, el

programa de descarga JTAG fallará

en el caso de una gran cantidad de datos , pero la probabilidad de

SWD será muy pequeña

Muchos, y

la cantidad de pines requeridos por

SWD es pequeña, lo que puede ahorrar espacio

en la PCB . Aunque STM32 tiene cristal interno de 8MHz

Oscilación, pero la precisión no es tan alta como la del oscilador de cristal de alta velocidad con configuración externa. Hay dos tipos de osciladores de cristal externos: oscilador de cristal de alta velocidad y oscilador de cristal de baja velocidad.

El oscilador de cristal de baja velocidad típico es de

32,768 KHz

, y el oscilador de cristal de alta velocidad se puede seleccionar entre

4 ~ 32 MHz

, y luego se puede configurar mediante el bucle de bloqueo de fase.

La frecuencia principal se eleva a

72MHz

. La interfaz del módulo de expansión que debe reservarse en la placa central se utiliza para conectar varios módulos de expansión.

El método de comunicación entre los módulos de expansión aquí elige la comunicación

RS485

, porque

RS485

admite un modo maestro y múltiples modos esclavo. al mismo tiempo

Es necesario diseñar un circuito de selección de estado y un circuito de indicación de estado alrededor de STM32

. El circuito de selección de estado utiliza un interruptor de dial como

La entrada de pin de STM32

, el circuito de indicación de estado utiliza

LED

como salida de pin de

STM32

.

FPGA

no tiene

flash en el chip

, por lo que los programas

FPGA

deben almacenarse en

un flash fuera del chip

, seleccione aquí

EPCS4SI8N

se utiliza como

flash fuera del chip de

FPGA

. Los métodos de descarga de FPGA incluyen el modo JTAG , el modo AS y PS

modelo.

En modo AS

, el programa se graba en el chip de configuración

EPCS

y cada vez que

se enciende

la FPGA , actúa como un controlador desde el chip de configuración.

Configure el chip

EPCS

para leer datos; el modo

PS

es usar

EPCS

como dispositivo de control, usar

FPGA

como memoria y

FPGA

Cuando se enciende,

EPCS

escribirá datos activamente en

FPGA

, este modo puede realizar

la programación en línea de

FPGA ;

El modo JTAG

es el modo más utilizado y graba directamente el programa en

la SRAM de

la FPGA

, por lo que después de un corte de energía

La secuencia desaparecerá.

Cuando la FPGA

funciona normalmente, sus datos de configuración se almacenan en

la SRAM

y deben descargarse nuevamente cuando se enciende.

En el sistema experimental, generalmente se usa una computadora o un controlador para la depuración, por lo que se puede usar

PS

. Pero en el sistema práctico

En la mayoría de los casos,

el proceso de operación de configuración debe ser guiado activamente por

la FPGA . En este momento,

la FPGA participará activamente

Los datos de configuración se obtienen del chip de almacenamiento y

la información de configuración FPGA

en este chip se obtiene utilizando un programador común para diseñar

el .pof.

El archivo de formato se graba a través de

AS

.

Grabar el archivo .sof a través del modo

JTAG

grabará el programa en la SRAM ,

Sin embargo, a través de la conversión de archivos,

el

archivo .sof se convierte en

un

archivo .jic y

el programa pasará a través de la FPGA mediante la grabación en modo

JTAG .

Se solidifica en el chip de configuración

EPCS

, de modo que

la FPGA

leerá

el programa

del EPCS cuando se vuelva a encender.

El examen final de este artículo.

Considerando la conveniencia de la depuración, elegimos

el modo JTAG

.

La frecuencia principal de la FPGA

necesita un oscilador de cristal externo, y

el STM32

tiene un circuito de inicio del oscilador de cristal en el interior, por lo que se puede utilizar un oscilador de cristal pasivo.

Pero

FPGA

no lo tiene, por lo que

FPGA

solo se puede conectar con un oscilador de cristal activo, aquí elija

50 MHz

como fuente de reloj

FPGA

.

Se puede obtener un reloj de hasta 300 MHz

multiplicando la frecuencia del bucle de bloqueo de fase

.

Los pines FPGA

se pueden configurar como modo de entrada o modo de salida, todos los cuales son

señales

3.3VTTL .

Los

pines de entrada y salida de FPGA controlan directamente

los LED

como

luces indicadoras

de E/S , un total de

40 , 16 puntos de entrada, 16 de salida.

Punto de salida,

8

puntos de salida de alta velocidad. La placa central y la placa de interfaz están conectadas entre sí a través de conectores para transmitir señales de datos de puntos

de E/S

.

No., entre

el FPGA

y el conector también se conecta un chip de conversión de nivel, entre la señal

3.3VTTL

y la

señal

5VTTL

La interconversión y el chip de conversión de nivel pueden desempeñar un papel protector para evitar que los pines

FPGA

se conecten directamente al exterior

[35]

.

2.3.2

Diseño del esquema de la placa de interfaz

La estructura de hardware de la placa de interfaz incluye un circuito de entrada de optoacoplador, un circuito de salida de relé, un circuito de salida de transistor y

RS485.

Circuito de comunicación, circuito de comunicación

USB

, módulo de comunicación Ethernet,

circuito reductor

CC/CC , placa central y placa de alimentación.

circuito de interfaz, etc.

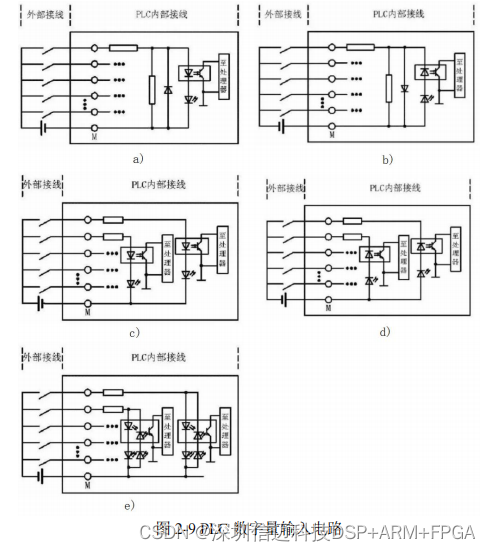

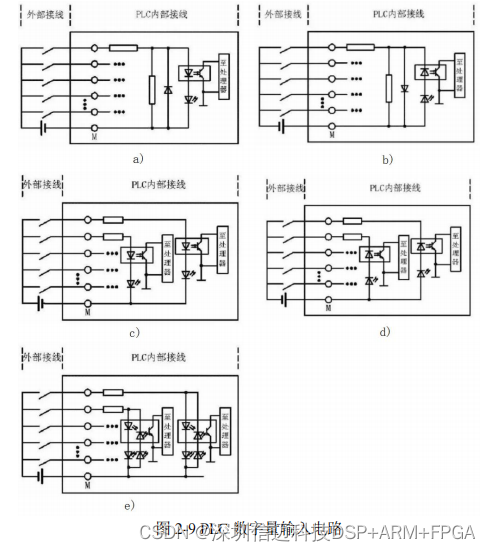

El circuito de entrada del optoacoplador se utiliza para ingresar la señal del interruptor externo. Generalmente,

el módulo de entrada del

PLC consta de varios puntos de entrada.

y una terminal común. Como se muestra

en la Figura

2-9 ,

a) yb ) son dos formas diferentes de circuitos de entrada de CC de PLC , la diferencia es que

Cuando el interruptor externo está cerrado,

la corriente en

a)

sale del PLC (entrada de fuente) desde el terminal común M , y la corriente en b) fluye desde el común

El terminal

M

desemboca en

el PLC

(entrada positiva). Cuando el interruptor está cerrado,

el diodo emisor de luz del optoacoplador dentro

del PLC se enciende y los tres fotosensibles

El tubo polar se satura y se enciende, y luego la señal se envía a la unidad central de procesamiento y se considera que hay una señal de entrada.

c)

y

d) son

a) y b)

respectivamente

Estructura de señal multicanal. Para adaptarse a más dispositivos de campo, este documento utiliza

el circuito de entrada híbrido que se muestra en

e) , optoacoplador

Elija un optoacoplador de entrada bidireccional y la forma del cableado externo puede ser tanto entrada de energía como entrada de sumidero.

2.5

Diseño del esquema de software

2.5.1

Sistema operativo integrado

Aunque las aplicaciones integradas pueden ejecutarse directamente en el chip, para llamar a la multitarea de manera más razonable,

Para aprovechar al máximo los recursos del sistema, este documento adopta

el esquema de trasplantar el sistema operativo integrado en

STM32 .

incrustación utilizada actualmente

Los sistemas operativos integrados incluyen

μClinux

,

μC/OS-II

,

eCos

y

FreeRTOS

.

μClinux

(

micro-control Linux ) es un

Linux

de microcontrol . En comparación con

Linux estándar , el kernel μClinux

Pequeño, pero aún hereda la buena estabilidad y portabilidad

de Linux

, tiene potentes funciones de red y excelente texto.

sistema de software, API

rico en estándares

y

protocolo de red

TCP/IP , etc.

En términos de trasplante, dado que

μClinux

es

Linux

Una mejora dirigida a sistemas embebidos, por lo que su estructura es más complicada y el procesador de destino necesita un externo.

ROM

y

RAM

, para

STM32F103

, trasplantar este sistema requiere al menos

512 KB

de espacio

RAM

,

1 MB

Espacio ROM

/FLASH

, y

STM32F103

solo tiene

256 KB

de

FLASH

, por lo que se requiere una memoria externa,

Esto aumenta los costos de hardware. Además,

μClinux

tiene una estructura compleja, es difícil de trasplantar y tiene un rendimiento deficiente en tiempo real, por lo que no es adecuado como

El esquema de trasplante de este sistema.

μC/OS-II

es

un kernel compacto, preventivo y multitarea en tiempo real escrito en lenguaje

C.

µC/OS-II

Se admiten hasta

64 tareas

, correspondientes a las prioridades

0~63

, donde

0

representa la prioridad más alta,

63

es la más baja y el sistema

Las 4

prioridades más altas y

las 4

prioridades más bajas

están reservadas , por lo que hay

56 tareas disponibles para el usuario

.

µC/OS-II

Puede proporcionar funciones como programación y gestión de tareas, gestión de memoria, sincronización y comunicación entre tareas, gestión del tiempo y servicio de interrupciones, etc.

Tiene las características de alta eficiencia de ejecución, tamaño reducido, excelente rendimiento en tiempo real y gran escalabilidad. En portabilidad,

μC/OS-II

Admite la mayoría de las

CPU más populares actualmente

. Debido a su pequeño núcleo, el código mínimo es de solo

2 KB

y se requiere espacio de datos.

Solo hay

4 KB

de

RAM

, por lo que la portabilidad es relativamente simple, solo es necesario modificar el código relacionado con el procesador, que es más adecuado.

Se puede trasplantar en este sistema juntos.

eCos

(

sistema operativo configurable integrado

) es un sistema operativo configurable integrado, un

El sistema operativo configurable, portátil y en tiempo real de Kaiyuan para aplicaciones profundamente integradas. su característica más importante

Es decir, el núcleo es configurable y la configuración flexible provocada por el método de diseño modular.La parte central se compone de componentes similares.

Los componentes como el kernel, la biblioteca de lenguaje C y los paquetes de tiempo de ejecución subyacentes se pueden configurar fácilmente a través de la herramienta de configuración

eCos y se pueden configurar fácilmente.

Bueno para satisfacer las necesidades de diferentes aplicaciones integradas. En términos de trasplante,

el

núcleo de eCos es pequeño, el código mínimo es de solo

10 KB

y el requerido

El espacio de datos es de solo

10 KB

de

RAM

y la portabilidad es buena, lo cual

es más fácil que

μClinux

y

μC/OS-II , pero

Su aplicación no es extensa y no hay tantos documentos como

μC/OS-II

, y es más adecuado para aplicaciones como la electrónica de consumo.

FreeRTOS

es un sistema operativo en tiempo real que es completamente gratuito y puede

ejecutarse en pequeños microcontroladores

RAM .

Funciones como desarrollo de código, gran portabilidad, adaptabilidad y estrategias de programación flexibles.

El sistema operativo FreeRTOS

puede completar

La gestión de tareas, la gestión del tiempo, el semáforo, la cola de mensajes, la gestión de la memoria, la grabación y otras funciones pueden cumplir con un mínimo

Requisitos básicos del sistema operativo. En términos de portabilidad,

FreeRTOS

se puede portar fácilmente a diferentes procesadores, como

ARM

,

MSP430

,

PIC

,

AVR

,

C8051F

, etc.,

el núcleo de

STM32 es

ARM , por lo que FreeRTOS

Es adecuado para el trasplante de este sistema y también es el sistema operativo integrado adoptado en este artículo.

2.5.2

Sistema de software

Un sistema de software consta de programas del sistema y programas de usuario. El programa del sistema es el programa solidificado en el chip de control.

El controlador se compone de un controlador principal y un módulo remoto. Hay

dos chips de control,

STM32

y

FPGA , en el controlador principal. Hay

5 tipos

Cada uno de los módulos remotos tiene un STM32

como chip de control

para realizar sus respectivas funciones , por lo que es necesario diseñar

7

conjuntos de diferentes

Programa del sistema, el lenguaje de programación incluye

el lenguaje C requerido por

STM32 y el lenguaje

Verilog HDL requerido por FPGA . usar

Edición de programas de usuario Este documento diseña dos conjuntos de soluciones, uno es diseñar un software de programación del lado

de la PC

, que se puede descargar a través del

puerto

USB .

Al flash en el controlador principal

STM32

, y el otro es la función de programación en el sitio, es decir, a través de la interfaz de interacción persona-computadora, usando

Las palabras clave permiten a los usuarios comunes sin conocimientos de programación escribir programas de prueba simples, lo cual es conveniente para la depuración en el sitio

[36][37]

.

2.5.3

Función modular

Este artículo diseña funciones modulares, control de movimiento y control de procesos. El control de movimiento se utiliza a menudo en maquinaria, máquinas herramienta, máquinas.

Robots, control de ascensores y otras ocasiones, utilizados para accionar motores paso a paso, servomotores o motores de CA, en este momento se requiere un controlador

Para generar señales de conducción correspondientes, como la conducción de motores de CA asíncronos, se requieren algoritmos

SPWM

y

SVPWM

para mover simultáneamente

El control a menudo utilizará el codificador para medir la velocidad y la posición. Este documento diseña la función del contador de números altos en el software. proceso

El control se utiliza a menudo en metalurgia, industria química, control de calderas, etc., para el control de circuito cerrado de cantidades analógicas como temperatura, presión y flujo.

Control, en este momento, el controlador necesita implementar el algoritmo

PID

.

2.5.4

Protocolo de comunicación

Cada fabricante

de PLC generalmente tiene su propio protocolo de comunicación, por ejemplo,

el PLC

de Rockwell

admite el protocolo DF1 .

Los PLC

de las

series

90-70

y

90-30 de

GE admiten el protocolo SNP , y los PLC de la serie Siemens S-200 admiten MPI y PPI

El PLC

Schneider

admite los protocolos

Modbus

y

Modbus Plus

,

el PLC Omron

admite

el protocolo

Host Link

Según el acuerdo, Mitsubishi

PLC

admite el protocolo

CC-Link

y Panasonic

PLC

admite el protocolo

MEWTOCOL-COM

. Entre ellos Modbus

No es sólo el protocolo de comunicación del

PLC

, también se utiliza en muchos instrumentos inteligentes y convertidores de frecuencia, y se ha utilizado en el campo del control industrial.

Ha sido ampliamente utilizado en el campo

[38]

. En este artículo, se selecciona

Modbus

como protocolo de datos para la comunicación entre el controlador principal y el módulo remoto.

En el protocolo mencionado anteriormente,

el

protocolo MEWTOCOL-COM es abierto y simple, este documento realiza algunos cambios en base a él.

Como

protocolo de datos para la comunicación entre

RMEN

y módulos

de E/S ,

más adelante se denominará protocolo RM-COM .

Symmet proporciona soluciones de control de movimiento STM32+FPGA.