ILA core provides tracking and triggering, according to the data capture trigger condition set by the user, and then under the control of ICON, by boundary scan port to upload the data to the PC, and finally shows the signal waveforms Analyzer.

Although behavioral simulation we do not need to join ILA can be input and output, parameter, wire and reg types of data observations, but burned into the program the board when we can not see changes in these signals, it is caught by ILA observed signal takes you want, they can be observed, after burn-observation signal bitstream file to determine whether the code is correct.

trigger

When using ILA IP core, you must choose when to start capturing data to the IP core, which is called a trigger event.

a. of the trigger port. In order to monitor various signals and data bus design, the need to use different trigger port. For example, if the design of the internal system to monitor a control signal bus, an address signal and a data signal, it is necessary to specify a single port for each trigger / signal group. If these different signals to a bus and a trigger port, the monitor can not find the CE, WE and OE controls and the like so that a change signal when the address bus is within a specified range. In order to achieve minimal resources, you can choose different types of matching unit needed to customize the starting ILA IP core.

B. match logic. Each port has one or more trigger matching unit matching unit which performs a real logic block comparisons. There are several classes matching unit may be used. The simplest matching unit is equal to (=) or not equal (! =) Compare, such matching FPGA occupies a minimum logical resource units. The most complex matching unit may comprise achieve equal (=), not equal (! =), Greater than (>), less than (<), greater than or equal to (> =), less than or equal to (<=) and including all range comparison Compare type. The matching unit may be configured to include an edge detection signal, such as detection of a comparison rising, falling, or vary along the (rising and falling). Said matching unit of the following type.

(1) substantially matching unit (Basic) and comprises substantially matching unit (Basic with Edges) signal edge; (! =) Substantially matching unit may perform equal (=), not equal to comparison, substantially matching unit comprises a signal edge may also be for comparing a rising edge (R) falling edge (F) and a change in (B) is.

(2) Extended matching unit (Extended) and comprises a signal edge spreading matching unit (Extended with Edges): (! =) Expansion matching unit may perform equal (=), not equal, greater than (>), less than (<), greater than or equal to (> =), less than or equal to (<=) comparing, in the signal matching unit comprises a base may also be, the falling edge (F) and the rising edge of the comparison (R) varies in (B) is.

(3) the range of the matching unit (Range) and comprises a signal along a range matching unit: range matching unit may perform all the matching operation extension matching unit, value range also can compare value and exceeds the specified range, including the range of the signal along the matching unit may also, the falling edge (F) and the rising edge of the comparison (R) varies in (B) is.

C. matching unit counter. Matching unit group on the specified ports may trigger a configuration for each output matching counter for detecting the number of trigger events, may be a sequence, the sequence may not. Size specified when the counter generates an IP core technology events and / or counting procedure whether the sequence of determined at runtime.

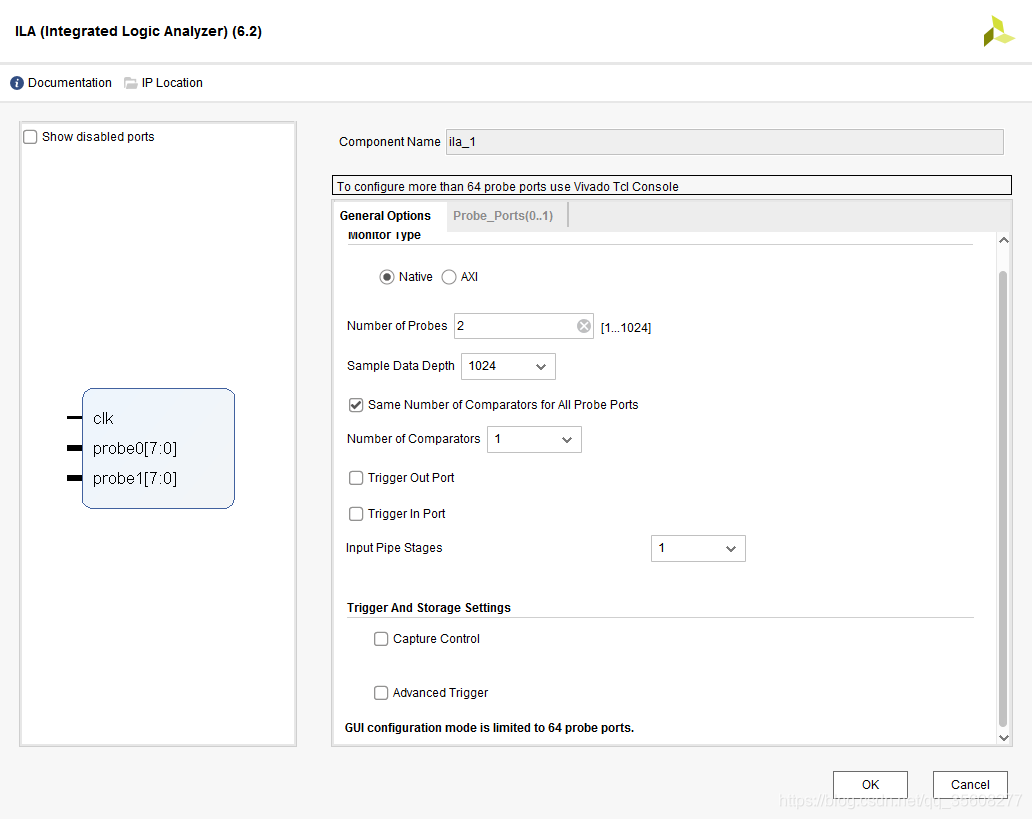

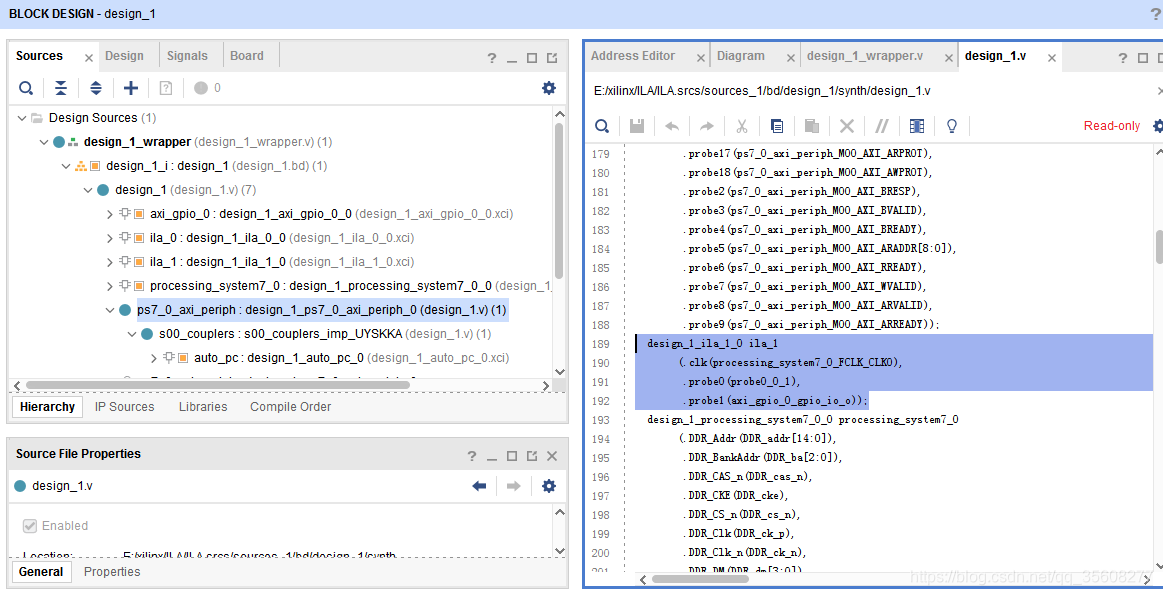

Number of probes 2 need to be disposed in the observed signal group 2 group,

the Sample Depth 1024 set the Data sampling depth, which is the need to consume the BRAM BRAM sampling depth greater the FPGA can be set greater, of course, will reduce the compilation speed.

Probe Port probe oscilloscope-like pen, but this is within the FPGA

Generating

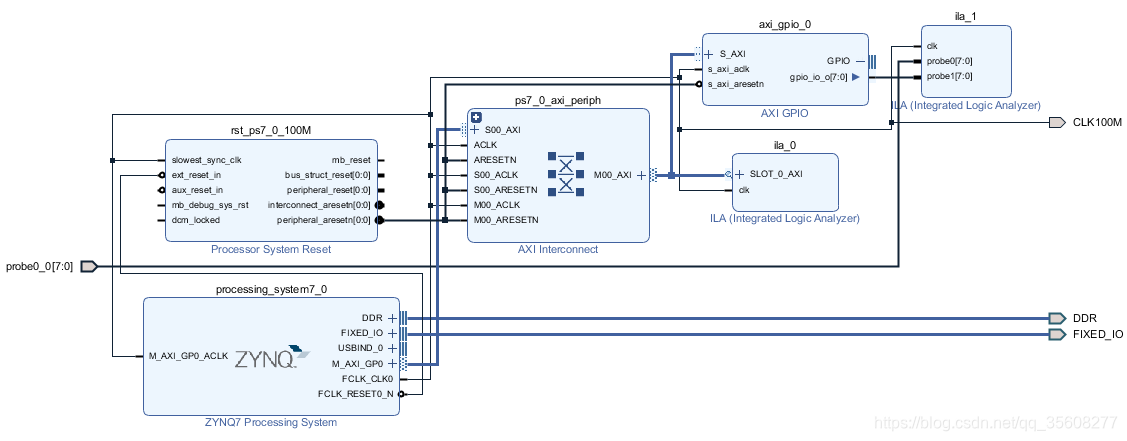

observation differences FPGA CNT and the speed sdk axigpio cnt, and logic axi

Start sdk

Open target