Memory - MESI cache coherency protocol: how to make multi-core CPU cache consistency

Principles of Computer Composition catalog: https://www.cnblogs.com/binarylei/p/12585607.html

In the last memory - Cache (CPU Cache): Why use the cache , we analyzed the Cache (CPU Cache) data structure, and how to read and write operations. In the write operation, the write-back policy can replace direct write by using a policy, the data is first written to the CPU Cache, thereby improving throughput. But always also left behind a problem, and that is how multi-core CPU to ensure the consistency of Cache?

1. cache coherency

1.1 root of the problem

- CPU Cache: The solution is memory access speed and CPU speed gap is too big problem.

- Multi-core CPU: difficult to raise the frequency of the time, by increasing the CPU core to enhance the throughput of the way the CPU.

We both combine a multi-core and CPU Cache, give us a new challenge. Because each CPU core each have their own cache operation between each other is independent, it will bring cache coherency (Cache Coherence) problem.

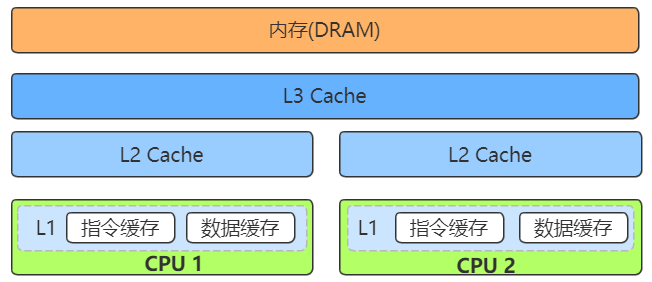

CPU in the Cache shown above, L1, and L2 Cache are unique to the CPU, and L3 and are shared DRAM. If CPU-1 to update their L1 or L2 Cache not updated main memory, CPU-1 or write concurrent read while the CPU-2, will cause data inconsistency CPU-1 and CPU-2 is. Either directly write or write-back policy can not solve this problem.

1.2 Solution

To solve this problem cache inconsistency, we need to have a mechanism to synchronize two different core inside of cached data. That such a mechanism what conditions need to meet it? I think can do the following two points is reasonable.

-

Write spread (the Write Propagation) : In a CPU core, our data update Cache, Cache Line must be able to spread to other nodes in the corresponding.

-

Serializable transaction (the Serialization the Transaction) : a reading and writing CPU core inside, appear in other nodes, the same sequence.

Serialized transaction more difficult to understand, for example. There are four CPU-1 ~ 4 CPU, CPU-1 data 5000 is modified to i, CPU-2 and the modified data into i 6000, they will modify the operation of the broadcast to CPU-3 and CPU-4. CPU-3 may receive the first broadcast CPU-1, i is modified to 5000, and then they receive the broadcast CPU-2, i is modified to 6000, and the CPU-4 contrary, 6000 Pre changed to modify 5000. This resulted in inconsistencies both CPU data, that is, do not serialized transaction.

2. bus sniffing mechanisms and MESI protocol

To solve cache coherency problems, we must first solve the problem of data spread among multiple CPU cores.

- Bus sniffing (Bus Snooping) : The most common type of multi-core CPU data broadcasting solve the problem. Essentially all read and write requests via a bus (Bus) broadcast to all of the CPU core, and then let go of each core "sniff" the request, and then responds according to the local circumstances.

- MESI protocol : bus-based cache coherency protocol sniffer mechanism, MESI protocol is also being introduced in the Pentium era to the Intel CPU.

2.1 Write spread vs write failure

- Write failure (Write Invalidate) protocol : the failure of the agreement in writing, after the CPU write Cache, it will go to broadcast a "failed" request to all other CPU. If there are other CPU cache line like this, directly labeled as a failure. MESI protocol is used to write invalid protocol.

- Propagation write (Write Invalidate) protocol : the CPU to other data broadcast will, with respect to the failure of a write request, occupying more bandwidth.

2.2 MESI protocol

The origin of the MESI protocol of it, from our four different tags for Cache Line, namely:

- M: Representative modified (Modified), indicates that no dirty data synchronized to the main memory after the data modifications.

- E: Representative exclusive (Exclusive), exclusive mode, may correspond to any modified data need not broadcast to the other CPU.

- S: means Shared (Shared), when there are two data reading CPU, the cache line becomes a shared state from exclusive. At this time, data is modified, it is necessary to broadcast another CPU.

- I: Representative has expired (the Invalidated), data indicating the invalidity and the re-read data from main memory.

reference:

- "Westward Computer" section 6.9: explain the consistency of multi-core CPU to access stored data in more detail.

The intentions of recording a little bit every day. Perhaps the content is not important, but the habit is very important!