这篇文章主要整理静态时序分析(STA)的一些基本概念

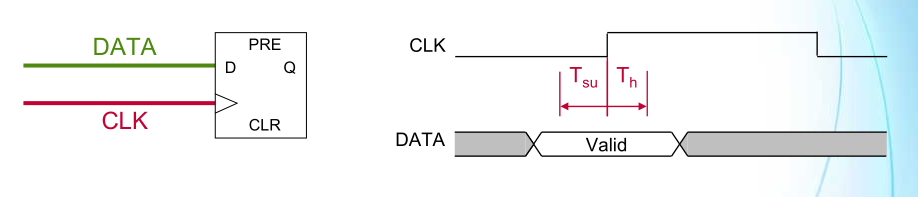

1. setup & hold

对于任何一个 DFF, 都有两个重要的参数: setup time 和 hold time

这两个参数是相对于时钟信号上升沿(或者下降沿)来定义的:

setup time 是在 CLK 端的时钟信号上升沿到来之前, D 端数据信号必须保持稳定的最短时间,这个最短时间长度记为 Tsu

hold time 是在 CLK 端的时钟信号上升沿到来之后, D 端数据信号必须继续维持稳定的最短时间,这个时间长度记为 Th

也就是说,D 端的数据信号必须比时钟上升沿提前至少 Tsu 时间到达D端,且在时钟上升沿到来之后的 Th 时间长度内依然保持稳定,才能保证 DFF 将 D 端的数据信号稳定的锁存下来。

数字电路设计的重中之重就是要保证每一个 DFF 都能够将其输入端的数据稳定的锁存住,也就是要保证每个 DFF 的 setup time 和 hold time 都不出现违例。

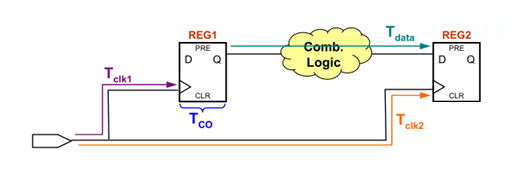

2. 静态时序分析基本模型

下图就是一个最简单的静态时序分析模型:

|------------------------------------------|