为什么会有建立时间setup和保持时间hold要求

D触发器结构

要知道为什么会有setup、hold要求,首先要清楚D触发器的结构

D触发器可以由静态逻辑实现,也可以由动态逻辑实现,这里仅讨论静态CMOS D触发器的结构

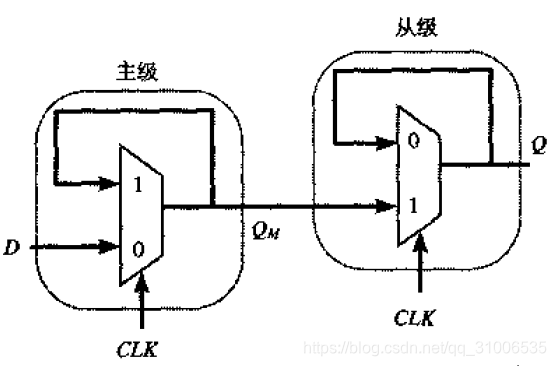

构成一个D触发器最普遍方法是采用主从结构,由一个负latch(主级)和正latch(从级)串联而成,而latch可以采用传输门构成的多路开关MUX来实现,见下图

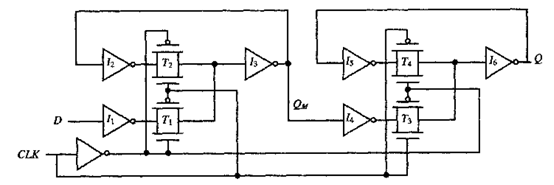

而具体的电路结构如下图

可以看到latch中的MUX是通过传输门逻辑实现的,牢记这个结构即可

为什么有建立时间要求(setup)

那为什么会有建立时间要求呢?首先明确建立时间的概念

建立时间:输入数据D在时钟上升沿之前必须有效的时间

假设上图中反相器的延时都是

,传输门的延时都是

。对于传输门型的主从边沿触发器,输入数据必须在时钟上升沿到来之前必须传播通过

、

、

、

,这才能保证当时钟上升沿到来导致

打开时,其两端的电压是相等的,否则交叉耦合反相器就会停留在一个不正确的值。

因此该结构的建立时间

为什么有保持时间要求(hold)

那为什么会有保持时间要求呢?一样地,先明确保持时间的概念

保持时间:输入数据D在时钟上升沿之后必须保持稳定的时间

保持时间其实是为了保证在时钟上升沿之后,D端的数据不能影响触发器在该上升沿采集的数据。我们都知道时钟上升沿之后,主latch将处于锁存状态,也就是D数据是无法传输到主latch中的,那为什么还有这样一个保持时间要求呢?

仔细观察上图结构,D端数据不再影响主latch中数据的条件是当时钟上升沿到来时,传输门

关断。但是注意,由于从D触发器的D pin和CLK pin到传输门

的延时是不同的,以及传输门的关断本身需要时间,因此在CLK信号到达传输门

控制端并且完成关断动作之前,传输门

前的数据端必须保持不变(注意不是D pin端数据),由此即可计算出保持时间要求。

假设传输门的关断不需要时间,而CLK net上的反相器和D net上的反相器延时相同,那么建立时间就为0

如果CLK net的反相器延时为

,D net的反相器延时为

,那么保持时间

建立时间、保持时间跟什么有关

- 触发器本身的结构、工艺

- D、CLK信号的transition

- PVT

从上面的分析可以知道,建立时间、保持时间的大小本质上跟内部反相器和传输门的延时有关,凡是会影响门延时的因素都能影响建立时间和保持时间

比方说,D、CLK信号transition的不同会导致D net和CLK net上的反相器延时不同,进而影响hold;而如果触发器本身采用LVT单元实现,那么速度更快,setup也就更小.