英特尔Quick Assist Technology (以下简称QAT)是英特尔针对网络安全和数据存储推出的一个硬件加速技术。QAT支持对称数据加密算法(如AES)中的密码操作和验证操作运算和公钥非对称数据加密算法(如RSA、椭圆曲线等)中的加密运算。

逻辑实例

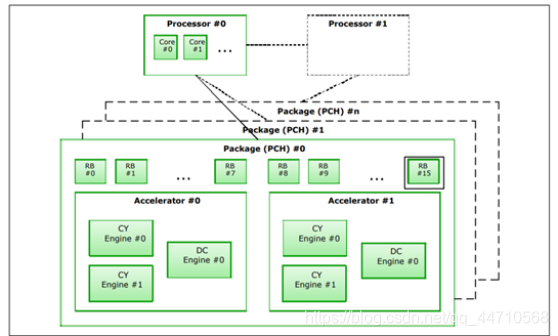

可以将逻辑实例视为到硬件的通道。逻辑实例允许地址域(即内核空间和单个用户空间进程)配置由该地址域使用的环,并定义该环的行为。QAT Accelerator有一系列rings来存放数据。16个rings组成一个ring bank。如图1中一个package(即一个设备)包含16个ring bank和2个accelerator,每个accelerator又包含多个engine。Engine是专门处理数据的加速单元,分为压缩解压和加解密两类。每个处理器有多个物理核或逻辑核。

Ring按作用可分为两类:request ring和response ring。

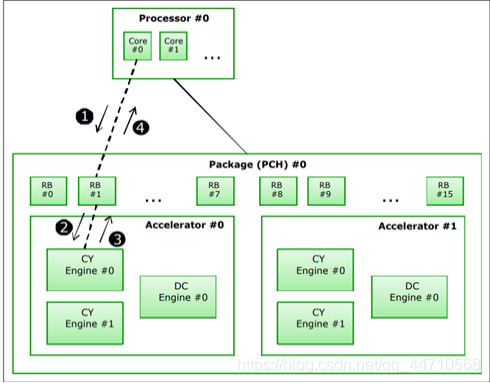

处理器和QAT设备之间的通信可简化为以下四个步骤,如图2所示:

1) 处理器发送一个request到request ring中

2) Engine设备从request ring中读出request

3) Engine处理数据完毕后,将response写入response ring中

4) 处理器从response ring中取出response

Service instance可以看做是QAT engine和处理器之间通信的通道。

一个Processor有n个logical core。 每个core / thread可对应n个instance。每个ring bank包括16个rings。每个DC instance 需要2个ring,每个CY instance需要2个ring。多个instance可共享同一个engine。

中断模式

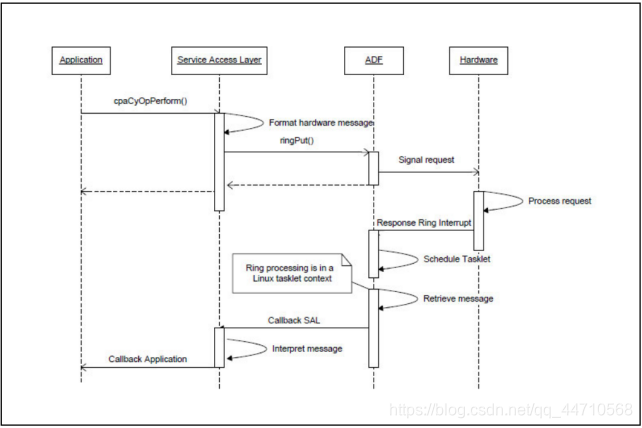

在中断模式下配置时,加速卡驱动程序框架(ADF)寄存器用于响应环处理的中断处理程序。由于服务中断的等待时间代价很大,因此硬件辅助环提供一种将中断成本摊销到单个中断中的机制可能服务多个响应。

加速卡驱动程序框架注册了一个中断处理程序来处理环形存储区中断。当一个 中断触发时,加速卡驱动程序框架为中断提供服务并创建一个中断处理程序,下半部分消耗来自响应环的响应。如果支持MSI-X,中断处理程序的下半部分将创建并关联到已配置的内核。对应用程序代码的回调发生在此Tasklet的上下文中。Linux将中断处理程序分为两半。如此称为“上半部分”的例程实际上是对中断做出响应的,即向request_irq 注册。“下半部分”是由上半部分将在更安全的时间执行。这个顺序是如下图3所示(为清楚起见,已减少了整个序列)。

对于给定的平台,每个特定内部连接和QAT端点数(例如,对于Intel ®C62x芯片组最多三个)依赖于产品、sku和路由(即和配置相关的)。对于每个QAT端点(例如,QAT[0]),使用硬件辅助的环作为通信机制,在CPU和QAT端点之间传输请求,反之亦然。硬件支持256个环(每个QAT端点),每个环都有头尾配置状态寄存器(CSR)指针映射到CPU上的PCIe*内存。提供的软件根据配置文件中声明的加密(CY)和数据压缩(DC)实例来分配环。

每个QAT端点都有多个计算引擎。对于给定的QAT端点,与该端点关联的所有环都是共享的,并且硬件负载平衡来自这些环的请求。