本文为明德扬原创及录用文章,转载请注明出处!

作者:轩工

1.1 概述

| 条目 | 说明 |

|---|---|

| 分类 | 1>> 面向设计的语句; // 可综合。2>> 面向测试的语句; //testbench ,不可综合。 |

| 特点 | 设计语句 assign , always ,模块例化,都对应实际电路,并行执行。 |

| 构造 |  |

1.2 模块 Module

| 条目 | 说明 |

|---|---|

| 模块名(端口列表) | 整个电路的外特性,抽象为黑盒子; |

| 端口方向 | input , output ; inout ; |

| 端口类型 | wire , reg ;端口类型是 wire 时可以省略。例: input a ; // 端口方向为输入,类型默认为 wire ; |

1.3 数据类型

1.3.1 wire/reg 线网

wire 和 reg 都是线类型,工程上没区别;只是 always/initial 模块中输出定义需要为 reg 型;

注意:不要将 reg 类型与 D 触发器混淆, reg 理解为因为代码所产生的。

例如:

| wire [7:0] a; // 定义了 8 位的 wire 型数据wireb; // 定义了 1 位的 wire 型数据 |

|---|

| reg [3:0]sum ; // 定义了一个 4 位的 reg 型数据 |

1.3.2 常量

| 类型 | 格式 | 说明 |

|---|---|---|

| parameter | parameter 数据名 = 表达式 | parameterMSB = 7 ;// 定义参数 MSB 为常量 7 ;推荐大写; |

| 常量 | < 位宽 >< 进制 >< 数字 > | 二进制: B 或 b ;十进制: D 或 d ;八进制: O 或 o ; 十六进制: H 或 h ;8’b1010_1100 (‘b 表示二进制 ) 下画线“ _”, 提高阅读性。 |

| < 数字 > | 默认十进制; | |

| 4 值逻辑 | 0 : Logic Low | 低电平; |

| 1 : Logic High | 高电平; | |

| x : Unknow ; | 不确定; | |

| z : High Impedance ; | 高阻态; // 三态门 |

1.4 运算符

1.4.1 概述

| 运算符 | 说明 |

|---|---|

| 算术运算符 | + ( 加 ) , - (减), * (乘), / (除), % (取模); |

| 每个运算符在电路中都是个模块,如加法器,减法器;!注意:除法,除 2^n ,是移位运算,浮点运算就复杂了,因此浮点运算要专用除法器; | |

| 关系运算符 | >, <, >=, <= , == (相等), ! = (不相等); |

| 逻辑运算符 | && (逻辑与) . |

| 位运算符 | & (与), |

| 移位运算符 | << (左移), >> (右移); |

| 归约操作 | & , ~& , |

| 条件运算符 | ?: |

| 拼接运算符 | {} //{3{a[0]}}: 代表 3 根同样的 a[0] 线, {a[0],a[0],a[0]} |

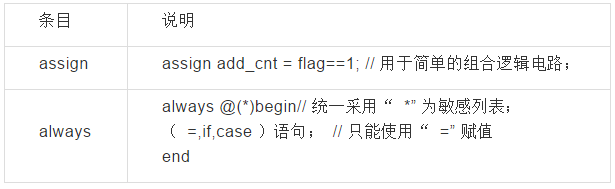

1.5 设计语句

1.5.1 assign (连续赋值)

| 实例 | 说明 |

|---|---|

| assigny = ~ b ;assign out = a1 && c1 ;assign f = sel ? a : b ; | >> 实现可以用布尔函数描述的组合逻辑电路; |

| >>“=” 后面可以是任何布尔函数; >> 并行执行; | |

| 典型错误 1 :assigna = b + a; | 避免出现反馈电路:变为了不可知时序逻辑电路; |

1.5.2 always (过程块)

a、赋值

b、if 语句

c、case 语句

d、代码 & 硬件

1.5.3 模块例化

a、作用

系统设计时,建议遵循以下设计原则:

b、常见的典型错误如下所示:

1.5.4 全加器

全加器顶层: w1 , w2 , w3 :模块之间连线;

半加强: 2 种描述方法,如下:

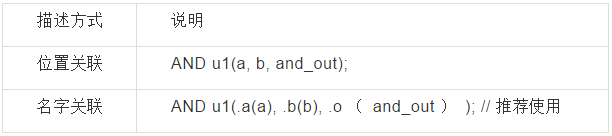

描述方式

1.6 测试语句

1.6.1 结构

Testbench

1.6.2 特殊符号

1.6.3 语句

1.6.4 系统任务和函数

1.7 代码模板

1.7.1 组合逻辑电路

1.7.2 时序逻辑电路

a、计数器模板 1

b、计数器模板 2

c、 4 段式状态机模板

1.7.3 Testbench

a、框架

b、复位

c、仿真时钟

d、激励信号

以上就是本人总结的 Verilog 语法相关知识点,当然明德扬还有很多比较简便的模板给我们使用,感兴趣的朋友可以进入明德扬论坛进行更多 FPGA 或者语法相关讨论!