Ref:TMS320x2833x Analog-to-Digital Converter (ADC) Module

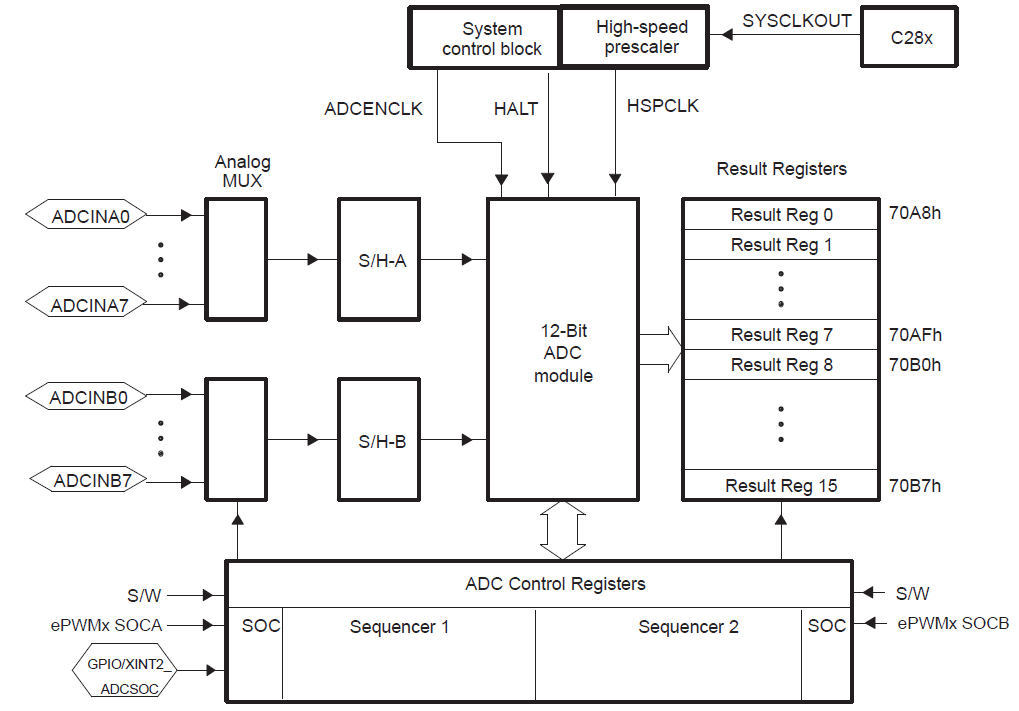

Functions of the ADC module include:

- 內建取樣與保持電路(S / H),兩組12位元的ADC轉換模組。

- 類比輸入:0~3V

- ADC時鐘快速轉換時間運行在12.5 MHz,或6.25 MSPS

- 16個多工類比輸入訊號(ADCIN0-ADCIN15)

- SEQ(倫循順序)可以作為兩個獨立的8狀態定序器或作為倫循順序來操作或一個大的16倫循順序狀態來操作

- 輸入模擬電壓的數字值由下式導出

- 靈活的中斷控制允許每個序列結束(EOS)或每個其他EOS的中斷請求

- ePWM觸發器可以在雙音序器模式下獨立運行

- 作為轉換開始(SOC)序列的源的多個觸發器

- 軟體觸發(SOC_SEQn位元設定)

- ePWM 1-6

- GPIO XINT2

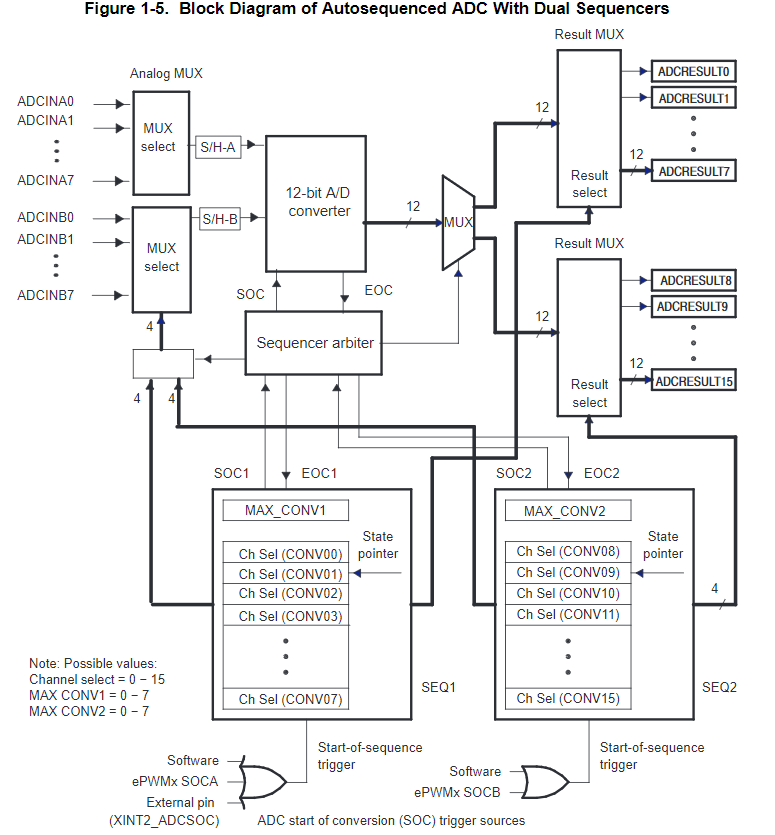

Block Diagram of the ADC Module

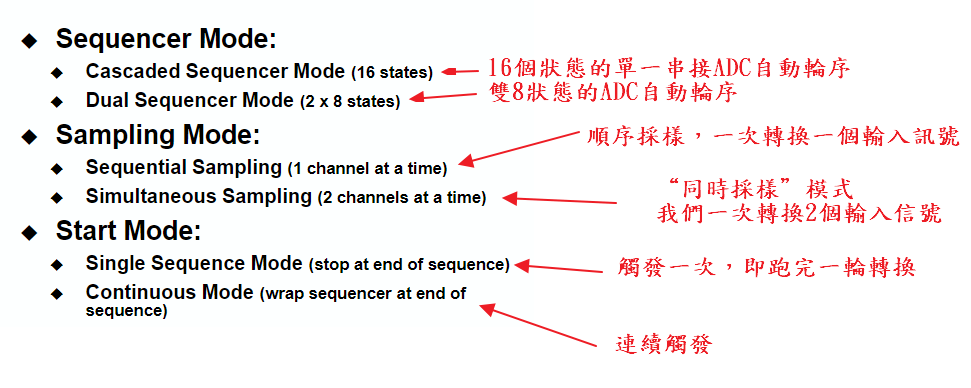

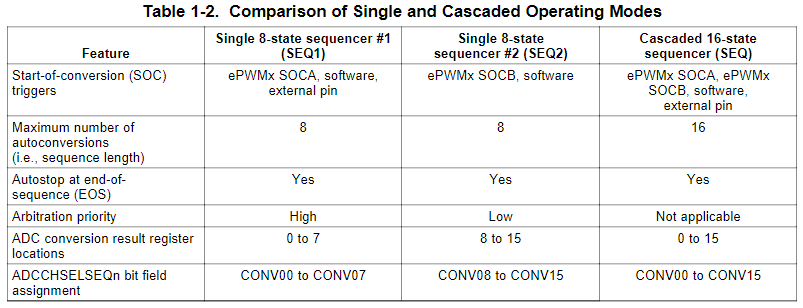

ADC Operating Modes

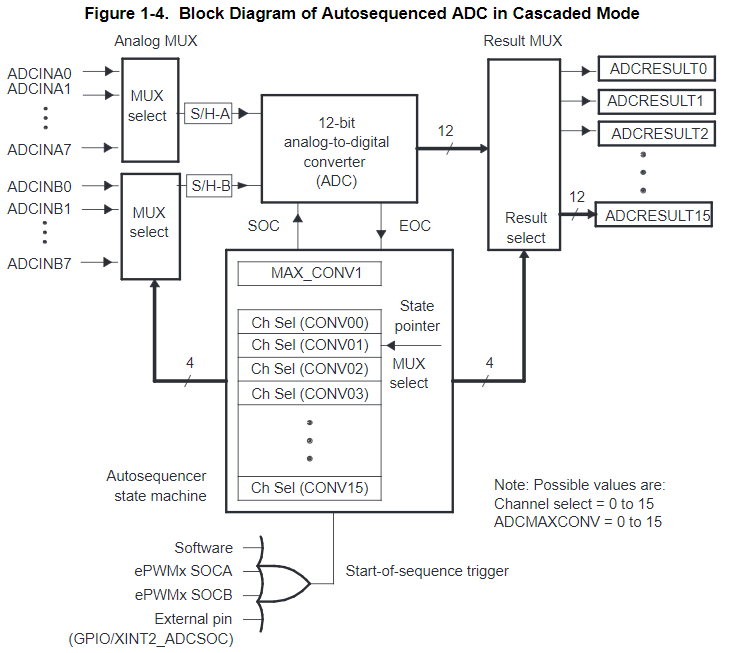

ADC In Cascaded Mode (16個狀態的單一串接自動輪序方塊結構圖)

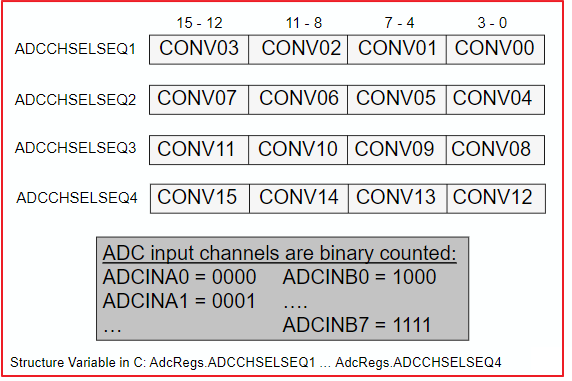

CONV.xx由4位元來定義輸入接腳,來選擇ADCINXX被輸入取樣保持和緩衝

最高為元選擇ADCINA or ADCINB 0:A 1:B

後三位元選擇ADCINX0-7

Ex:

- CONVxx=0101=> ADCINA5

- CONVxx=1011=> ADCINB3

雙8狀態的ADC自動輪序方塊結構圖

在此模式下,CONVxx的最高為元失去意義,只有三位元去選擇ADCINA0-7 and ADCINB0-7

在此雙輪序模式中,SEQ1有最高的耶先續,例如SEQ1 and SEQ2同時提出要求,會先執行SEQ1

若處理SEQ1輪序期間,SEQ1 & SEQ2又提出要求,則ADC依然會選擇SEQ1做處理

輪序器運作於8狀態與16狀態的些微差異表

可以注意到只有SEQ1右外接腳的SOC

Example 1-1.Simultaneous Sampling Dual Sequencer Mode Example(同時採樣雙序列器模式示例)

Example initialization: AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // 設置同步採樣MODE AdcRegs.ADCMAXCONV.all = 0x0033; // 每個排序器4個轉換(共八個) AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3 AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4; // Setup conv from ADCINA4 & ADCINB4 AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & ADCINB5 AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & ADCINB6 AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7; // Setup conv from ADCINA7 & ADCINB7 If SEQ1 and SEQ2 were both executed, the results would go to the following RESULT registers: ADCINA0 -> ADCRESULT0 ADCINB0 -> ADCRESULT1 ADCINA1 -> ADCRESULT2 ADCINB1 -> ADCRESULT3 ADCINA2 -> ADCRESULT4 ADCINB2 -> ADCRESULT5 ADCINA3 -> ADCRESULT6 ADCINB3 -> ADCRESULT7 ADCINA4 -> ADCRESULT8 ADCINB4 -> ADCRESULT9 ADCINA5 -> ADCRESULT10 ADCINB5 -> ADCRESULT11 ADCINA6 -> ADCRESULT12 ADCINB6 -> ADCRESULT13 ADCINA7 -> ADCRESULT14 ADCINB7 -> ADCRESULT15

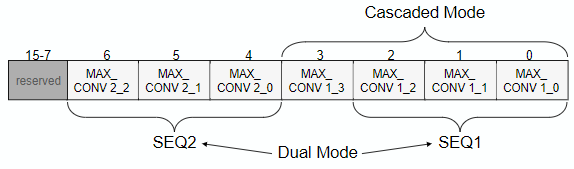

ADC MAXCONV Register(ADCMAXCONV小補充)

- BIT定義每個觸發器的轉換次數(二進制+1)

- 每個排序器從“初始狀態”開始並順序前進

- 除非軟件提早重置,否則每個都會以“結束狀態”進行換行

ADC Input Channel Select Registers(ADCCHSELSEQn 小補充)

- ADC輸入通道選擇排序控制寄存器

Example 1-2. Simultaneous Sampling Cascaded Sequencer Mode Example(級聯排序列同步採樣模式示例)

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode 同步採樣模式 AdcRegs.ADCTRL1.bit.SEQ_CASC = 0x1; // Setup cascaded sequencer mode 設置級聯排序器模式 AdcRegs.ADCMAXCONV.all = 0x0007; // 8 double conv's (16 total) 每個排序器8個轉換(共16個) AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3 AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4; // Setup conv from ADCINA4 & ADCINB4 AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5; // Setup conv from ADCINA5 & ADCINB5 AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6; // Setup conv from ADCINA6 & ADCINB6 AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7; // Setup conv from ADCINA7 & ADCINB7 If the cascaded SEQ was executed, the results would go to the following ADCRESULT registers: ADCINA0 -> ADCRESULT0 ADCINB0 -> ADCRESULT1 ADCINA1 -> ADCRESULT2 ADCINB1 -> ADCRESULT3 ADCINA2 -> ADCRESULT4 ADCINB2 -> ADCRESULT5 ADCINA3 -> ADCRESULT6 ADCINB3 -> ADCRESULT7 ADCINA4 -> ADCRESULT8 ADCINB4 -> ADCRESULT9 ADCINA5 -> ADCRESULT10 ADCINB5 -> ADCRESULT11 ADCINA6 -> ADCRESULT12 ADCINB6 -> ADCRESULT13 ADCINA7 -> ADCRESULT14 ADCINB7 -> ADCRESULT15

Example 1-3. Conversion in Dual-Sequencer Mode Using SEQ1 (使用SEQ1的雙輪序模式之轉換)

假如要用SEQ1做7個輪序轉換(例如在自動輪序期間,通道2、3、2、3、6、7、12需要被轉換),則ADCMAXCONV.all=0x006 (6+1=7)

同時ADCCHSELSEQn 需要設計為下表的值

-

CONV00 = 2

-

CONV01 = 3

-

CONV02 = 2

-

CONV03 = 3

-

CONV04 = 6

-

CONV05 = 7

-

CONV06 = 12

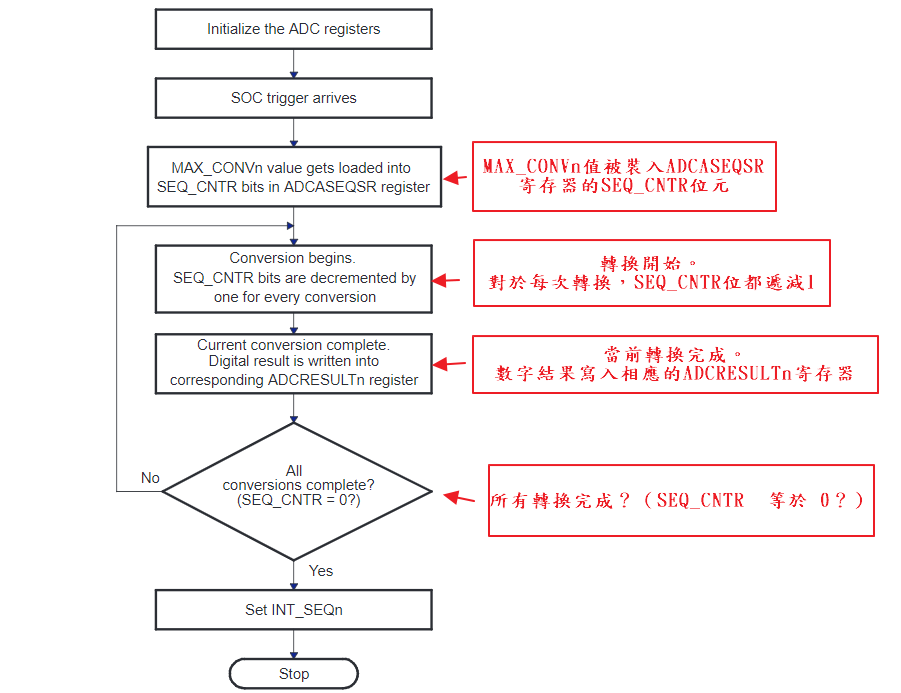

Flow Chart for Uninterrupted Autosequenced Mode(連續自動排序模式程式運作流程圖)