状态机分类:

通常, 状态机的状态数量有限, 称为有限状态机(FSM) 。由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机。 根据状态机的输出信号是否与电路的输入有关分为 Mealy 型状态机和 Moore 型状态机。

Mealy 型状态机:

电路的输出信号不仅与电路当前状态有关, 还与电路的输入有关。

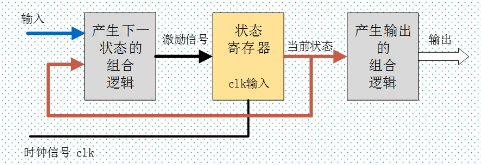

Moore 型状态机:

电路的输出仅仅与各触发器的状态, 不受电路输入信号影响或无输入。

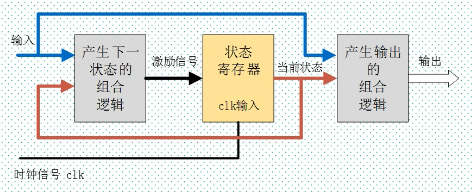

三段式状态机的一般结构:

1)利用参数定义语句 parameter 描述状态机各个状态名称, 即状态编码。一般采用独热码。

2)用时序always模块,格式化描述次态寄存器(下一个状态的寄存器)迁移到现态寄存器。

3)用组合逻辑always模块,描述状态转移条件判断或者状态转移规律。

4)同步时序always模块,格式化描述各个状态的输出。

实现代码:

module test( input clk, input rst_n, output reg out ); //reg define reg q; //第一步,状态声明和状态编码 reg [1:0] current_state; reg [1:0] next_state; parameter [1:0] S0=4'b0000; parameter [1:0] S1=4'b0010; parameter [1:0] S2=4'b0100; parameter [1:0] S3=4'b1000; //第二部,时序逻辑: 描述状态转换,格式固定 always@(posedge clk) begin if(!rst_n) current_state <= 0; else current_state <= next_state; end //第三部,组合逻辑: 描述状态转移条件,即只考虑状态之间的跳转,也就是说各个状态机之间跳转关系。 always @ (current_state or .... ) //电平触发, begin next_state = x; //要初始化,使得系统复位后能进入正确的状态 case(current_state) S0: if(...) next_state = S1; //阻塞赋值 else ...... S1: if(...) next_state = S2; //阻塞赋值 else ...... . . . default : ..... endcase end //第四部,用时序always块输出逻辑: 让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺 always@(posedge clk) begin if(!rst_n) out<=1'b0; else begin case(current_state) S0: out<=1'b0; S1: out<=1'b1; . . . default : .... endcase end end assign q = ou; //让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺 endmodule