NOR Flash 是一种常见的存储设备。它可以向内存一样的读,但是不可以像内存一样写。 因为它的这一特性很多的嵌入式linux 设备都会有一块NOR flash 作为启动的芯片。在系统一上电之后就可以直接开始运行程序,执行初始化操作。但是由于价格的原因,NOR flash 一般都不会很大大多都是用作启动的芯片的(我觉得用来放boot loader 也是非常棒的 用来实现ISP 会简单很多)

我们先来分析开发板的主控芯片 S3C2440 ,很老很老的一款芯片了,也就比我小几岁。

这是S3C2440 不同的启动模式对应的内存图。 主要是两大类,一类是 NAND启动,一类是非NAND。

当进行nand启动的时候 CPU 会自动云心内部的程序把 NANDFlash 上面的前 4K的数据拷贝到片内仅有的 4K内存上

这时候这一段内存对应的地址就是0~ 4095 (程序上电是从 0地址开始运行的 )

当启动模式是非 NAND 启动的时候(NOR启动) 程序是直接从0地址开始运行的 片内的4K ram 的地址变成 0x4000 0000以及之后的4K 空间

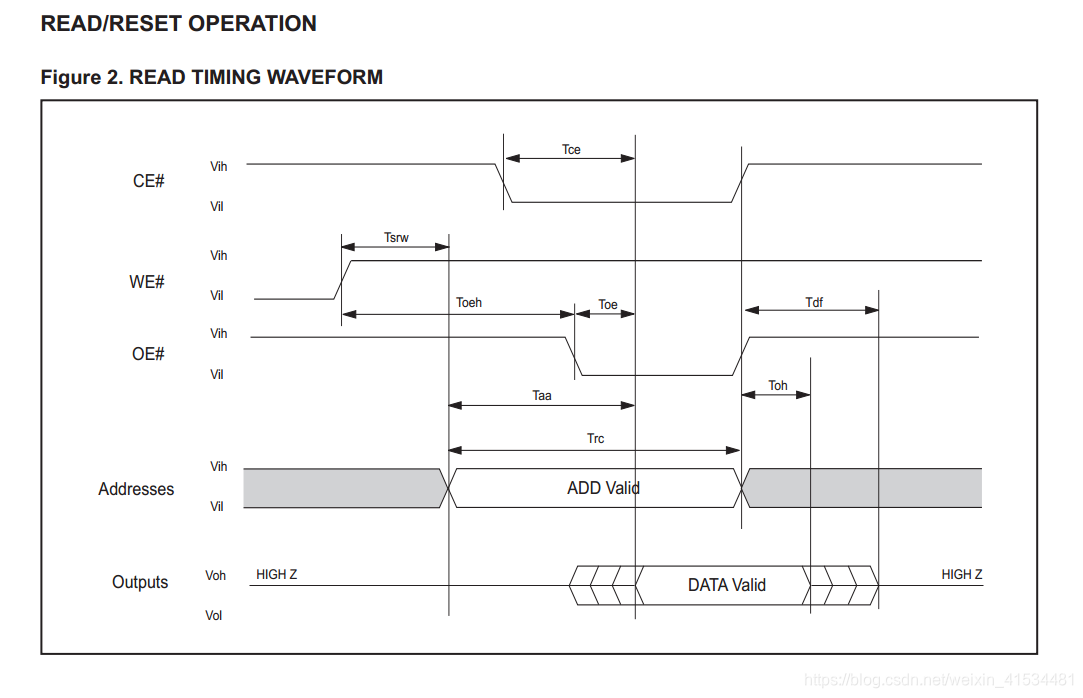

接下来我们分析一下时序部分

根据时序图 我们可以知道

读取的 时序的逻辑是 先发送地址线(A24:A0) 然后发送指定的片选线 nGCSx 和nOE(输出使能)

这是 JZ2440 开发板的 NOR flash 芯片我的 读取时序

NOR flash 的 AC特性表

这里最大70ns 就可以读取到数据 这是一个极限值 ,在芯片接收到地址之后的70ns 之后肯定有数据

OE 之后 30ns 数据就是有效的

Toh 数据保持时间是0

Tdf 数据输出浮动(这段时间内数据不稳定 不能去操作其他的)

为了简化操作 让 CE OE ADDR 信号同时发出 都大于70ns 就可以满足这款芯片的需要

在 前面的时序图中我们知道 S3C2440侧的 时间 是以时钟周期为单位的, 这里我们的HCLK 设置成100MHz 所以也就是 说我们需要让 Tacc 大于等于 7个时钟周期

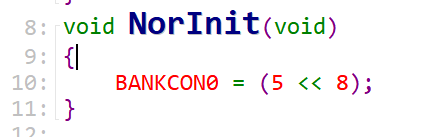

反应到寄存器的取值上面就是 BANKCON0 的 [10:8] 要大于5

NOR flash 的参数很少需要设置的。作为入门总线接口芯片的 第一个是非常合适的。