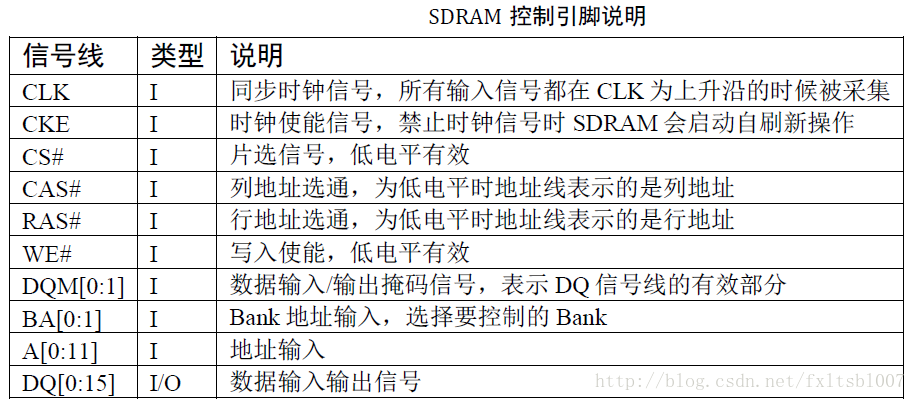

在“自我刷新”资料里,多次的提到CKE信号线。那我们就来看一下SDRAM的信号线吧。

可以看到CKE是时钟使能。正常使用期间这个信号线都处于高电平。其他的都是常规信号线,如时钟线,行选通,列选通,地址线,数据线,写使能等。

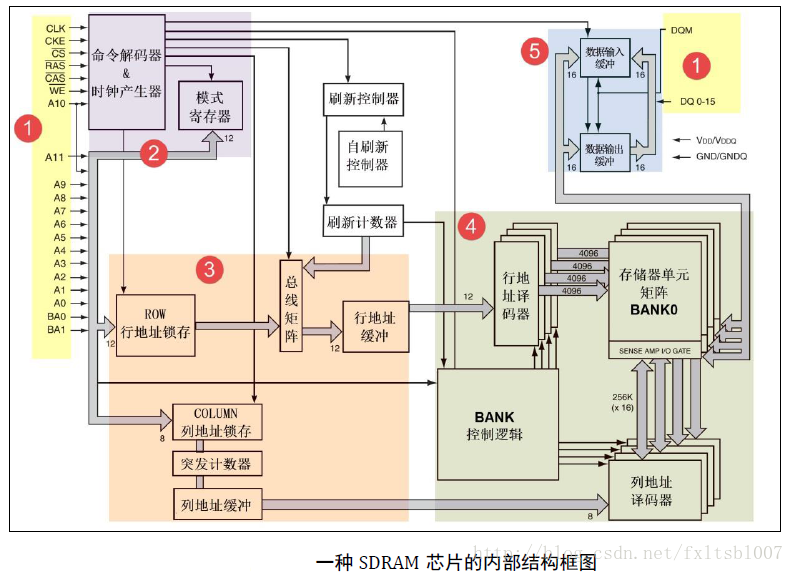

既然说到了信号线,就来顺便看一下SDRAM芯片内部的结构框图:

下面稍微解释一下这个结构框图

1、逻辑控制

SDRAM内部的“控制逻辑”指挥着整个系统的运行,外部通过CS、WE、CAS、RAS以及地址线来向控制逻辑输入命令,命令经过“命令译码器”译码,并将控制参数保存到“模式寄存器”中,控制逻辑依此运行。

2、地址控制

SDRAM包含有“A”以及“BA”两类地址线,A类地址线是行和列共用的地址线,BA地址线是独立的用于指定SDRAM内部存储矩阵号的。在命令模式下,A类地址线还用于输入某些命令参数

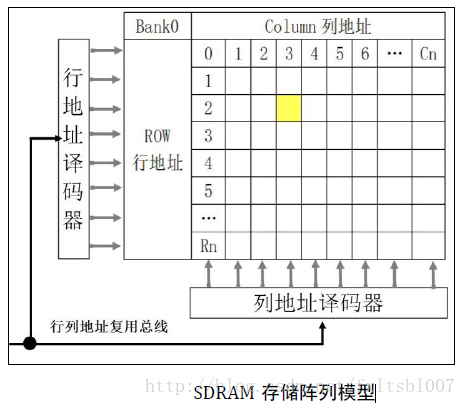

3、SDARM的存储阵列

SDRAM内部包含的存储矩阵,可以把它理解为一张表格,数据就填在这张表格上。和表格查找一样,指定一个行地址和列地址,就能精确的找到目标单元格。这样的每个单元格被成为存储单元,而这样的表被成为存储阵列。目前设计的SDRAM芯片基本上内部包含有4个这样的Bank,寻址时指定Bank号及行地址,然后再指定列地址即可寻找到目标存储单元。

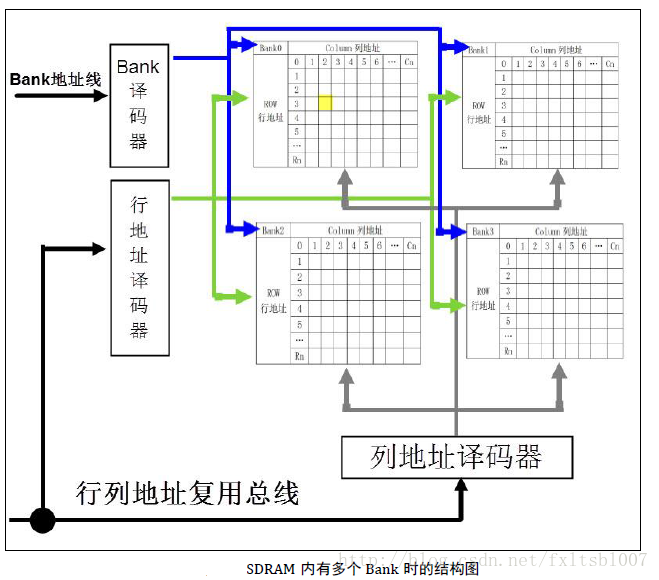

SDRAM内部具有多个Bank的结构见下图:

SDRAM芯片向外部提供有独立的BA类地址线用于Bank寻址,而行与列则共用A类地址线。

通讯时,当RAS线为低电平,则“行地址选通器”被选通,地址线A[11:0]表示的地址会被输入到“行地址译码及锁存器”中,作为存储阵列中选定的行地址。

同时,地址线BA[1:0]表示的Bank也被锁存,选中了要被操作的Bank号;

接着控制CAS线为低电平,“列地址选通器”被选通,地址线A[11:0]表示的地址会被锁存到“列地址译码器”中作为列地址,完成寻址过程。