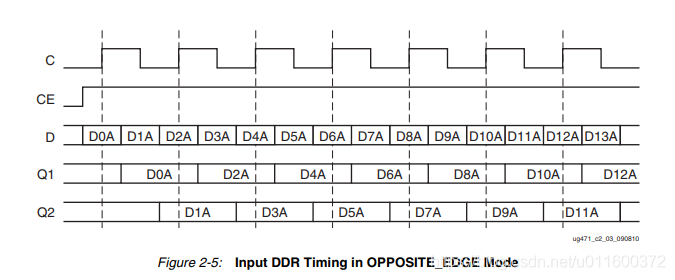

OPPOSITE_EDGE Mode

传统的输入DDR解决方案或OPPOSITE_EDGE模式是通过ILOGIC模块中的单个输入实现的。 数据在时钟的上升沿通过输出Q1提供给FPGA逻辑,在时钟的下降沿通过输出Q2提供给FPGA逻辑。 该结构类似于Virtex-6 FPGA实现。 图1 显示了使用OPPOSITE_EDGE模式的输入DDR的时序图。

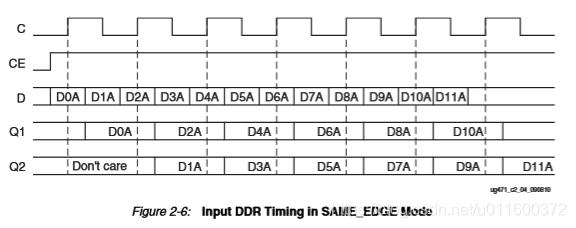

SAME_EDGE Mode

在SAME_EDGE模式下,数据在同一时钟边沿上呈现给FPGA逻辑。 该结构类似于Virtex-6 FPGA实现。

图2显示了使用SAME_EDGE模式的输入DDR的时序图。 在时序图中,输出对Q1和Q2不再是(0)和(1)。 相反,第一对呈现的是Q1(0)和Q2(不关心),然后是下一个时钟周期的对(1)和(2)。

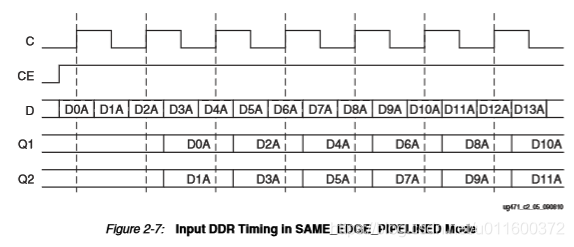

SAME_EDGE_PIPELINED Mode

在SAME_EDGE_PIPELINED模式下,数据在同一时钟边沿上呈现给FPGA逻辑。

与SAME_EDGE模式不同,数据对不会分开一个时钟周期。 但是,需要额外的时钟延迟来消除SAME_EDGE模式的分离效果。 图3显示了使用SAME_EDGE_PIPELINED 模式的输入DDR的时序图。 输出对Q1和Q2同时提供给FPGA逻辑。

xilinx IDDR原语

猜你喜欢

转载自blog.csdn.net/baidu_25816669/article/details/104293057

今日推荐

周排行