IDELAY原语使用注意事项

一、IDELAY+IDELAYCTRL

(1)IDELAY必须与IDELAYCTRL搭配使用,IDELAYCTRL主要用于给出参考时钟,进而得到延迟抽空的分辨率。

(2)IDELAYCTRL与IDELAY不需要连接。

(3)当有多个IDELAYCTRL时综合时可能会有冲突,最后统一为一个IDELAYCTRL或者选择不同的BANK的IDELAYCTRL。

二、延迟时间的计算方法

延迟时间=设置的抽头数×分辨率,其中分辨率=1/(32×参考时钟频率×2),注意有仿真表明一旦使用IDELAY,都会先增加一个0.6ns的延时,因此总延迟时间=延迟时间+0.6ns。

三、参数说明

参考下面代码,将IDELAY原语参数说明如下:

(1)CINVCTRL_SEL:是否动态地反转时钟信号C的极性。

(2)DELAY_SRC :延时信号来源,内部信号(DATAIN)或来自管脚信号(IDATAIN)。

(3)HIGH_PERFORMANCE_MODE:TURE减小抖动,FLASE降低功耗。

(4)IDELAY_TYPE:包括FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE四种模式。

(5)IDELAY_VALUE:延时值,在FIXED模式下有用。

(6)PIPE_SEL:VAR_LOAD_PIPE 模式下有用。

(7)REFCLK_FREQUENCY:参考时钟。

(8)SIGNAL_PATTERN:确定延时的是时钟还是数据,以确定不同路径上的抖动。

// receive frame interface, ibuf -> iddr

IBUFDS i_rx_frame_ibuf (.I(rx_frame_in_p),.IB(rx_frame_in_n),.O(rx_frame_ibuf_s));

IDELAYE2 #(

.CINVCTRL_SEL ("FALSE" ),// Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC ("IDATAIN" ),// Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE" ),// Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE ("VAR_LOAD" ),// FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE (0 ),// Input delay tap setting (0-31)

.PIPE_SEL ("FALSE" ),// Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY (200.0 ),// IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN ("DATA" ) // DATA, CLOCK input signal

)

IDELAYE2_F (

.CNTVALUEOUT ( ),// 5-bit output: Counter value output

.DATAOUT (rx_frame_idelay ),// 1-bit output: Delayed data output

.C (clk200 ),// 1-bit input: Clock input

.CE (1'b0 ),// 1-bit input: Active high enable increment/decrement input

.CINVCTRL ( ),// 1-bit input: Dynamic clock inversion input

.CNTVALUEIN (idly_d ),// 5-bit input: Counter value input

.DATAIN ( ),// 1-bit input: Internal delay data input

.IDATAIN (rx_frame_ibuf_s ),// 1-bit input: Data input from the I/O

.INC (1'b0 ),// 1-bit input: Increment / Decrement tap delay input

.LD (idly_en[6] ),// 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN ( ),// 1-bit input: Enable PIPELINE register to load data input

.REG

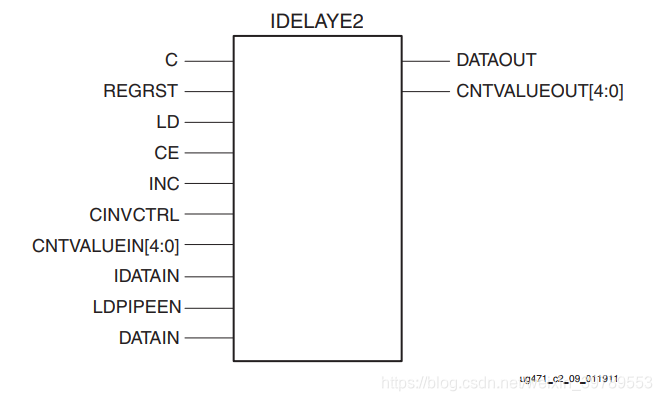

四、接口说明

1、输出接口

(1)DATAOUT:延时数据。

(2)CNTVALUEOUT:用于查看延时系数。

2、输入接口

(1)DATAIN , IDATAIN:延时数据输入信号,DATAIN是内部数据, IDATAIN是来自管脚的数据。

(2)C:时钟信号,当不是FIXED模式时,需要提供时钟信号,用于更新延时抽头系数。

(3)REGRST:复位信号,只有在VAR_LOAD_PIPE 模式下有效。

(4)CINVCTRL:允许更改时钟极性,即时钟极性反转。

(5)CNTVALUEIN:动态更改抽头系数值。

(6)LDPIPEEN:将输入的延时值加载到流水线当中。

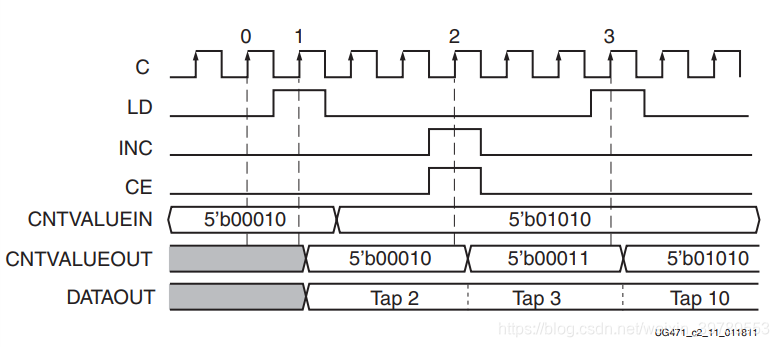

(7)CE, INC, LD:在VAR_LOAD模式下,通过LD信号可以动态多次加载CNTVALUEIN抽头系数值,当CE为高电平时,如果INC为高电平,抽头系数值CNTVALUEIN当前值+1,如果INC为高电平,抽头系数值CNTVALUEIN当前值-1,如下图。