一.实验目的:

【1】通过修改由VCS识别为Verilog代码,提高仿真性能;

【2】使用+ rad编译开关编译现有Verilog程序并执行仿真二进制文件,以演示仿真性能的提高;

二.任务安排

在A部分中,您将使用+ prof实用程序来定位仿真瓶颈。然后,您将通过更改编码样式来修改Verilog代码,以提高仿真性能。

步骤:

•使用VCS Profiler进行配置文件编解码器仿真并记录CPU运行时间;

•修改被识别为瓶颈的编解码器Verilog代码段;

•重新仿真并记录CPU运行时间;

•重复前三个步骤,直到可以接受仿真速度;

在B部分中,您将使用+ rad VCS优化开关来改善仿真性能。

•仿真编解码器设计并记录CPU运行时间;

•使用+ rad开关编译和仿真编解码器并记录CPU运行时间;

三.实验方法

1.进入到lab6/文件夹中;

cd /home/zwj/wendang/IC/VCS_study/VCS_guide/vcs_lab.cn_vcs_lab/lab6/parta/

2.编译和仿真

vcs –f codec.f CAM.v fileio.o –R

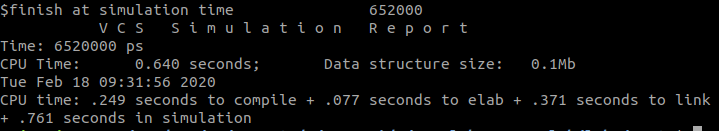

3.记录CPU时间和数据结构大小

4.使用+prof开关,记录CPU运行的时间的相关参数

vcs –f codec.f cam.v fileio.o –R +prof #这里面+prof开关表示在VCS仿真的过程中生成一个VCS.prof文件,记录设计中最耗CPU时间的module,层次和verilog结构

5.评估编解码器仿真性能

使用编辑器打开vcs.prof文件。