64兆位串行SPI FLASH存储器

1.常规介绍

W25Q64BV(64兆位)串行FLASH存储器为一个空间大小,引脚,功耗限制的系统提供解决方案。25Q系列的灵活性和性能良好超越了普通的串行FLASH设备。该芯片是理想的代码跟踪到RAM,通过两路或四路SPI(XIP)直接执行代码来存储声音,文字,数据等,只需要一个2.7V到3.6V的供电,在活跃状态是电流消耗可以低至4mA,掉电模式下可以低到1uA。所有的设备都提供节省面积的封装。

W25Q64BV拥有32768页的可编程阵列(每页可写256字节数据)。一次最大可编辑256字节。每页可以被分成16组扇区擦除,每个扇区分成128(32KB区擦除),或256个(64KB区擦除)或者整个擦除(整个芯片擦除)。W25Q64BV有2048个可擦除扇区和128个可擦除区块。最小4KB的扇区擦除拥有更好的灵活性在数据和参数存储上。

W25Q64BV支持标准SPI,和高性能双路/四路数据作为双路/四路SPI:串行时钟,片选,数据I/O0(DI),I/O1(DO),I/O2(/WP),和IO3(/HOLD)。在使用快速读双路或四路输出设备时,SPI时钟频率最高支持80MHz和160MHz的时钟速率在双路SPI模式下和320MHz的时钟速率在四路输出模式下,发送器速率可以胜过8位和16位并行FLASH存储器。连续读模式考虑到高效的内存访问只用了8个时钟的指令开销用来读一个24位的数据,允许真XIP(excute in place)。

一个保持引脚,写保护引脚和可编程写保护,可以通过顶层或底层阵列控制,提供更好的灵活性,另外,设备支持一个第一无二的64位JEDEC标准制造商和设备标识。

2.特性

*SPIFlash存储器家族

-W25Q64BV:64兆位/8兆字节(8388608)

-每页由有256字节可编程字节

*标准,双路/四路SPI

-标准SPI:CLK,/CS,DI,DO,/WP,/Hold

-双路SPI:CLK,/CS,IO0,IO1,/WP,/Hold

-四路SPI:CLK,/CS,IO0,IO1,IO2,IO3

*最高表现串行SPI

-最高是普通的串行Flash的6倍

-80Mhz 工作时钟

-160MHz等效时钟(双路SPI模式下)

-320MHz等效时钟(四路SPI模式下)

-40MB/s连续数据发送速率

*高效“连续读模式”

-低指令消耗

-只需要8个时钟的地址存储

-支持真XIP(EXECUTE in place)

-胜过16位并行FLASH

*低功耗,款温度范围

-单电源供电(2.7V-3.6V)

-4mA 活动电流,掉电模式下小于1uA

- -40℃到85℃工作范围

*灵活的4KB扇区架构

-统一扇区擦除(4K字节)

-区擦除(32K和64K字节)

-一次可编程256K字节

-十万次擦写次数

-每个芯片有独一无二的ID

*空间高效封装

-8引脚SOIC 208mil

-8引脚PDIP 300mil

-8焊盘 WSON 8*6mm

-16引脚 SOIC 300mil

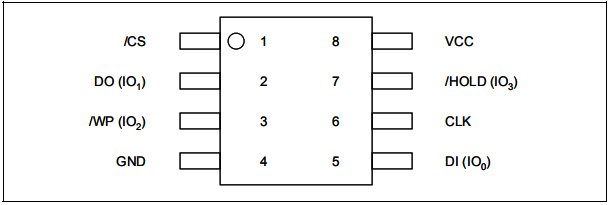

3.引脚配置 SOIC 208mil

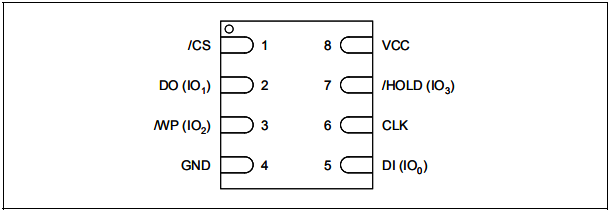

4.焊盘配置 WSON 8*6mm

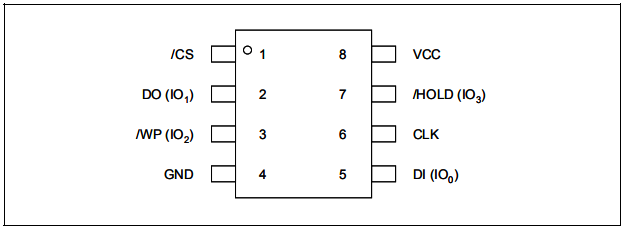

5.焊盘配置 PDIP 300mil

6.引脚介绍 SOIC 208mil PDIP300mil WSON 8*6mm

| 引脚号 | 引脚名称 | I/O | 功能 |

| 1 | /CS | I | 片选输入 |

| 2 | DO(IO1) | I/O |

数据输出(数据输入输出1)*1 |

| 3 | /WP(IO2) | I/O | 写保护输入(数据输入输出2)*2 |

| 4 | GND |

地 | |

| 5 | DI(IO0) | I/O | 数据输入(数据输入输出0)*1 |

| 6 | CLK | I | 串行时钟输入 |

| 7 | /HOLD(IO3) | I/O | 保持输入(数据输入输出3)*2 |

| 8 | VCC | 供电 |

*1 IO0和IO1用在标准和双路SPI模式

*2 I/O0到I/O3用在四路SPI模式下

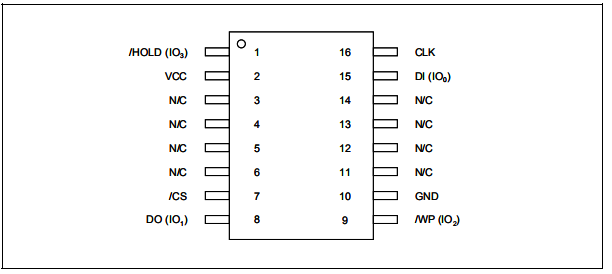

7.引脚配置 SOIC 300mil

8.引脚介绍SOIC300mil

| 引脚号 | 引脚名称 | I/O | 功能 |

| 1 | /HOLD(IO3) | I/O | 保持输入(数据输入输出3)*2 |

| 2 | VCC | 供电 | |

| 3 | NC |

不连接 | |

| 4 | NC | 不连接 | |

| 5 | NC | 不连接 | |

| 6 | NC | 不连接 | |

| 7 | /CS |

I | 片选 |

| 8 | DO(IO1) | I/O | 数据输出(数据输入输出1)*1 |

| 9 | /WP(IO2) | I/O | 写保护输入(数据输入输出2)*2 |

| 10 | GND | 地 | |

| 11 | NC | 不连接 | |

| 12 | NC | 不连接 | |

| 13 | NC | 不连接 | |

| 14 | NC | 不连接 | |

| 15 | DI(IO0) | I/O | |

| 16 | CLK | I | 串行时钟输入 |

*1 IO0和IO1用在标准和双路SPI模式

*2 I/O0到I/O3用在四路SPI模式下

8.1封装类型

W25Q64BV提供一个8引脚SOIC(封装代码:SS)和8*6mmWSON(封装代码:ZE),300mil 8引脚是另一种封装类型,W25Q64还有一种16引脚300mil塑料SOIC封装(封装代码:SF)。封装图和大小在数据手册的结尾阐述.

8.2片选(/CS)

SPI片选(/CS)引脚使能或屏蔽设备,当/CS为高电平时,此设备将被屏蔽并且串行数据输出(DO,或IO0,IO1,IO2,IO3)引脚处于高阻态。当处于屏蔽状态时,在内部擦除信号到来之前,该设备的功率消耗出在待机等级,编程或者状态寄存器周期正处于编程过程中。当/CS引脚被拉低时,该设备将被选中,功率消耗会回到活动等级,且可以对设备进行读写。在上电后,在一个指令被接收前/CS必须从高到低转换,/CS引脚输入必须要到供电电源的电位水平在上电时。(详情见“写保护”),为了实现可以通过一个上拉电阻上拉到VCC。

8.3串行数据输入,输出和IO口(DI,DO,IO1,IO2,IO3)

W25Q64BV支持标准,双路和四路SPI。在串行时钟(CLK)的上升沿标准SPI指令使用单向DI(输入)用来写串行指令,地址或数据到设备。在串行时钟(CLK)的下降沿标准SPI也使用单向DO(输出)来读数据或状态。

在CLK的上升沿双路和四路SPI指令使用双向IO引脚来写串行指令,地址和数据到设备并且在CLK的下降沿读数据或者设备的状态。四路SPI指令要求非易失性QE位置一,见状态寄存器2,当QE=1,/WP引脚变成IO2且/HOLD引脚变成IO3。

8.4写保护(/WP)

写保护(/WP)引脚被用来避免状态寄存器被写。和状态寄存器的其他保护位(SEC,TB,BP2,BP1和BP0)还有状态寄存器保护位(SRP)一起使用,一部分或者整个寄存器 阵列被硬件保护。/WP引脚低电平有效。当状态寄存器2的QE位置位用作四路I/O,由于这个引脚被用作IO2,/WP引脚(硬件写保护)功能是无效的。

8.5保持(/HOLD)

/HOLD引脚允许在运行时被暂停,当/HOLD引脚被拉低且/CS是低电平,DO引脚将变成高阻态且DI引脚和CLK上的信号被忽略,当/HOLD被拉高时,设备会继续工作。/HOLD功能在多台设备共享SPI信号时大有用处。/HOLD低电平有效,当状态寄存器2 的QE位被设置位四路SPI模式时,/HOLD引脚功能无效,因为该引脚被用作IO3。

8.6串行时钟(CLK)

SPI串行时钟输入(CLK)引脚提供串行输入输出时钟.

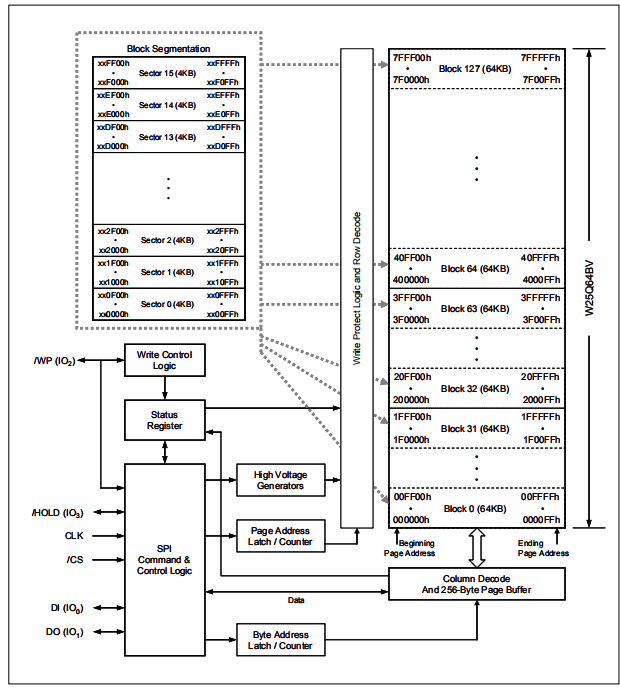

9.模块图

10.功能介绍

10.1SPI运营

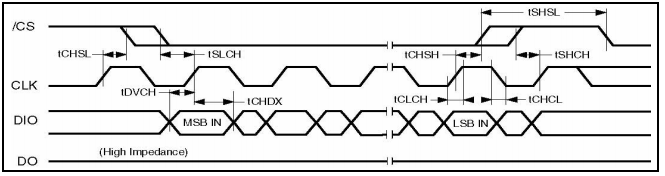

10.1.1标准SPI指令

W25Q64BV是使用四线SPI兼容总线:串行时钟:(CLK),片选(CS),串行数据输入(DI),串行数据输出(DO)。标准SPI指令是MCU在CLK的上升沿使用DI输入引脚串行写指令,地址,数据到设备。在CLK的下降沿用DO输出引脚从设备读取数据或状态。

SPI总线支持工作模式0(0,0)和3(1,1)。模式0和模式3的主要不同点在于当SPI总线朱发送器的CLK正常状态时数据不发送到串行FLASH。对模式0来说,CLK在/CS的下降/上升沿时为场低,而模式3在/CS的上升沿/下降沿为常高。

10.1.2双路SPI指令

W25Q64BV在使用“快速读双路输出或双路输入”提供双路SPI工作(3Bh和BBh)指令。这些指令允许数据发送到设备以两到三倍的普通串行FLASH设备。双路读指令理想情况下开机后快速下载代码到RAM或者直接通过SPI总线(XIP)执行非关键速度代码。当使用双路SPI指令的时候DI引脚和DO引脚变成双向I/O引脚:IO0和IO1。

10.1.3四路SPI指令

W25Q64BV在使用“快速读四路输出”时支持四路SPI指令,“快速读四路I/O”和八'进制字节读四路I/O'(6Bh,EBh和E3h指令),这些指令允许数据发送速率为普通串行FLASH的四到六倍。四路读指令提供有效的改善在连续发送和随机存取发送器速率允许快速代码映射到RAM或者直接通过SPI总线(XIP)执行。当使用四路SPI指令时,DI和DO引脚变成双向IO口IO0和IO1且/WP和/HOLD引脚变成IO2和IO3。四路SPI指令要求状态寄存器2的QE位被置位。

10.1.4保持功能

/HOLD信号允许W25Q64BV被暂停在被选中的情况下(CS=0)。保持功能可以在与其他设备共享SPI时钟和数据时使用。例如,考虑到如果当一个优先中断要求使用SPI总线时页缓冲器部分被写。在这种情况下,/HOLD功能可以保存指令状态和缓冲器中的数据,当下次总线被释放时,会回到中断的地方。/HOLD功能只在标准SPI和双路SPI模式下有效,不包括四路SPI模式。

开始/HOLD的条件,设备必须被选中(CS=0),/HOLD条件在时钟(CLK)低电平时产生一个下降沿的跳变位有效信号。在时钟(CLK)低电平时,/HOLD的上升沿跳变表示结束保持。如果CLK没有被提前拉低时保持会在下个时钟下降沿之后停止。在保持期间,串行数据输出(DO)是高阻态,还有串行数据输入(DI)和串行时钟(CLK)将被忽略。在整个“保持”(HOLD)工作期间片选信号应该保持选中状态(CS=0)来避免重置设备内部逻辑状态。

10.2写保护

在应用非易失性存储器是必须考虑到噪声的可能性和其他不利的系统条件可能破坏数据的完整性。为了解决这些问题,W25Q64BV提供一些方法来保护数据而必变意想不到的写。

10.2.1写保护特征

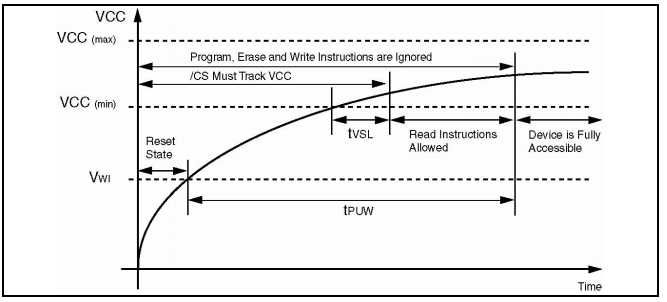

*当VCC小于临界值是设置重启

*在上电后延迟一段时间写屏蔽

*写使能/屏蔽指令和在编程和擦除后自动写屏蔽

*软件和硬件(/WP引脚)使用状态寄存器写保护

*使用掉电指令写保护

*在下一次上电之前,写保护

*一次编程(OTP)写保护

注:这些特征在特定的情况下发生,联系Winbond以获取细节。

根据上电或掉电,当VCC电压小于Vwl时,(详情见上电时序和电压等级),W25Q64BV产生一个复位条件。当复位时,所有的工作被禁止且没有指令被识别。在VCC电压值超过Vwl后才开始启动,所有的编程和擦写有关联的指令被禁止并保持一个Tpuw时间延时。包括写使能,页编程,扇区擦除,区块擦除,片擦除和写状态寄存器指令。注意在启动后片选必须跟随VCC供电的电压等级直到VCC-min和Tvsl时间延时到来。可以使用片选引脚连接一个上拉电阻来实现上述。

在启动之后设备自动设置状态寄存器写使能锁定位(WEL)置零来使设备处于写禁止状态,所以在页写,扇区擦除或片擦除或写状态寄存器指令之前,必须要写使能。在编译完一个程序,擦除或写指令之后,写使能锁定(WEL位)自动清零,设设备处于写禁止状态。

软件控制写保护促进了使用写状态寄存器指令和设置状态寄存器保护(SRP0,SRP1)和区块保护(SEC,TB,BP2,BP1,BP0)位。这些设置允许一个位置或整个存储区配置为只读。配合写保护位(/WP)使用,改变状态寄存器来使能或禁止硬件控制。看状态寄存器已获得更多的信息。另外,当所有的指令被忽略除了退出掉电模式指令,掉电指令提供一个额外的写保护等级。

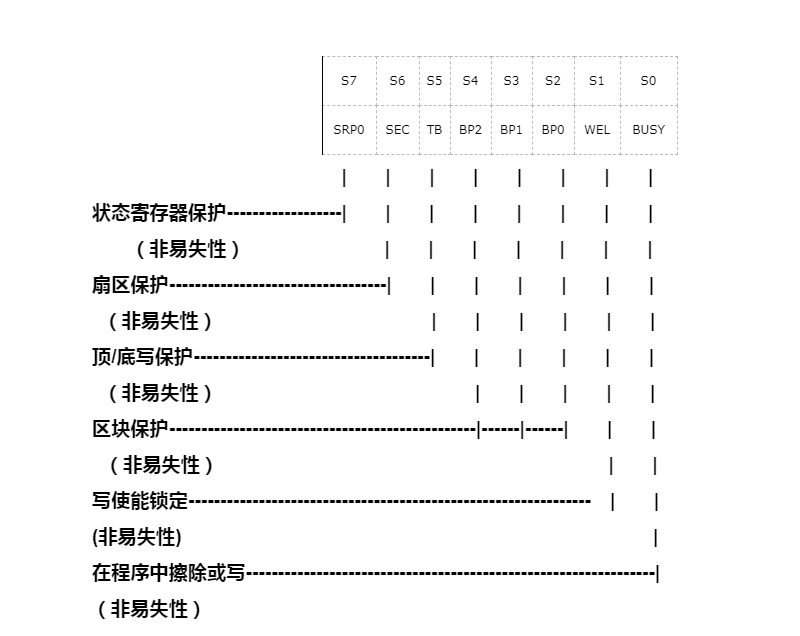

11.控制和状态寄存器

读状态寄存器1和状态寄存器2指令在FLASH存储器阵列被用来提供有效的状态,如果设备处于写使能或写禁止状态,写保护状态或四路SPI设置。写状态寄存器指令可以改被用来配置设备写保护和四路SPI设置。写状态寄存器的方法是控制非易失性状态寄存器的保护位(SRP0,SRP1),写使能命令,和(/WP)引脚的一些情况。

11.1状态寄存器

11.1.1忙

忙(只读位)是状态寄存器的(S0)位,当设备执行一个页写,扇区擦除,区擦除,片擦除或写状态寄存器指令时置1。在这个时间里,设备会忽视发送过来的指令除了读状态寄存器指令和擦除延缓(暂停)指令(Tw,Tpp,Tse,Tbe,Tce在AC特征中)。当程序,擦除,写状态寄存器完成后,BUSY位将被清零表明设备准备好了可已接收下一个指令。

11.1.2写使能锁定(WEL)

写使能锁定(WEL)(只读位)(S1),在执行一个写使能指令之后置一。写使能锁定转状态位在设备写禁止后清零。写禁止状态发生在上电之前或者在任意下列指令中(写禁止,页写,扇区擦除,区块擦除,片擦除和写状态寄存器)的一个结束后。

11.1.3 区块保护位(BP0,BP1,BP2)

区块保护位(BP2,BP1,BP0)是状态寄存器的非易失性读/写位(S4,S3,S2),且提供写保护控制和状态。区块保护位可以通过写状态寄存器指令设置(见AC特性中Tw)。全部,没有或某位置存储器阵列可以被保护通过程序或擦除指令(见状态寄存器存储保护表格)。工厂出厂设置区块保护位为0,没有阵列被保护。

11.1.4顶层/底层区块保护(TB)

非易失性顶层/底层为(TB)控制当区块保护位(BP0,BP1,BP2,)保护从顶(TB=0)或者从底(TB=1)开始的阵列,就像状态寄存器存贮保护列表里的一样。工厂出厂位(TB=0)。TB位可以通过写状态寄存器指令的SRP0,SRP1和WEL位实现。

11.1.5扇区/区块保护(SEC)

非易失性扇区保护位(SEC)通过控制区块保护位(BP2,BP1,BP0)保护4KB扇区(SEC=1)或者64KB区块(SEC=0)从顶部(TB=0)开始或者从底部(TB=1)开始的阵列,如状态寄存器存储保护列表里一样,默认SEC设置为SEC=0;

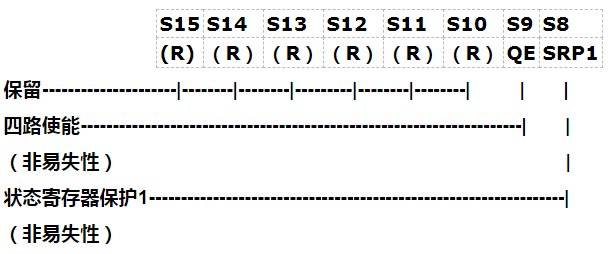

11.1.6状态寄存器保护(SRP1,SRP0)

状态寄存器保护位(SRP1和SRP0)是状态寄存器中的(S8和S7位)非易失性读/写位。SRP位控制写保护的方法:软件保护,硬件保护,供电阈值下保护或者OTP保护(一次编程保护)。

| SRP1 | SRP0 | /WP | 状态寄存器 | 介绍 |

| 0 | 0 | x | 软件保护 | /WP没有控制效果。状态寄存器在写使能指令字后可以写。WEL=1。(出厂默认值) |

| 0 | 1 | 0 | 硬件保护 | /WP为低电平,状态寄存器锁定,不可以被写入。 |

| 0 | 1 | 1 | 硬件不保护 | 当/WP引脚为高电平,状态寄存器解锁且在写使能指令之后可以被写入。WEL=1。 |

| 1 | 0 | x | 供电电压阈值下保护 | 状态寄存器被保护且不能被写入直到下一个掉电/上电循环。 |

| 1 | 1 | x | 单次编程保护 | 状态寄存器完全被保护且不可被写入。 |

注:

1.非特殊情况下有效,联系Winbond获取细节。

2.当(SRP1,SRP0)=(1,0),一个掉电,上电循环会将(SRP1,SRP0)置零(0,0)。

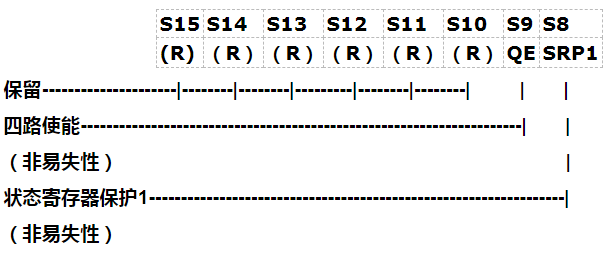

11.1.7四路使能(QE)

四路使能(QE)位位于状态寄存器的S9为非易失性读/写位用来控制四路SPI工作。当QE位被设置为0(出厂默认值0,),/WP和/HOLD引脚被使能。当QE位为1时,四路SPI模式的IO2和IO3被使能。

警告:在标准SPI模式或双路SPI模式期间,当/WP或/HOLD位上拉到电源或下拉到第的时候,QE位一定 不要置一。

状态寄存器1

状态寄存器2

11.1.8状态寄存器存储保护

| 状态寄存器(1) | W25Q64(64兆位)存储器保护 | |||||||

| SEC | TB | BP2 | BP1 | BP0 | 区块(s) | 地址 | 密度 | 位置 |

| X | X | 0 | 0 | 0 | 无 | 无 | 无 | 无 |

| 0 | 0 | 0 | 0 | 1 | 126&127 | 7E0000h-7FFFFh | 128KB |

最上1/64 |

| 0 | 0 | 0 | 1 | 0 | 124~127 |

7C0000h – 7FFFFFh

|

256KB

|

最上1/32 |

| 0 | 0 | 0 | 1 | 1 |

120 ~ 127

|

780000h – 7FFFFFh

|

512KB

|

最上1/16

|

| 0 | 0 | 1 | 0 | 0 |

112 ~ 127

|

700000h – 7FFFFFh

|

1MB

|

最上 1/8

|

| 0 | 0 | 1 | 0 | 1 |

96 ~ 127

|

600000h – 7FFFFFh

|

2MB

|

最上 1/4

|

| 0 | 0 | 1 | 1 | 0 |

64 ~ 127

|

400000h – 7FFFFFh

|

4MB

|

最上1/2

|

| 0 | 1 | 0 | 0 | 1 | 0&1 |

000000h – 01FFFFh

|

128KB

|

最下 1/64

|

| 0 | 1 | 0 | 1 | 0 | 0~3 |

000000h – 03FFFFh

|

256KB

|

1/32

|

| 0 | 1 | 0 | 1 | 1 | 0~7 |

000000h – 07FFFFh

|

512KB

|

1/16

|

| 0 | 1 | 1 | 0 | 0 | 0~15 |

000000h – 0FFFFFh

|

1MB

|

1/8

|

| 0 | 1 | 1 | 0 | 1 | 0~31 |

000000h – 1FFFFFh

|

2MB

|

1/4

|

| 0 | 1 | 1 | 1 | 0 | 0~63 |

000000h – 3FFFFFh

|

4MB

|

1/2

|

| X | X | 1 | 1 | 1 | 0~127 |

000000h – 7FFFFFh

|

8MB

|

所有 |

| 1 | 0 | 0 | 0 | 1 | 127 |

7FF000h – 7FFFFFh

|

4KB

|

顶层区块 |

| 1 | 0 | 0 | 1 | 0 | 127 |

7FE000h – 7FFFFFh

|

8KB

|

顶层区块 |

| 1 | 0 | 0 | 1 | 1 | 127 |

7FC000h – 7FFFFFh

|

16KB

|

顶层区块 |

| 1 | 0 | 1 | 0 | X | 127 |

7F8000h – 7FFFFFh

|

32KB

|

顶层区块 |

| 1 | 1 | 0 | 0 | 1 | 0 |

000000h – 000FFFh

|

4KB | 底层区块 |

| 1 | 1 | 0 | 1 | 0 | 0 |

000000h – 001FFFh

|

8KB | 底层区块 |

| 1 | 1 | 0 | 1 | 1 | 0 |

000000h – 003FFFh

|

16KB | 底层区块 |

| 1 | 1 | 1 | 0 | X | 0 |

000000h – 007FFFh

|

32KB

|

底层区块 |

注:x=不需要管

11.2指令

W25Q64BV指令包括27个基础指令(全部通过SPI总线控制)(见指令设置表格)。指令咋片选的下降沿开始。最初的字节数据循着时钟通过DI输入来提供指令代码。DI输入线上的数据(高位在前)在时钟的上升沿采样。

指令长度从一个字节到多个字节不等,可以更在地址字节后面,数据自己,虚拟字节(不需要在意),或者在某种情况下,组合。指令在/CS的上升沿编译。每一个指令的时钟相关时序图下图列出。所有的读指令在任意时钟位可以被编译。然而,所有写指令,程序或者擦除必须在字节边界上完成(在完成整个8位/CS拉高)否则这个指令会被终止。这个功能会防止设备在无意间被写。另外,在存储器在擦除或编程 的过程中,或者在状态寄存器被写的过程中,所有的指令除了读状态寄存器都会被忽略直到编程或擦除周期完成。

11.2.1制造商和设备鉴别

| 制造商ID | (M7-M0) | |

| Winbond串行FLASH | EFh | |

| 设备ID | (ID7-ID0) | (ID15-ID0) |

| 指令 | ABh,90h | 9Fh |

| W25Q64BV | 16h | 4017h |

11.2.2指令设置表格1(1)

| 指令名称 | 字节1 (代码) |

字节2 | 字节3 | 字节4 | 字节5 | 字节6 |

| 写使能 | 06h | |||||

| 写禁止 | 04h | |||||

| 读状态寄存器1 | 05h | (S7-S0)(2) | ||||

| 读状态寄存器2 | 35h | (S15-S8)(2) | ||||

| 写状态寄存器 | 01h | (S7-S0) | (S15-S8) | |||

| 页编程 | 02h | A23-A16 | A15-A8 | A7-A0 | (D7-D0) | |

| 四页写 | 32h | A23-A16 | A15-A8 | A7-A0 | (D7-D0,...)(3) | |

| 区块擦除(64KB) | D8h | A23-A16 | A15-A8 | A7-A0 | ||

| 区块擦除(32KB) | 52h | A23-A16 | A15-A8 | A7-A0 | ||

| 扇区擦除(4KB) | 20h | A23-A16 | A15-A8 | A7-A0 | ||

| 片擦除 | C7h/60h | |||||

| 擦除暂停 | 75h | |||||

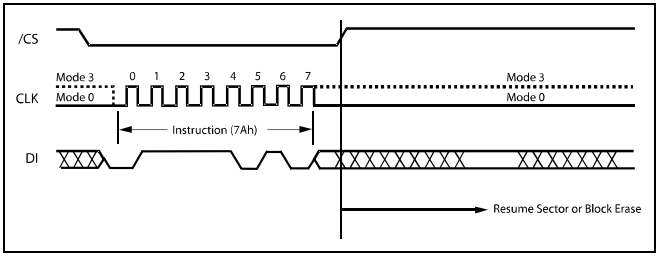

| 擦除恢复 | 7Ah | |||||

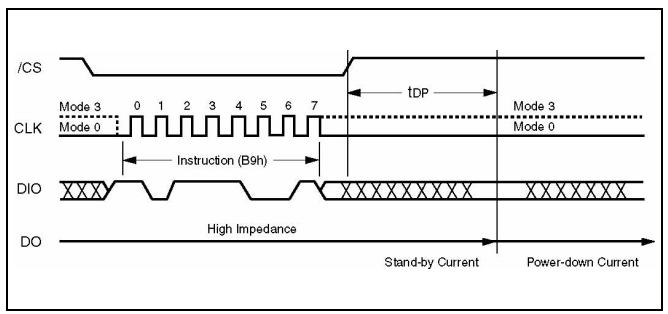

| 掉电 | B9h | |||||

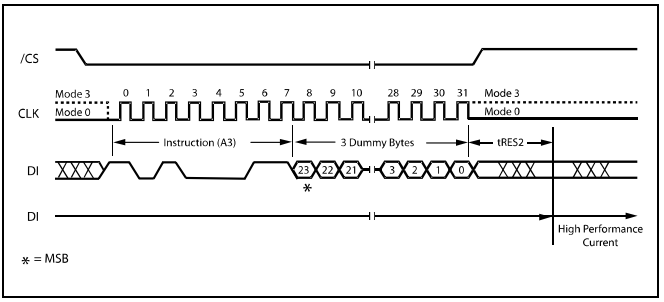

| 高性能模式 | A3h | 虚拟字节 | 虚拟字节 | 虚拟字节 | ||

| 连续读模式复位(4) | FFh | FFh | ||||

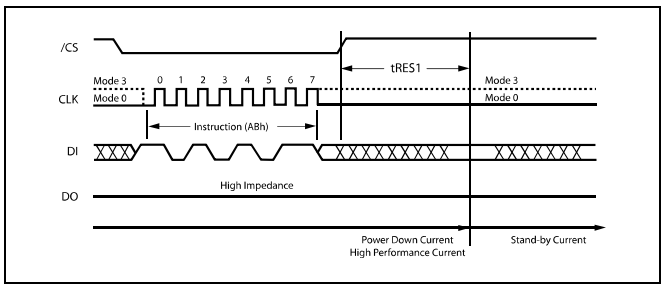

| 掉电恢复或HPM/设备ID | ABh | 虚拟字节 | 虚拟字节 | 虚拟字节 | (ID7=ID0)(5) | |

| 制造商/设备ID | 90h | 虚拟字节 | 虚拟字节 | 00h | (MF7-MF0) | (ID7-ID0) |

| 读唯一ID(7) | 4Bh | 虚拟字节 | 虚拟字节 | 虚拟字节 | 虚拟字节 | (ID63-ID0) |

| JEDEC ID | 9Fh | (MF7-MF0) 制造商 |

(ID15-ID0) 存贮类别 |

(ID7-ID0) 能力 |

||

注:

1.数据字节是通过高位在前以为得到的。括号中的字节表示正在通过DO引脚读取设备上的数据。

2.状态寄存器的内容会存在直到/CS终止指令。

3.四爷片成输入数据

IO0=(D4,D0,...)

IO1=(D5,D1,...)

IO2=(D6,D2,...)

IO3=(D6,D3,...)

4.这个指令在使用双路或四路“连续读模式”时推荐使用。详情见11.2.29

5.设备ID重复直到/CS终止指令

6.查看制造商和设备标书表格得到设备ID信息。

7.在特殊的需求下使用。

11.2.3指令设置表格2(读指令)

| 指令名称 | 字节1 (代码) |

字节2 | 字节3 | 字节4 | 字节5 | 字节6 |

| 读数据 | 03h | A23-A16 | A15-A8 | A7-A0 | (D7-D0) | |

| 快速读 | 0Bh | A23-A16 | A15-A8 | A7-A0 | 虚拟字节 | (D7-D0) |

| 快速读双输出 | 3Bh | A23-A16 | A15-A8 | A7-A0 | 虚拟字节 | (D7-D0,...)(1) |

| 快速读双路I/O | BBh | A23-A8(2) | A7-A0,M7-M0(2) | (D7-D0,...)(1) | ||

| 快速读四路输出 | 6Bh | A23-A16 | A15-A8 | A7-A0 | 虚拟字节 | (D7-D0,...)(3) |

| 快速读四路I/O | EBh | A23-A0,M7-M0(4) | (X,X,X,X,D7-D0,...)(5) | (D7-D0,...0)(3) | ||

| 三字节读四路I/O | E3h |

A23-A0, M7-M0(4)

|

(D7-D0, …)(3)

|

|||

注:

1.双数据输出

IO0=(D6,D4,D2,D0)

IO1=(D7,D5,D3,D1)

2.双地址输入

IO0=A22,A20,A18,A16,A14,A12,A10,A8,A6,A4,A2,A0,M6,M4,M2,M0

IO1=A23,A21,A19,A17,A15,A13,A11,A9,A7,A5,A3,A1,M7,M5,M3,M1

3.四路数据输出

IO0=(D4,D0,...)

IO1=(D5,D1,...)

IO2=(D6,D2,...)

IO3=(D7,D3,...)

4.四路地址输入

IO0=A20,A16,A12,A8,A4,A0,M4,M0

IO1=A21,A17,A13,A9,A5,A1,M5,M1

IO2=A22,A18,A14,A10,A6,A2,M6,M2

IO3=A23,A19,A15,A11,A7,A3,M7,M3

5.快速读四路I/O数据

IO0=(X,X,X,X,D4,D0,...)

IO1=(X,X,X,X,D5,D1,...)

IO2=(X,X,X,X,D6,D2,...)

IO3=(X,X,X,X,D7,D3,...)

6.最低四位地址必须为0.(A0,A1,A2,A3=0,0,0,0,)

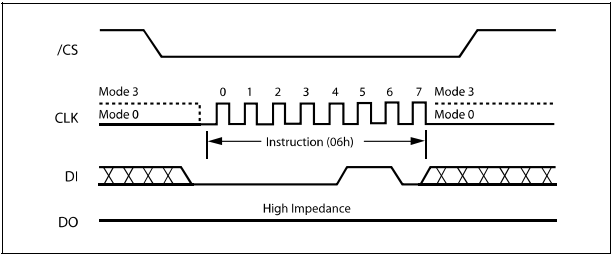

11.2.4写使能(06h)

写使能指令设置在状态寄存器(S1)的写使能锁定位(WEl)为1。WEL位必须在每一次页编写,扇区擦除,区块擦除,片擦除和写状态寄存器之前优先设置。写使能指令在每次/CS位低的时候进入,在CLK的上升沿将指令代码“06h”通过DI移位发送到设备,然后/CS拉高。

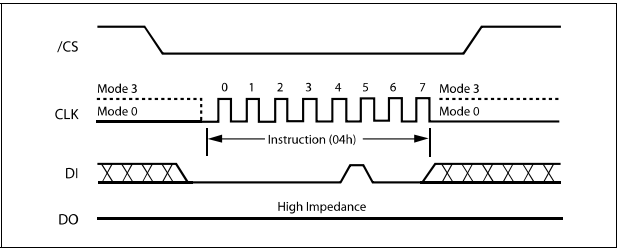

11.2.5写禁止(04h)

写禁止指令将状态寄存器中的写使能锁定位复位为0。写禁止指令在/CS位低的时候写入,通过DI引脚移位发送指令代码“04h”到设备,然后/CS拉高。注意,WEL位在上电,写状态寄存器,页编程,扇区擦除,区块擦除和片擦除指令完成之后自动复位。

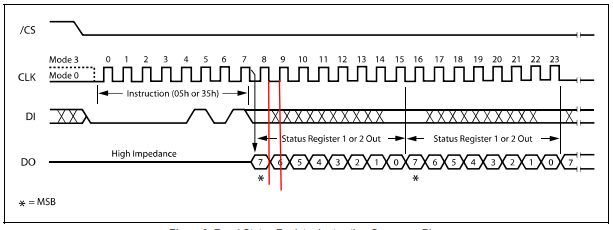

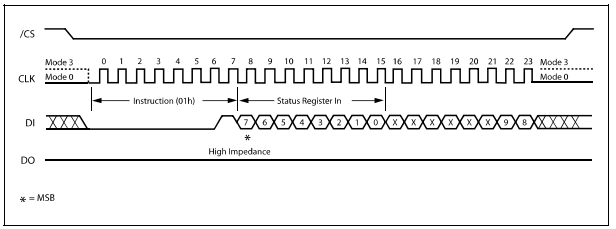

11.2.6读状态寄存器1(05h)和读状态寄存器2(35h)

读状态寄存器指令允许8位状态寄存器被读。该指令在/CS拉低后在CLK的上升沿通过DI引脚移位指令代码“05h”到状态寄存器1和“35h”到状态寄存器2。在CLK的下降沿通过DO(MSB在前)将状态寄存器位移出。

状态寄存器位包括BUSY,WEL,BP2-BP0,TB,SEC,SRP0,SRP1,和QE位。

读状态寄存器指令可以在任何时间使用,甚至在编程,擦除或写状态寄存器的时候。这要求监视BUSY位来决定当整个周期完成后是否要接收其他指令。状态寄存器可以连续读,如图所示,该指令通过将/CS引脚拉高来完成。

11.2.7写状态寄存器(01h)

写状态寄存器指令允许状态寄存器被写。一个写使能指令在设备收到写状态寄存器指令之前发送(状态寄存器WEL位等于1)。一旦写使能,该指令会在/CS拉低时,发送指令代码“01h”之后写状态寄存器数据字节如下图所示。

只有非易失性状态寄存器位SRP0,SEC,TB,BP2,BP1,BP0(状态寄存器1的S7,S5,S4,S3,S2)和QE,SRP1(状态寄存器2的S9,S8)可以被写。所有其他状态寄存器位位只读且不可以通过写状态寄存器指令。

/CS引脚必须在第八个或第六个数据位接收到之后必须被拉高。如果没有则完成写状态寄存器指令将不会执行。如果/CS位在第八个时钟(和25系列相配)拉高,QE位和SRP1位将被清零。在/CS拉高之后,自定时写状态寄存器周期将会开始Tw的持续时间(见AC特性)。在写状态寄存器周期内,读状态寄存器指令仍然可以被接收用来检查BUSY状态位。在写状态寄存器期间,BUSY位为1且在写状态寄存器周期接收后准备接收下一次指令的时候清零。在写寄存器周期结束后,写使能锁定位(WEL)清零。

写状态寄存器指令允许区块保护位(SEC,TB,BP2,BP1,BP0)设置为保护所有,某位置,或不保护存储器,来防止擦除或编程指令。保护区域变成只读(见状态寄存器存储器保护列表和介绍)。这些位和写保护位(/WP),阈值锁定或OTP组合使用去禁止写状态寄存器。参考11.1.6.出厂默认所有的状态寄存器为0。

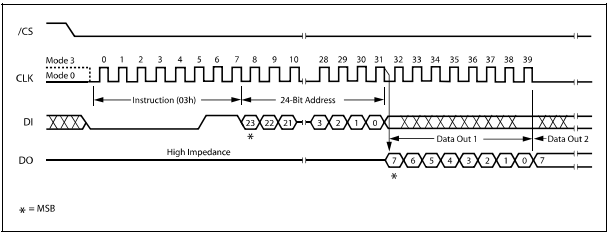

11.2.8读数据(03h)

读数据指令允许一个或多个字节数据从存储器中按顺序读。该指令在/CS引脚拉低后开始且紧接着移位发送指令代码“03h”,后面这时通过DI引脚发送的24位地址(A23-A0)。代码和地址都在CLK的上升沿采集。在地址接收之后,地址所对应的存储器数据字节会在CLK的时钟下降沿从DO引脚移出(高位在前)。在每个数据字节移出后地址会自动增加到下一个更高的地址因此达到一个数据流。这意味着整个存储器可以由一个指令访问,只要时钟在继续。该指令通过/CS引脚拉高来完成。

11.2.9快速读(0Bh)

快速读指令和读指令 很相似除了快速读可以工作在更高的时钟Fr(见AC特性)。这是在24位地址发送后使用八个空时钟如图。这个空是综合功能允许设备内部电路设置初始地址话费额外的时间。在虚拟时钟期间,不需要管DO引脚上的数据。

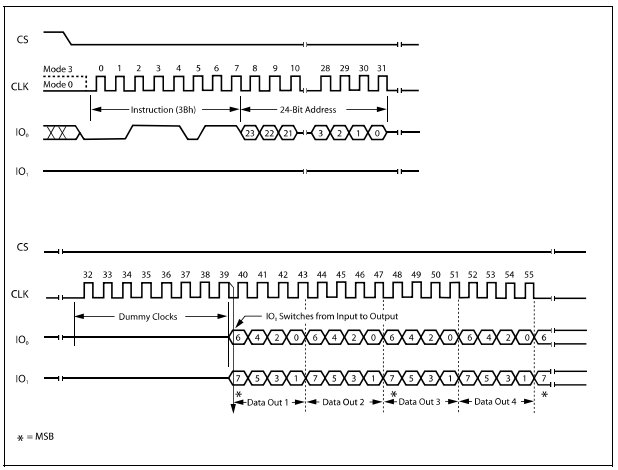

11.2.10快速读双路输出(3Bh)

快速读双路输出(3Bh)指令和标准快速读指令相似,除了数据输出在两个引脚上,IO0和IO1。

这使得数据从W25Q64BV发送速率是标准SPI设备的两倍。快速双路输出指令是理想的设备在上电时从FLASH把代码狭隘到RAM或用于将代码段缓存到RAM中以备应用程序使用。

和快速读指令相似,快速低双路输出指令可以工作在更高的频率Fr下(见交流特性),这个也是通过在24位地址后增加八个虚拟时钟来实现的,虚拟时钟允许设备的内部电路在建立内部地址时花费更多的时间。在虚拟时钟的期间,数据不需要在意。然而,IO0引脚应该位优先高阻态在第一个数据输出时钟的下降沿。

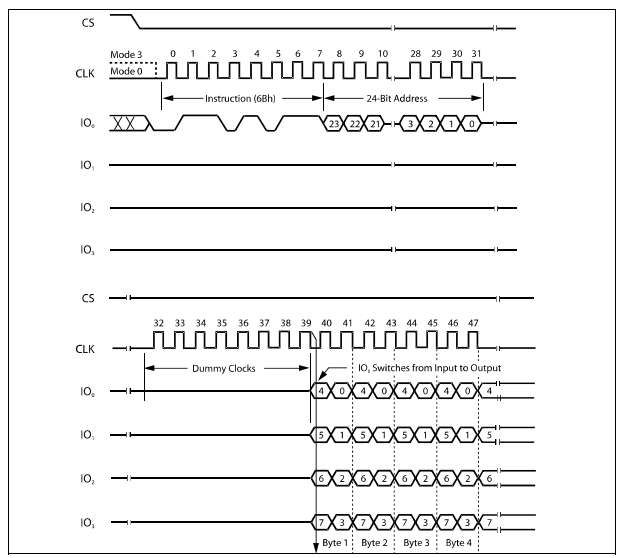

11.2.11快速读四路输出(6Bh)

快速读四路输出指令(6Bh)和快速读两路输出(3Bh)相似处理数据输出时四个引脚:IO0,IO1,IO2,IO3.在设备接收四路输出指令(状态寄存器位QE=1)之前,状态寄存器2的四路使能位必须执行, 快速读四路输出指令允许数据W25Q64BV发送数据以四倍标准SPI设备的速率。

快速读四路输出指令可以工作在更高的可用频率Fr(见交流特性)。这个也是通过在24位地址后增加八个虚拟时钟来实现的,虚拟时钟允许设备的内部电路在建立内部地址时花费更多的时间。在虚拟时钟的期间,数据不需要在意。然而,IO0引脚应该位优先高阻态在第一个数据输出时钟的下降沿。

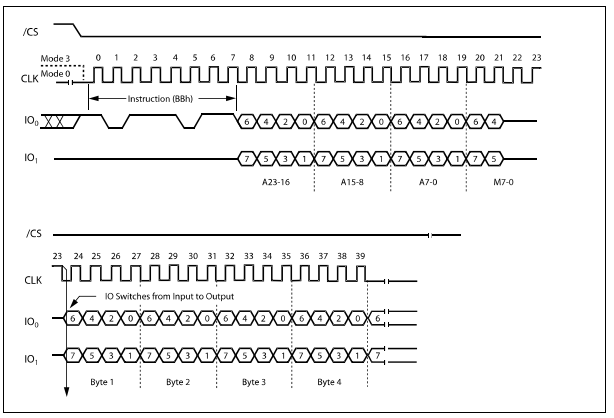

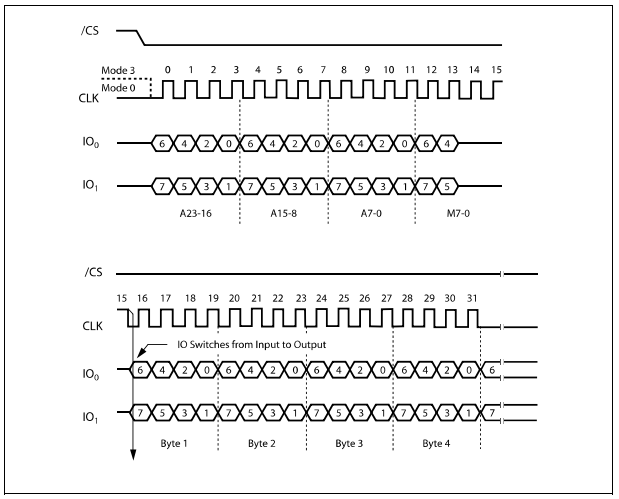

11.2.12快速读双路I/O(BBh)

快速读读双路读I/O(BBh)指令允许改进的随机访问,同时保持两个引脚,IO0和IO1。可快速读上路输出(3Bh)相似,但每个周期都需要输入地址位(A23-A0)留两位的空间。在某些应用中,直接使用双路SPI的XIP来减少指令开销。为了确保最优的表现,高效率模式(HPM)指令(A3h)必须先执行一次,先于快速读双路I/O指令。

"连续读模式下"的快速读双路I/O

快速读双路I/O指令可以通过在24位地址之后设置“连续读模式”位 (M7-M0)来进一步减少指令开销,

如图所示。高四位(M7-M4)通过包括或排除第一个指令代码字节控制下一给快速读双路I/O的长度。低四位(M3-M0)不需要在意(x),然而,IO引脚在第一个数据输出时钟的下降沿应优先为高阻态。

如果“连续读模式”位(M7-M0)等于“Axh”,则下一个读双路I/O指令(在/CS上升然后下降之后)不使用指令(BBh)代码。如图所示。这使得指令序列减少到8个时钟且允许立刻读地址在/CS拉低之后。如果“连续读模式”位(M7-M0)是比“AX”大的任意值,下一个指令(在/CS拉高又拉低后)要求第一个字节指令代码,从而恢复正常模式。在执行正常指令之前“连续读模式”复位指令可以用来复位(M7-M0)。

快速读双路输入/输出指令系列(M7-M0=0xh或不等于Axh)

快速读双路输入/输出指令序列代码(M7-M0=Axh)

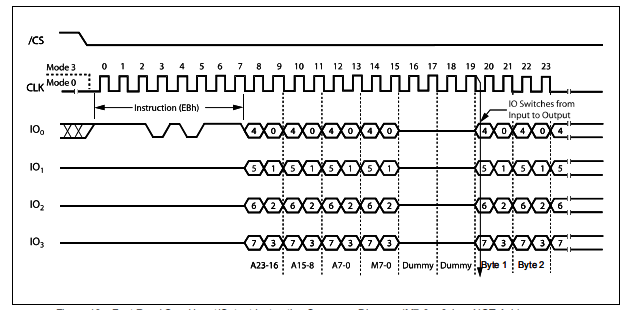

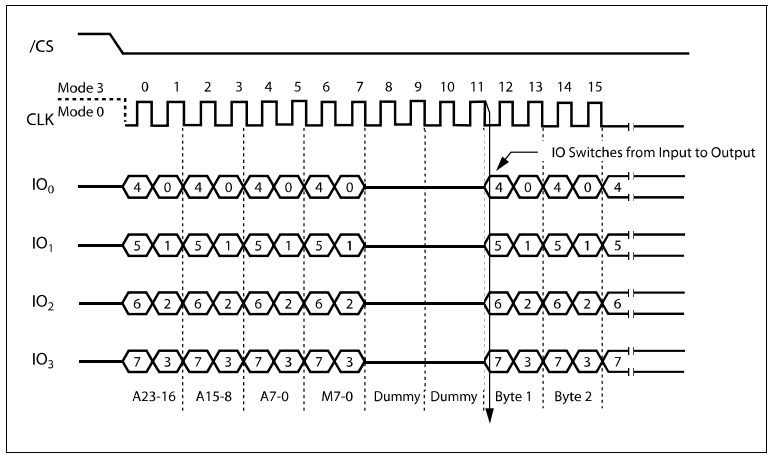

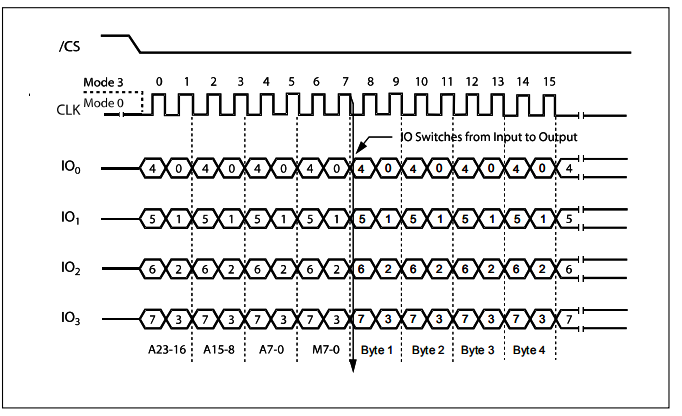

11.2.13快速读四路I/O(EBh)

快速读四路I/O(EBh)指令和快速读双路I/O指令(BBh)相似,除了地址和数据位输入输出时通过四路引脚IO0,IO1,IO2,IO3,和四个虚拟时钟在数据输出前。四路I/O引人注意的减少指令消耗支持更高的存储办法直接使用四路SPI模式的XIP。状态寄存器的四路使能位(QE)在读四路I/O指令的时候必须使能,为了确保更好的表现使用效率模式(HPM)指令(A3h)要提前执行一次,先于快速读四路I/O指令。

连续读模式下快速读四路I/O

快速读四路I/O指令可以通过在输入24位地址(A23-A0)之后设置“连续读模式”位(M7-M0)来进一步减少指令消耗,如图所示,高四位(M7-M4)通过包括或排除第一个指令代码字节来控制下一个高速I/O指令的长度。低四位(M3-M0)不需要在意(x),然而,IO引脚在第一个数据输出时钟的下降沿应优先为高阻态。

如果“连续读模式”位(M7-M0)等于“Axh”,则下一个读双路I/O指令(在/CS上升然后下降之后)不使用指令(BBh)代码。如图所示。这使得指令序列减少到8个时钟且允许立刻读地址在/CS拉低之后。如果“连续读模式”位(M7-M0)是比“AX”大的任意值,下一个指令(在/CS拉高又拉低后)要求第一个字节指令代码,从而恢复正常模式。在执行正常指令之前“连续读模式”复位指令可以用来复位(M7-M0)。

高速读四路输入/输出志林序列图表(M7-M0=0xh或不等于Axh

高速读四路输入/输出指令序列图表(M7-M0=Axh)

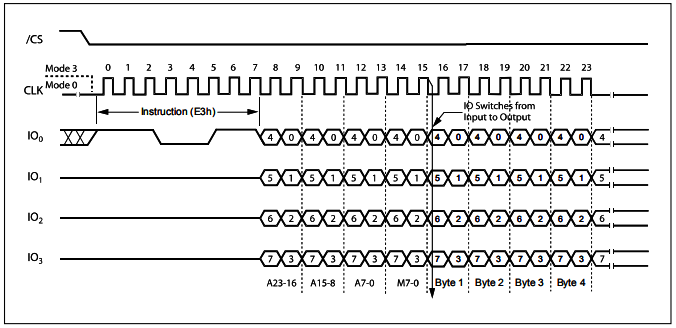

11.2.14八进制字节读四路I/O(E3h)

八进制字节读四路I/O(E3h)指令和快速读四路I/O(EBh)指令相似,除了低四位地址字节(A0,A1,A2,A3)必须等于0。结论就是,四个虚拟时钟不需要了。而且进一步减少了指令消耗,使得允许更快的代码执行的随机访问(XIP)。状态寄存器的四路使能位(QE)在读四路I/O指令的时候必须使能,为了确保更好的表现使用效率模式(HPM)指令(A3h)要提前执行一次,先于快速读四路I/O指令。

连续读模式下的八进制字节读四路I/O

八进制读四路I/O指令可以通过在输入24位地址(A23-A0)之后设置“连续读模式”位(M7-M0)来进一步减少指令消耗,如图所示,高四位(M7-M4)通过包括或排除第一个指令代码字节来控制下一个八进制字节读四路I/O指令的长度。低四位(M3-M0)不需要在意(x),然而,IO引脚在第一个数据输出时钟的下降沿应优先为高阻态。

如果“连续读模式”位(M7-M0)等于“Axh”,则下一个读八进制字节读四路I/O指令(在/CS上升然后下降之后)不使用指令(B3h)代码。如图所示。这使得指令序列减少到8个时钟且允许立刻读地址在/CS拉低之后。如果“连续读模式”位(M7-M0)是比“AX”大的任意值,下一个指令(在/CS拉高又拉低后)要求第一个字节指令代码,从而恢复正常模式。在执行正常指令之前“连续读模式”复位指令可以用来复位(M7-M0)。

八进制字节读四路I/O指令序列(M7-M0=0xh或不是Axh)

八进制字节读四路I/O指令序列(M7-M0=Axh)

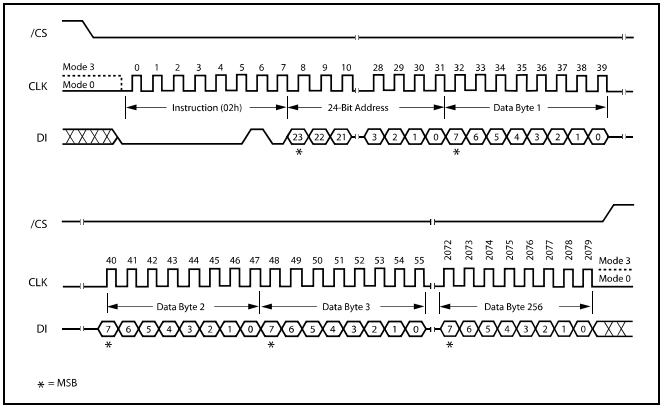

11.2.15页编程(02h)

页编程指令允许在之前擦写(FFh)存储器的位置编程从一个字节到256字节(一页)数据。一个写使能指令必须在设备接收到页编程之前执行(状态寄存器位WEL=1)。通过将/CS引脚压低,然后将指令码“02h”跟着一个24位地址(A23-A0)移动和至少一个数据字节,进入DI引脚。当数据发送到设备是/CS引脚必须保持低电平在整个长度的指令时间内。

如果整个256字节通过页编程写,最后的地址字节(最后的8位地址位)应该被置零。如果最后的地址字节不为零,且时钟的长度大于剩下的页的长度。若超过256个字节被发送到设备,地址将会回滚到地址的最开始且覆盖原来发送的内容。

如果写或者擦除指令,/CS引脚必须在最后一个字节的第八位拉高。如果没有这样做,页编程指令将被直线。在/CS拉高之后,自定时页编程指令将开始一段时长为Tpp的保持时间(将交流特性)。当页编程周期正在进行时,读状态寄存器指令可以被接收用来查看BUSY位。在页编程期间BUSY位为1,当整个循环结束后且准备接收另一个指令时清零,即BUSY=0,在页编程周期结束之后,状态寄存器的写使能锁定位(WEl)被清零。如果要写得多页被区块保护(BP

2,BP1,BP0)位保护,页编程指令不会被执行。

页编程指令时序图表

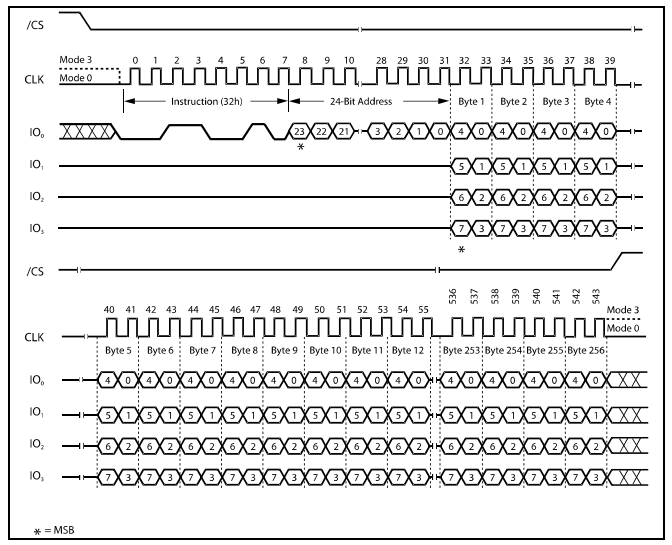

11.2.16四输入页编程(32h)

在前面擦除(FFh)指定位置使用四个引脚:IO0,IO1,IO2,IO3,四路页编程指令允许最大256自己的的数据被编程。四路页编程可以改善时钟速度小于5MhzPROM编程器和应用程序的的表现。拥有更快的时钟速度的系统不是很适合于四路页编程指令(状态寄存器1,WEL=1)原因是应为固有页面编程时间大于数据保持的时间。

为了使用四路页编程,状态寄存器2的四路使能位必须置一(QE=1)。在设备接收四路页编程指令之前写使能指令必须被执行(状态寄存器1,WEL=1)。这个指令开始于/CS处于低电平时,然后在24位地址(A24-A0)之后移位发送指令代码“32h”且至少一个数据字节,在IO引脚上。/CS引脚在整个指令长度期间且数据发送期间必须保持低电平。所有其他四路页编程的功能和标准页编程完全相同。四路页写指令时序如图所示。

四路输入页编程指令时序图表

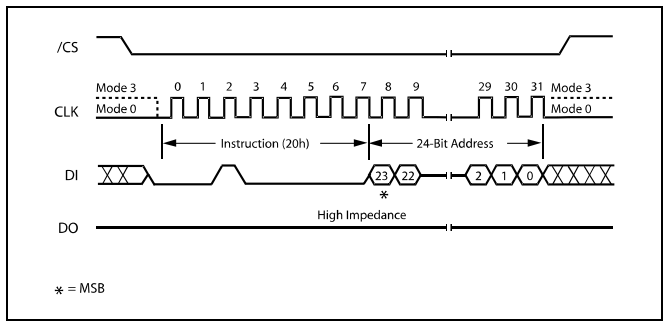

11.2.17扇区擦除(20h)

扇区擦除指令时在指定的扇区(4KB)之内设置所有的存储器擦除为FFh。一个写使能指令在设备收到扇区擦除指令之前必须被执行(状态寄存器位WEL必须等于1)。指令开始于/CS拉低的时候,且紧跟在24位地址后面移位发送指令代码“20h”。山区擦除指令时序如图所示。

/CS引脚在最后一个字节的第八位必须锁定位高电平。如果没有这样做,扇区擦除指令不会被执行。在/CS拉高时,自定时扇区擦除指令开始在一个时长为Tse的延时(见交流特性)。正在进行扇区擦除时,读状态寄存器指令可以被接受到用来检查BUSY位。BUSY在扇区擦除期间等于1,且在周期接束后且在等待下一个指令到来的时候拉低。在扇区擦除周期结束状态寄存器的写使能锁定位(WEL)位被清零。扇区擦除在区块保护(SEC,TB,BP2,BP1,BP0)位保护时不会被执行。

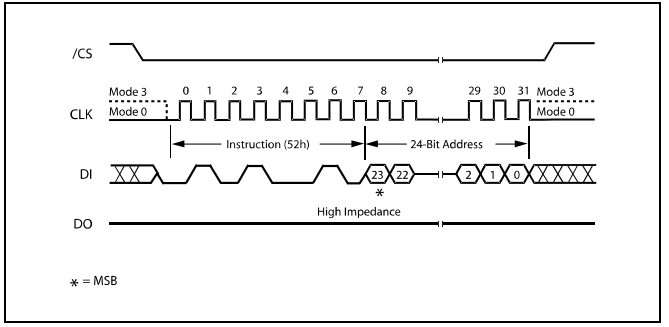

11.2.1832KB区块擦除(52h)

区块擦除指令在指定的区块内(32KB)设置所有存储区为1,(FFh)。在设备接收区块擦除指令之前必须先发送写使能指令(状态寄存器位WEL=1)。该指令在/CS引脚处于低电平时开始,且跟在24位区块地址(A23-A0)之后移位发送指令代码“52h”。区块擦除指令序列如图所示。

/CS引脚在最后一个字节的第八位必须锁定为1。如果不是这样,区块擦除指令将不会执行。在/CS引脚拉高后,自定时扇区擦除指令开始在一个时长为Tbe1的延时(见交流特性)。正在进行扇区擦除时,读状态寄存器指令可以被接受到用来检查BUSY位。BUSY在扇区擦除期间等于1,且在周期接束后且在等待下一个指令到来的时候拉低。在扇区擦除周期结束状态寄存器的写使能锁定位(WEL)位被清零。扇区擦除在区块保护(SEC,TB,BP2,BP1,BP0)位保护时不会被执行。

32KB区块擦除指令时序图

11.2.1964KB区块擦除(D8h)

区块擦除指令在指定的区块内(64KB)设置所有存储区为1,(FFh)。在设备接收区块擦除指令之前必须先发送写使能指令(状态寄存器位WEL=1)。该指令在/CS引脚处于低电平时开始,且跟在24位区块地址(A23-A0)之后移位发送指令代码“D8h”。区块擦除指令序列如图所示。

/CS引脚在最后一个字节的第八位必须锁定为1。如果不是这样,区块擦除指令将不会执行。在/CS引脚拉高后,自定时扇区擦除指令开始在一个时长为Tbe的延时(见交流特性)。正在进行扇区擦除时,读状态寄存器指令可以被接受到用来检查BUSY位。BUSY在扇区擦除期间等于1,且在周期接束后且在等待下一个指令到来的时候拉低。在扇区擦除周期结束状态寄存器的写使能锁定位(WEL)位被清零。扇区擦除在区块保护(SEC,TB,BP2,BP1,BP0)位保护时不会被执行。

64KB区块擦除指令时序图

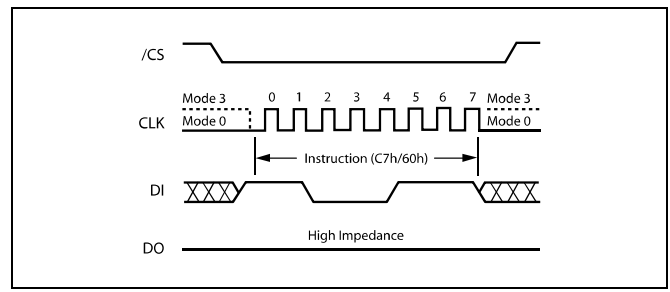

11.2.20片擦除(C7h/C6h)

片擦除指令在指定的区块内(64KB)设置所有存储区为1,(FFh)。在设备接收区块擦除指令之前必须先发送写使能指令(状态寄存器位WEL=1)。该指令在/CS引脚处于低电平时开始,且跟在24位区块地址(A23-A0)之后移位发送指令代码“C6h或C7h”。片擦除指令序列如图所示。

/CS引脚在最后一个字节的第八位必须锁定为1。如果不是这样,片擦除指令将不会执行。在/CS引脚拉高后,自定时扇区擦除指令开始在一个时长为Tbe的延时(见交流特性)。正在进行扇区擦除时,读状态寄存器指令可以被接受到用来检查BUSY位。BUSY在片擦除期间等于1,且在周期接束后且在等待下一个指令到来的时候拉低。在片擦除周期结束状态寄存器的写使能锁定位(WEL)位被清零。扇区擦除在区块保护(SEC,TB,BP2,BP1,BP0)位保护时不会被执行。

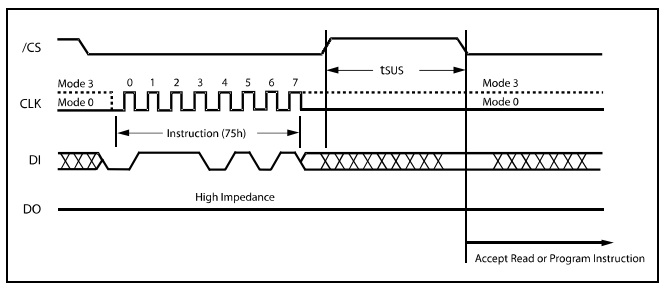

11.2.21擦除暂停(75h)

擦除暂停指令“75h”,允许系统中断一个扇区擦除或区块擦除工作且之后从从其他扇区或区块读数据或写数据。擦写暂停指令时序如图所示。

在擦除暂停期间不允许写状态寄存器指令(01h)和擦除指令(20h,52h,D8h,C7h,C6h)。擦除暂停在扇区或区块擦除期间是有效的。如果在片擦除或编程工作,擦除暂停指令被忽略。

擦除暂停指令‘75h’只有在扇区擦除或区块擦除时的状态寄存器的SUS位等于0和BUSY位等于1,才会被设备接收。如果SUS位等于1或BUSY位等于0,暂停指令就会被设备忽略。一个最大为Tsus的时间被用来暂停擦除工作。在擦除暂停之后状态寄存器的SUS位立即从0置为1且在“Tsus”时间内状态寄存器的BUSY位被立即从0置为1。对于一个之前的释放擦除指令,必须要求擦除暂停指令“75h”不早于最小时间“Tsus”于之后的恢复擦除指令“7Ah”。

在擦除暂停状态时,意外地掉电会使得设备复位且退出暂停状态。状态寄存器的SUS位也被复位为0。扇区或区块里的被暂停的数据可能 已经被破坏掉了。推荐使用者实现系统技术来对砍意外地电源中断和在擦除暂停期间保存数据完整性。

擦除暂停指令时序

11.2.22擦除释放(7Ah)

擦除释放指令“7Ah”在擦除暂停之后发送给设备来释放扇区或区块操作。擦除释放指令“7Ah”只有当状态寄存器中的SUS位等于1且BUSY位等于0时会被设备接收。执行完之后SUS位会被立即清零,BUSY位会在200ns内从零拉高为1且扇区或区块完成擦除操作。如果SUS位等于0或BUSY位等于1,该指令“7Ah”会被设备忽视。擦除释放指令时序如图所示。

擦除释放指令时序

11.2.23掉电(B9h)

尽管在正常工作期间的待机电流已经相当的低,但是通过掉电指令待机电流可以进一步降低。在电池供电应用中,掉电指令可以由更低的功耗(见交流特性ICC1和ICC2)。该指令在/CS引脚拉低时开始且通过DI引脚移位发送指令代码“B9h”如图所示。

/CS引脚必须在第八位发送结束后锁定为高电平。如果没有这样做,掉电指令将不会被执行。在/CS引脚拉高之后,在Tdp(见交流特性)时间之内设备会进入掉电模式。在掉电模式下,只有掉电释放或设备ID指令可以被接受到,才可以使设备恢复到正常模式,所有其他指令都会被忽略。这包括读状态寄存器指令,在正常工作期间是有效的。忽略所有但除了一个指令使得掉电状态也是一个最大限度的写保护条件。此设备在上电后处于正常工作模式,且有待机电流ICC1.

深度掉电指令时序图

11.2.24高性能模式(A3h)

当工作在高频率(见交流电气特性的FR和FR1)高性能模式(HPM)指令执行之前必须先执行四路I/O指令或双路I/O指令。这个指令允许内部电荷泵的预充电,所以所需的电压对于FLASH存储器阵列来说是现成的。该指令序列包括三个虚拟字节时钟后的指令A3h如图所示。在HPM指令执行后,设备会保持比正常SPI模式要高一些的静态电流(ICC3)。从掉电模式恢复或者HPM指令(ABh)可以永凯回到正常SPI模式(静态电流ICC1)。另外,写使能(06h)和掉电指令(B9h)同样也可以从HPM模式恢复到SPI待机状态。

高性能模式指令时序

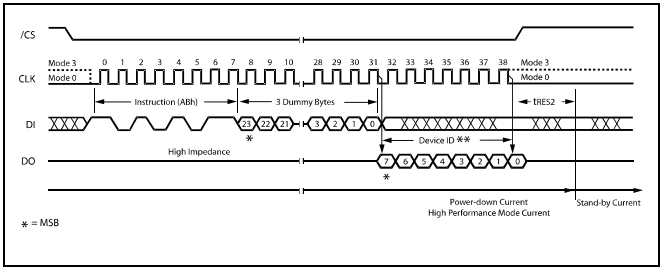

11.2.25从掉电模式或高性能模式恢复/设备ID(ABh)

从掉电或高性能模式恢复/设备ID指令是一个多用途指令。可以用来从掉电模式或高性能模式下回到到正常模式,或者获得设备电气ID号。

为了从掉电或高性能模式恢复,指令在/CS引脚为低电平的时候执行,移位发送代码“ABh”且如图所示那样拉高/CS引脚。从掉电模式释放到正常模式和其他指令被接收会花费大于Tres1的时间(见交流特性)。/CS引脚在Tres1期间报纸高电平。

当在非掉电状态用来被获得设备ID时,指令在/CS引脚为低电平开始且在三个虚拟时钟之后移位发送指令代码“ABh”,设备ID位会在之后时钟的下降沿移位发送(高位在前),如图所示W25Q64BV的设备ID值列在制造商和设备ID表格里。设备ID可以被连续读。该指令在/CS拉高后结束。

当设备从掉电模式释放时且获取设备ID,该指令和之前介绍的相似,如图,除了在/CS在Tres2时间里保持/CS为高电平(见交流特性)。在整个时间之后设备会恢复到正常模式和等待另一个指令被接收。如果从掉电模式或高性能模式恢复/设备ID指令在一个擦除,编程的写周期中发送(BUSY=1),该指令不会别识别且对现有的周期不会有任何影响。

从掉电模式或高性能模式恢复指令时序

从掉电模式或高性能模式恢复/设备ID指令时序

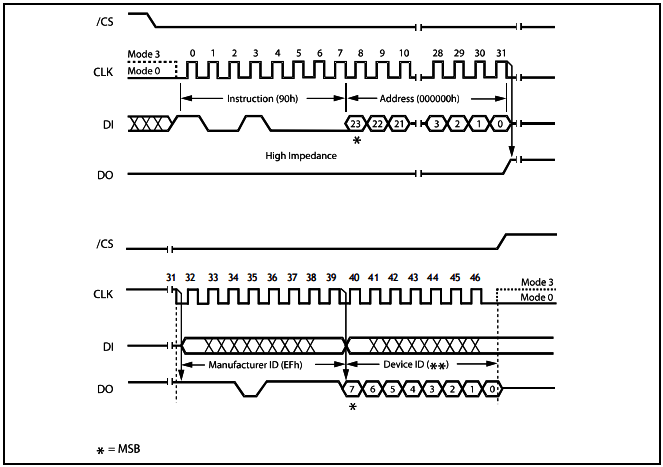

11.2.26读制造商/设备ID(90h)

读制造商/设备ID指令是从掉电模式释放的另一种选择,提供JEDEC分配的制造商ID和设备ID。

读制造商/设备ID指令和从掉电模式/设备ID指令相似。该指令在/CS拉低时开始且移位发送指令代码“90h”跟随在24位地址(A23-A0)(0000h)后面。在那以后,Winbond的制造商ID(EFh )和设备ID在时钟的下降沿移位发送出去(如图所示)(高位在前)。设备ID值列在制造商和设备ID表格里。如果24位地址开始设置为0001h,设备ID会被先读到之后是制造商UD。制造商和设备IDI可以被连续读,可以选一个或多个,该指令在/CS拉高后完成。

读制造商/设备ID

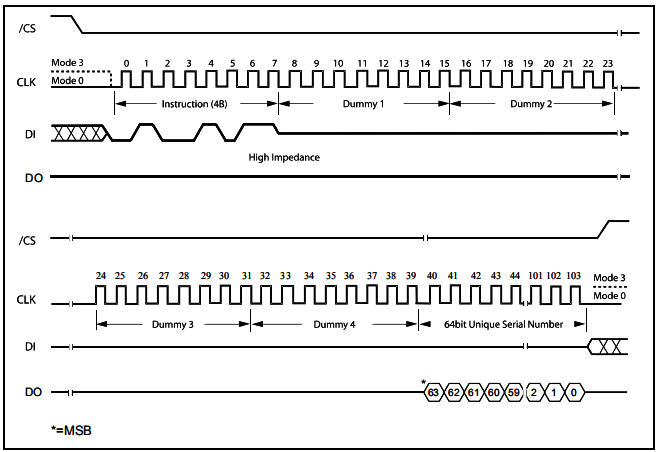

11.2.27读唯一I值(4Bh)

读唯一ID指令由厂商设置为64位只读值,且每一设备各不相同。ID值可以组合软件使用来避免复制或克隆一个系统。读唯一ID指令从/CS引脚为低电平开始且通过跟在四个空时钟字节后移位发送指令代码“4Bh”,之后,64位ID在时钟的下降沿移位出设备。

读唯一ID值指令时序

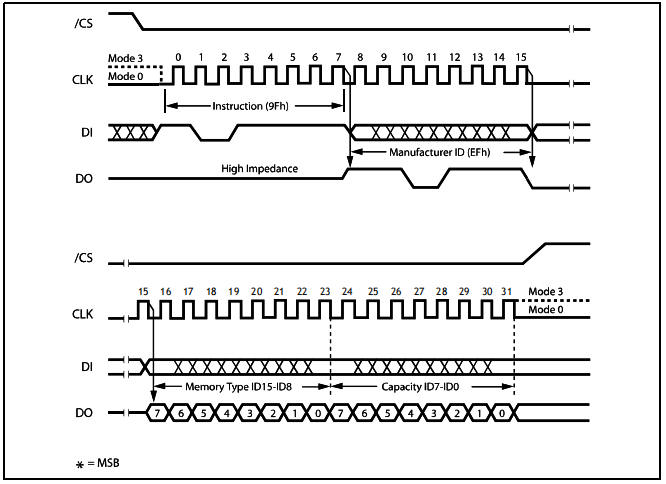

11.2.28读JEDEC ID (9Fh)

因为兼容性问题,W25Q64BV提供这些指令来进行电子设备这些设备。读JEDEC ID指令

与JEDEC标准兼容的SPI兼容串行存储器在2003年被采用。指令开始于/CS位低电平且移位发送指令代码“9Fh”,JEDEC分配了制造商字节和两个设备字节,存储器种类(ID15-ID8)和容量(ID7-ID0),在时钟CLK的下降沿移位输出(高位在前),如图对于存储器种类,容量大小值参考制造商和设备ID表格。

读JEDEC ID指令时序

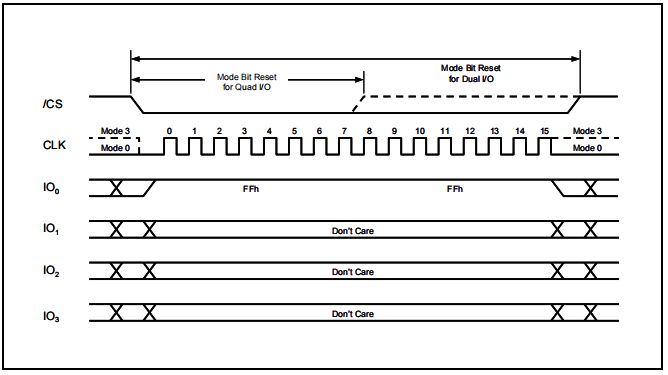

11.2.29连续读模式复位(FFh或FFFFh)

对于高速两路/四路I/O模式,“连续读模式”位(M7-M0)被执行用来进一步减少指令开销。通过设置(M7-M0)为Axh,下一个高速读两路或四路I/O操作不需要BBh/EBh的指令代码。

如果系统控制器在运行中被重置,可能会回到标准SPI模式,比如读ID(9Fh)或者高速读(0Bh),从W25Q64BV。然而,和大多数SPI串行存储器一样,W25Q64BV没有硬件复位引脚,所以如果连续读模式位被设置为“Axh”,W25Q64BV将不会识别任何指令。为了解决这种可能性, 推荐在系统复位之后的第一个指令执行连续读模式复位指令。这样做就可以从连续读模式恢复且可以设备标准SPI指令。如图。

在四路I/O工作期间,为了从“连续读模式中”恢复,只需要8个时钟,指令时“FFh”。为了在上路I/O时,从连续读模式中复位,需要移位写16个时钟指令“FFFFh”。

12.电气特性

12.1最大值范围(1)

| 参数 | 符号 | 条件 | 范围 | 单位 |

| 供电电压 | VCC | -0.6 - +4.0 | V | |

| 任何引脚能接受的电压 | VIO | 相对于VCC | -0.6 - VCC+0.4 | V |

| 任意引脚的瞬时电压 | VIOT | <20ns相对于地 | -2.0 - VCC+2.0 | V |

| 存储温度 | Tstg | -65 - 150 |

℃ | |

| 焊接温度 | Tlead | 注释2 | ℃ | |

| 静电电压 | Vesd | 人体模型 | -2000 - +2000 | V |

注释:

1.设备在指点工作环境下设计和测试。适当地工作环境外,这些等级是不能得到保证的。暴露在这些最大值附近会影响设备的稳定性。超过这些值会造成设备损坏。

2.与JEDEC标准J-STD-20C兼容,适用于小型封装的Sn-Pb或Pb-free(绿色)总成

欧洲有害物质限制指令2002/95/EU。

3.JEDEC Std JESD22-A114A(C1=100pF,R1=1500Ω,R2=500Ω)。

12.2工作范围

| 参数 | 符号 | 条件 | SPEC | 单位 | |

| 最小值 | 最大值 | ||||

| 供电电压 | VCC | Fr=80MHz,fR=33MHz Fr=50MHz |

2.7 3.0 |

3.6 3.6 |

V |

| 环境温度,工作是 | Ta | 商业级 工业级 |

0 -40 |

+70 +85 |

℃ |

注:

1.VCC电压在读期间可以超过最大值和最下肢但是必要超过编程电压的±10%(擦除/写)。

12.3上电时序和写抑制阈值

| 参数 | 符号 | SPEC | 单位 | |

| 最小值 | 最大值 | |||

| VCC(最小 )到/CS低电平 | Tvsl | 10 | us | |

| 写指令后的时间延时 | Tpuw | 1 | 10 | ms |

| 写抑制阈值电压 | Vwl | 1 | 2 | V |

12.4直流电气特性

| 参数 | 符号 | 条件 | SPEC | 单位 | ||

| 最小值 | 典型值 | 最大值 | ||||

| 输入电容 | Cin | Vin=0V | 6 | pF | ||

| 输出电容 | Cout | Vout=0V | 8 | pF | ||

| 输入漏电流 | ILI |

±2

|

uA | |||

| I/O漏电流 | ILO |

±2

|

uA | |||

| 标准电流 | ICC1 | /CS=VCC, Vin=GND或VCC |

25 | 50 | uA | |

| 掉电电流 | ICC2 | /CS=VCC, Vin=GND或VCC |

1 | 5 | uA | |

| 高性能电流 | ICC3 | 在使能高性能模式之后 | 50 | 100 | uA | |

| 读数据/双路/四路1MHz | ICC4 | C=0.1VCC/0.9VCC DO=开路 |

4/5/6 | 6/7.5/9 | mA | |

| 读数据/双路/四路33MHz | ICC4 | C=0.1VCC/0.9VCC DO=开路 |

6/7/8 | 9/10.5/12 | mA |

|

| 读数据/双路/四路50MHz | ICC4 | C=0.1VCC/0.9VCC DO=开路 |

7/8/9 | 10/12/13.5 | mA |

|

| 读数据/双路/四路80MHz | ICC4 | C=0.1VCC/0.9VCC DO=开路 |

10/11/12 | 15/16.5/18 | mA |

|

| 写状态寄存器电流 | ICC6 | /CS=VCC | 8 | 12 | mA | |

| 页编程电流 | ICC7 | /CS=VCC | 20 | 25 | mA | |

| 扇区/区块擦除电流 | /CS=VCC | 20 | 25 | mA | ||

| 片擦除电流 | /CS=VCC | 20 | 25 | mA | ||

| 输入低电平 | Vil | VCCx0.3 | V | |||

| 输入高电平 | Vih | VCCx0.7 | V | |||

| 输出低电平 | Vol | Iol=1.6mA | 0.4 | V | ||

| 输出高电平 | Voh | Ioh=-100uA | VCC-0.2 | V | ||

注:

1.测试采样基于VCC=3V,Ta=25℃

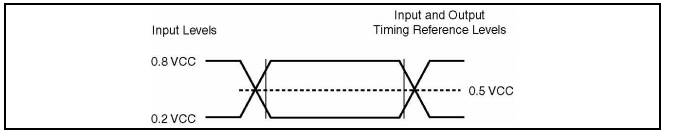

12.5交流测量条件

| 参数 | 符号 | SPEC | 单位 | |

| 最小值 | 最大值 | |||

| 负载电容 | Cl | 30 | pF | |

| 输入上升和下降时间 | Tr,Tf |

5 | ns | |

| 输入脉冲电压 | Vin | 0.2VCC-0.8VCC | V | |

| 输入时序参考电压 | IN | 0.3VCC-0.7VCC | V | |

| 输出时序参考电压 | OUT | 0.5VCC-0.5VCC |

V | |

注:输出高阻态被定义为数据不再输出的点

交流测量I/O波形

12.6交流电气特性

| 介绍 | 符号 | ALT | SPEC | 单位 | ||

| 最小值 | 典型值 | 最大值 | ||||

| 所有指令的时钟频率, 除了读数据(03h)和八进制字节读(E3h) 2.7V-3.6V,工业温度级 |

Fr | Fc | D.C. | 80 | MHz | |

| 八进制字节读四路I/O时钟频率 3.0V-3.6V,工业温度级 |

Fr | Fc | D.C. |

50 | MHz |

|

| 读数据指令时钟频率(03h) | Fr | D.C. | 33 | MHz | ||

| 时钟高电平时间,低电平时间 除读数据(03h) |

Tclh, Tcll |

6 | ns | |||

| 读数据(03h)的时钟高电平时间,低电平时间 | Tclh, Tcll |

8 8 |

ns | |||

| 峰到峰上升时间 | Tclch | 0.1 | V/ns | |||

| 峰到峰下降时间 | Tchcl | 0.1 | V/ns | |||

| 相对于时钟CLK的/CS激活设置时间 | Tslch | Tcss | 5 | ns | ||

| 相对于时钟CLK非激活保持时间 | Tchsl | 5 | ns | |||

| 数据建立时间 | Tdvch | Tdsu |

2 | ns |

||

| 数据保持时间 | Tchdx | Tdh | 5 | ns | ||

| 依赖于时钟CLK的/CS激活保持时间 | Tchsh | 5 | ns | |||

| 依赖于时钟CLK的/CS非激活保持时间 | Tshch | 5 | ns | |||

| /CS取消选择时间(从阵列读到阵列读/擦除或编程到读状态寄存器) | Tshsl | Tcsh | 10/50 | ns | ||

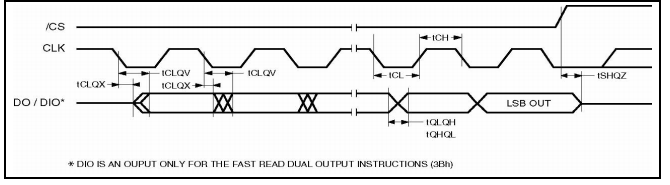

| 输出禁止时间 | Tshqz | Tdis | 7 | ns | ||

| 时钟低电平到输出可用 2.7V-3.6V/3.0V-3.6V |

Tclqv1 | Tv1 | 7/6 | ns | ||

| 时钟低电平到输出可用(读ID指令) 2.7V-3.6V/3.0V-3.6V |

Tclqv2 | Tv2 | 8.5/7.5 | ns | ||

| 输出保持时间 | Tclqx | Tho | 0 | ns | ||

| 依赖于时钟CLK的/HOLD激活建立时间 | Thlch | 5 | ns | |||

12.7交流电气特性

| 介绍 | 符号 | ALT | SPEC | 单位 | ||

| 最小值 | 典型值 | 最大值 | ||||

| 依赖于时钟CLK的/HOLD激活保持时间 | Tchhh | 5 | ns | |||

| 依赖于时钟CLK的/HOLD非激活建立时间 | Thhch | 5 | ns | |||

| 依赖于时钟CLK的/HOLD非激活保持时间 | Tchhl | 5 | ns | |||

| /HOLD到数据低阻态 | Thhqx | Tlz | 7 | ns | ||

| /HOLD到数据高阻态 | Thlqz | Thz | 12 | ns | ||

| /CS低电平之前的写保护建立时间 | Twhsl | 20 | ns | |||

| /CS高电平忠厚的写保护保持时间 | Tshwl | 100 | ns | |||

| /CS高点平到掉电模式 | Tdp | 3 | us | |||

| /CS高电平到待机模式(不读电子ID) | Tres1 |

3 | us | |||

| /CS高电平到待机模式(读电子ID) | Tres2 | 1.8 | us | |||

| 暂停后/CS高电平到下一个指令 | Tsus | 20 | us | |||

| 写状态寄存器指令时间 | Tw | 10 | 15 | ms |

||

| 字节编程时间(第一个字节) | Tbp1 |

20 | 50 | us | ||

| 另外的字节编程时间(第一个字节后) | Tbp2 | 2.5 | 12 | us | ||

| 页编程时间 | Tpp |

0.7 | 3 | ms | ||

| 扇区擦除时间(4KB) | Tse | 30 | 200/400 | ms | ||

| 区块擦除时间(32KB) | Tbe1 | 120 | 800 | ms | ||

| 区块擦除时间 | Tbe2 | 150 | 1000 | ms | ||

| 片擦除 | Tce | 15 | 30 | s | ||

注:

1.时钟高电平+低电平必须小于或等于1/Fc。

2.由设计和/或特性保证的价值,不是100%在生产中测试。

3.仅当扇区保护位设置为1时,才作为写状态寄存器指令的约束。

4.对一页之内的(第一个字节后的)多字节,Tbpn=Tbp1+Tbp2xN(典型值)和Tbpn=Tbp1+Tbp2xN(最大值),当N=编程字节数量。

5.最大值Tse=200ms在小于50k周期,大于50k小于100k时Tse=400ms。

12.8串行输出时序

12.9输入时序

12.10保持时间

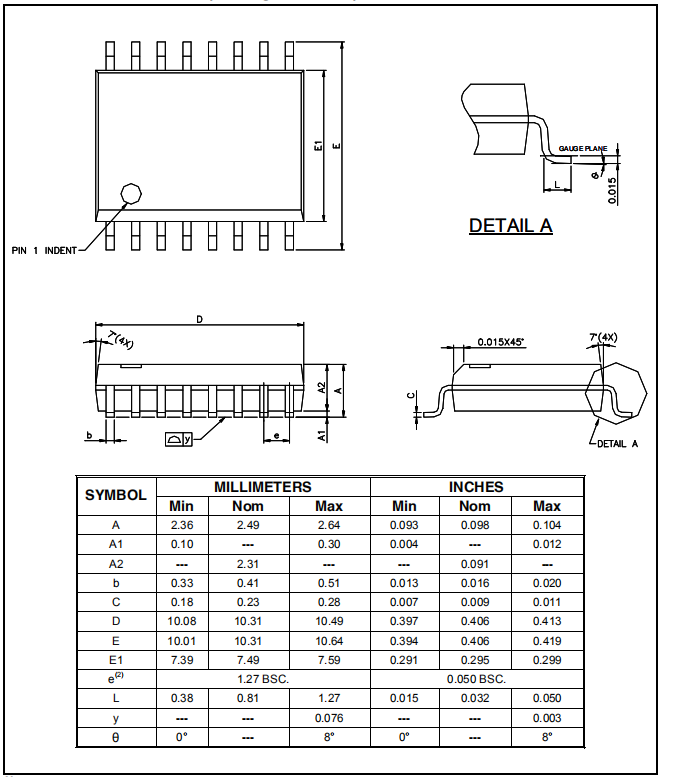

13.封装信息

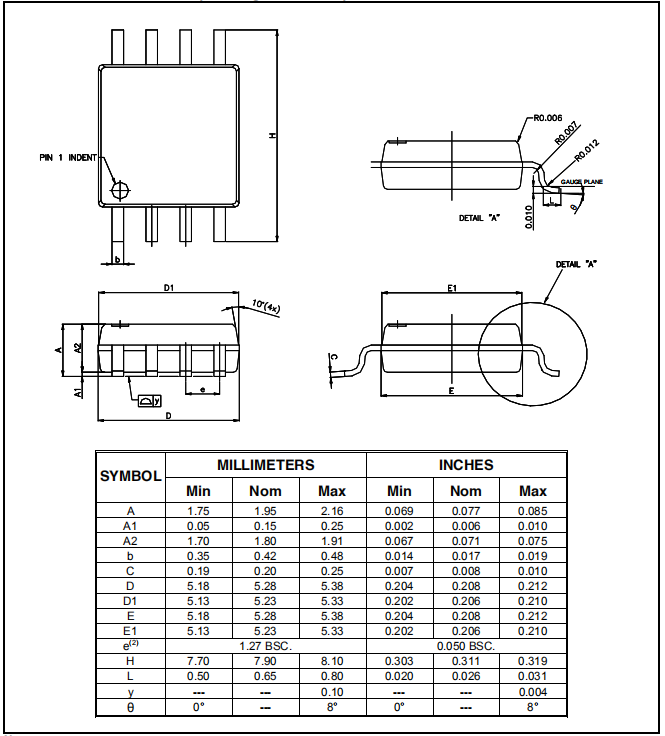

13.1 8-pin SOIC 208mil(封装代码 SS)

注:

1.控制单位:millimeter,除非另有说明。

2.BSC=到中心得基础焊接空间

3.尺寸D1和E1不包括FLASH突出物,应从封装的底部开始测量。

4.成形的引线与阀座平面的共面应在0.004英寸内。

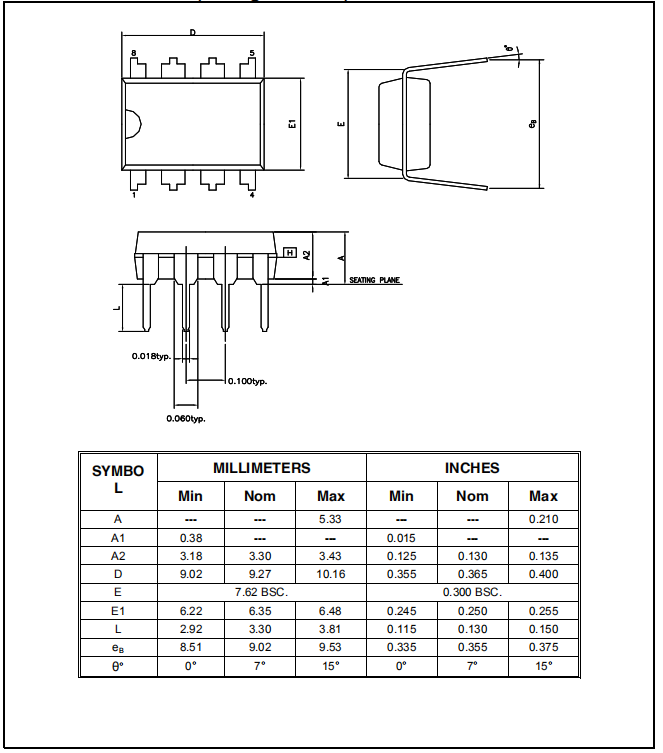

13.2 8-pin PDIP 300mil(封装代码 DA)

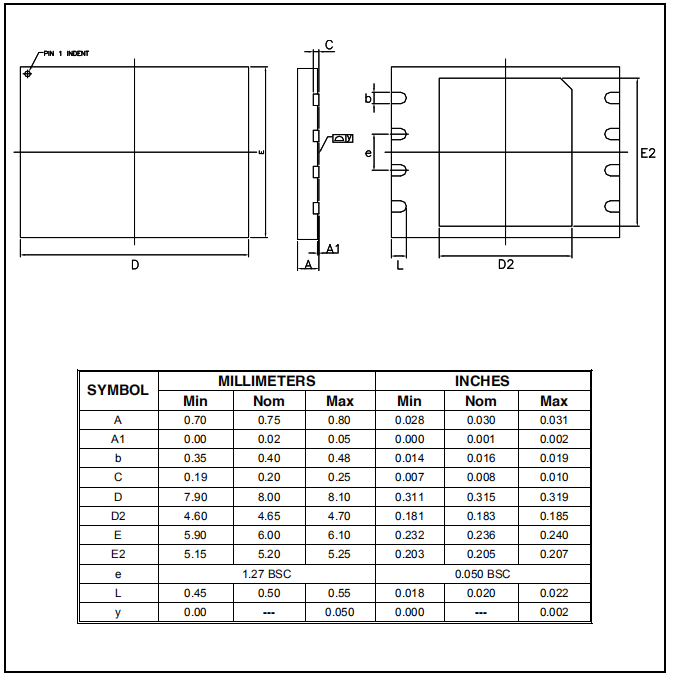

13.3 8-Contact 8x6mm WSON(封装代码 ZE)

13.4 16-pin SOIC 300mil(封装代码 SF)

注:

1.控制单位:英尺,除非另有说明

2.BSC=到中心的基础焊接区域

3.尺寸D和E1不包括FLASH突出物,应从底部测量封装。

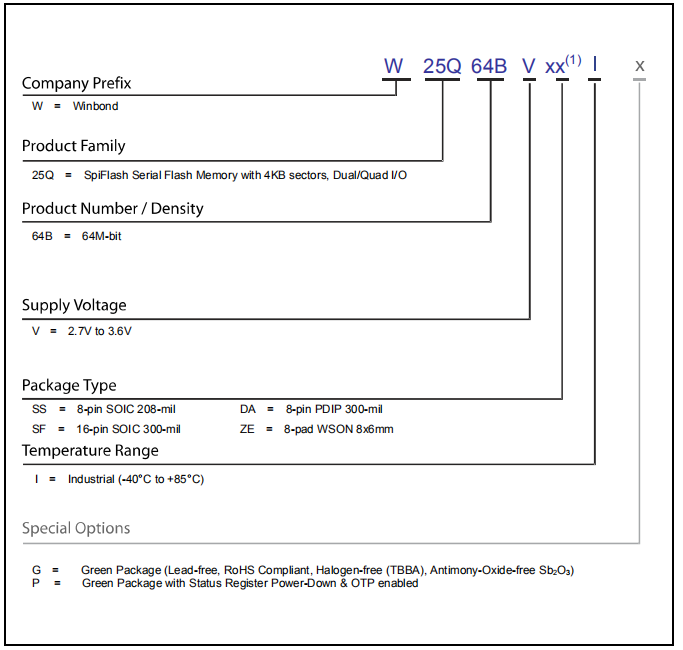

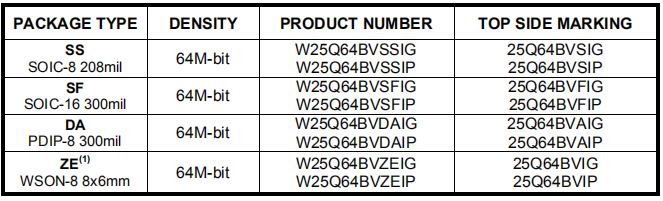

14.订购信息

注:

1. 只有第二位用作封装标记,WSON封装ZE不标注封装上。

2.标准散装货物为管材(形状E)。下订单时请指定替代包装方法,如胶带和卷轴(形状T),。

3.零件标记上不包括“W”前缀。

14.1有效部分编号和顶面标记

下表提供了W25Q64BV SpiFlash内存的有效部件号。请联系Winbond根据密度和包类型提供特定的可用性。Winbond SpiFlash内存使用12-为订购产品编号。但是,由于空间有限,所有包裹的顶部都有标记使用简短的10位数。

注:

1.WSON封装类型ZE不使用顶部标记 。

15.修订历史

| 版本 | 时间 | 页数 | 介绍 |

| A | 08/24/08 | 最新创建的初代 | |

| B | 01/15/09 03/12/09 3/13/09 |

56&57 57 5 13 |

添加到部件号末尾的P字符 更正顶面标志 将有效电流改为4mA 将QE引脚更改为QE位 |

| C | 08/20/09 | 38,39,54~56 58 44 |

更新擦除暂停和恢复介绍 更新封装表格 UID波形矫正 |

| D | 09/24/09 | 52 5,7,55,58,59 44 46 |

更改fR=33MHz 添加PDIP封装 |

| E | 07/08/10 | 61 55-58 50,53 |

移除初步的设计者 更新封装图表 更行参数VIH/VIL,Tbp1,Tse |