寄存器

寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部分。寄存器是有限存储容量的高速存储部件,它们可用来暂存指令、数据和位址。

SRAM

静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种。所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。相对之下,动态随机存取存储器(DRAM)里面所储存的数据就需要周期性地更新。然而,当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后还能储存资料的ROM或闪存是不同的。

存储单元由RS锁存器构成

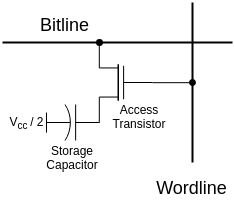

DRAM

动态随机存取存储器(Dynamic Random Access Memory,DRAM)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。由于在现实中晶体管会有漏电电流的现象,导致电容上所存储的电荷数量并不足以正确的判别数据,而导致数据毁损。因此对于DRAM来说,周期性地充电是一个无可避免的要件。由于这种需要定时刷新的特性,因此被称为“动态”存储器。相对来说,静态存储器(SRAM)只要存入数据后,纵使不刷新也不会丢失记忆。

总线收发器/缓冲器

缓冲寄存器:又称缓冲器缓冲器(buffer):多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。当负载不具有非选通输出为高阻特性时,将起到隔离作用;当总线的驱动能力不够驱动负载时,将起到驱动作用。由于缓冲器接在数据总线上,故必须具有三态输出功能。

它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。

Buffer:缓冲区,一个用于在初速度不同步的设备或者优先级不同的设备之间传输数据的区域。通过缓冲区,可以使进程之间的相互等待变少,从而使从速度慢的设备读入数据时,速度快的设备的操作进程不发生间断。

缓冲器主要是计算机领域的称呼。具体实现上,缓冲器有用锁存器结构的电路来实现,也有用不带锁存结构的电路来实现。一般来说,当收发数据双方的工作速度匹配时,这里的缓冲器可以用不带锁存结构的电路来实现;而当收发数据双方的工作速度不匹配时,就要用带锁存结构的电路来实现了(否则会出现数据丢失)。

缓冲器在数字系统中用途很多:

(1)如果器件带负载能力有限,可加一级带驱动器的缓冲器;

(2)前后级间逻辑电平不同,可用电平转换器加以匹配;

(3)逻辑极性不同或需要将单性变量转换为互补变量时,加带反相缓冲器;(4)需要将缓变信号变为边沿陡峭信号时,加带施密特电路的缓冲器

(5)数据传输和处理中不同装置间温度和时间不同时,加一级缓冲器进行弥补等等。

区别

1,寄存器由D触发器构成,D触发器由12晶体管构成,SRAM由6个晶体管构成,DRAM由1个晶体管和一个电容构成。

2,锁存器的集成度更高,所以在的ASIC设计中会用到锁存器。但锁存器对毛刺敏感,无异步复位端,不能让芯片在上电时处在确定的状态;另外,锁存器会使静态时序分析变得很复杂,不利于设计的可重用。所以,在ASIC设计中,除了CPU这高速电路,或者RAM这种对面积很敏感的电路,一般不提倡用锁存器。

3,从寄存数据的角度来讲,寄存器和锁存器的功能是相同的;它们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制