特权同学玩转Zynq连载20——基于FPGA的模块化设计

1 模块化设计概述

模块化设计是FPGA设计中一个很重要的技巧,它能够使一个大型设计的分工协作、仿真测试更加容易,代码维护或升级更加便利。

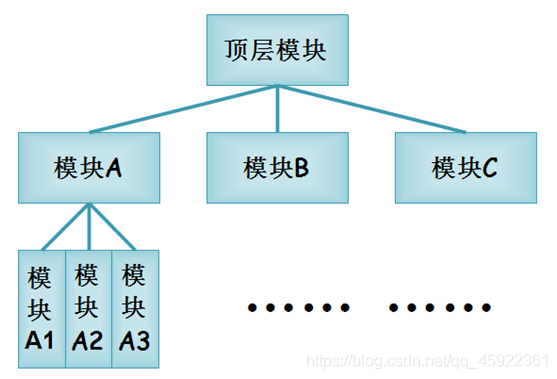

如图所示,一般整个设计工程的顶层文件里只做例化,不做逻辑处理。然后一个顶层下面会有模块A、模块B、模块C等等,模块A/B/C下又可以分多个子模块实现。

如此一来,就可以将大规模复杂系统按照一定规则划分成若干模块,然后对每个模块进行设计输入、综合与实现,并将实现结果约束在预先设置好的区域内,最后将所有模块的实现结果进行整合集成,就能完成整个系统的设计。

模块化设计的实现步骤是整个模块化设计流程中最重要、最特殊的,它包含:

●初始预算,本阶段是实现步骤的第一步,对整个模块化设计起着指导性的作用。在初始预算阶段,项目管理者需要为设计的整体进行位置布局,只有布局合理,才能够在最大程度上体现模块化设计的优势;反之,如果因布局不合理而在较后的阶段需要再次进行初始预算,则需要对整个实现步骤全面返工。

●子模块的设计实现,在该阶段,每个项目成员并行完成各自子模块的实现。

●模块的最终集成,在该阶段项目管理者将顶层的实现结果和所有子模块的实现结果进行整合集成,完成整个设计的实现。

模块划分的基本原则是,子模块功能相对独立,模块内部联系尽量紧密,而模块间的连接尽量简单。对于那些难以满足模块划分准则的具有强内部关联的复杂设计,并不适合采用模块化设计方法。

2 模块化设计实例详解

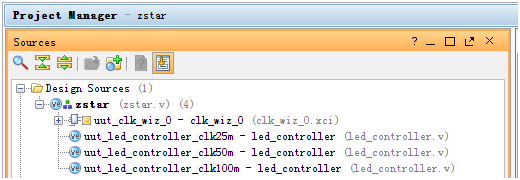

下面以zstar_ex03工程的顶层源码zstar.v为例,讲解在Verilog代码中如何实现模块化设计。在zstar.v模块下面有4个模块,包括1个PLL时钟产生模块,以及3个控制LED闪烁的模块。

module zstar(

input ext_clk_25m, //外部输入25MHz时钟信号

output[2:0] led //LED指示灯接口

);

//-------------------------------------

wire clk_25m; //PLL输出25MHz时钟

wire clk_50m; //PLL输出50MHz时钟

wire clk_100m; //PLL输出100MHz时钟

wire sys_rst_n; //PLL输出的locked信号,作为FPGA内部的复位信号,低电平复位,高电平正常工作

clk_wiz_0 uut_clk_wiz_0

(

// Clock in ports

.clk_in1(ext_clk_25m), // input clk_in1

// Clock out ports

.clk_out1(clk_25m), // output clk_out1

.clk_out2(clk_50m), // output clk_out2

.clk_out3(clk_100m), // output clk_out3

// Status and control signals

.reset(1’b0), // input reset

.locked(sys_rst_n)); // output locked

//-------------------------------------

//25MHz时钟进行分频闪烁,计数器为24位

led_controller #(24) uut_led_controller_clk25m(

.clk(clk_25m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[2]) //LED指示灯接口

);

//-------------------------------------

//25MHz时钟进行分频闪烁,计数器为25位

led_controller #(25) uut_led_controller_clk50m(

.clk(clk_50m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[1]) //LED指示灯接口

);

//-------------------------------------

//25MHz时钟进行分频闪烁,计数器为26位

led_controller #(26) uut_led_controller_clk100m(

.clk(clk_100m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[0]) //LED指示灯接口

);

endmodule

★ 语法要点

注意zstar.v模块的代码中例化了4个子模块,这是一个不折不扣的模块化设计工程。下面是对led_controller.v模块的一个例化代码。

led_controller #(24) uut_led_controller_clk25m(

.clk(clk_25m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[2]) //LED指示灯接口

);

以上面这段代码为例,模块例化大体有下面几个要点:

● led_controller是原始工程源码本身的模块名称。

● uut_led_controller_clk25m的名称是可以随意起的,只要不和已有的名称重名即可,它表示我们对当前例化工程led_controller.v的唯一识别名。在这个工程中,我们看到led_controller.v模块被例化了多次,但它和uut_led_controller_clk25m对应位置的命名是不一样的,而且必须是不一样的,表示工程中有多个完全一样的功能模块。这和软件程序里面的调用不一样,软件程序由于运行起来总是串行的,所以多次调用同一个函数时,这个函数可以只占一个函数所需的物理存储空间即可;但是FPGA是并行处理的,它的模块例化,哪怕是完全一样的模块,往往也是需要多个完全一样的物理资源与余对应的。

● “.clk(clk_25m),”是接口的映射,“.(),”是固定格式。clk是led_controller.v模块内部的接口,clk_25m是zstar.v模块的接口。

如图所示,当工程编译后,我们便可以在工程管理窗口中看到整个工程的模块结构。在zstar.v模块下面对应了4个子模块。

led_controller.v模块代码如下。

module led_controller(

input clk, //时钟信号

input rst_n, //复位信号,低电平有效

output sled //LED指示灯接口

);

parameter CNT_HIGH = 24; //计数器最高位

//-------------------------------------

reg[(CNT_HIGH-1):0] cnt; //24位计数器

//cnt计数器进行循环计数

always @ (posedgeclk or negedgerst_n)

if(!rst_n) cnt<= 0;

else cnt<= cnt+1’b1;

assign sled = cnt[CNT_HIGH-1];

endmodule