特权同学玩转Zynq连载40——[ex59] 基于Zynq的双目视觉图像采集显示实例

1 CMOS摄像头应用背景与驱动原理

CMOS摄像头(CMOS Sensor)是一种采用CMOS图像传感器的摄像头。摄像头主要有两类,CMOS和CCD。CMOS一般应用在普通数码设备中,CCD一般应用在高档数码设备中,它们都是光学成像,但CCD比CMOS单位成像的效果要好。CCD镜头比CMOS的颜色还原更好,并且分辨率更高。

CCD和CMOS在制造上的主要区别是,CCD是集成在半导体单晶材料上,而CMOS是集成在被称做金属氧化物的半导体材料上,但工作原理没有本质的区别。在成像方面,CCD的成像通透性、明锐度都很不错,色彩还原、曝光可以保证基本准确。而CMOS的产品往往通透性一般,对实物的色彩还原能力偏弱,曝光也都不太好。由于CMOS自身的物理特性,其成像质量和CCD还是有一定距离的。CCD制造工艺较复杂,掌握CCD技术的厂商并不多,采用CCD摄像头的价格相对也比较昂贵。但随着制造工艺的不断改进,目前CMOS和CCD的实际成像效果的差异在逐渐减小。加之CMOS的制造成本和功耗都要比CCD低不少,因此很多摄像头生产厂商更趋向于采用CMOS感光元件。正是由于低廉的价格以及高度的整合性,使得CMOS摄像头得到了更广泛的应用。

CCD是目前比较成熟的成像器件,CMOS被看作未来的成像器件。因为CMOS结构相对简单,与现有的大规模集成电路生产工艺相同,从而生产成本可以大大降低。从原理上看,CMOS的信号是以点为单位的电荷信号,而CCD是以行为单位的电流信号,前者更为敏感,速度也更快,更为省电。现在高级的CMOS并不比一般CCD差,但是CMOS工艺还不是十分成熟,普通的CMOS一般分辨率低而成像较差。

不管CCD还是CMOS,基本上两者都是利用矽感光二极体(photodiode)进行光与电的转换。比较CCD和CMOS的结构,ADC的位置和数量是最大的不同。简单的说,CCD每曝光一次,在快门关闭后进行像素转移处理,将每一行中每一个像素(pixel)的电荷信号依序传入“缓冲器”中,由底端的线路引导输出至CCD旁的放大器进行放大,再串联ADC输出;相应的,CMOS的设计中每个像素旁就直接连着ADC(放大兼类比数字信号转换器),信号直接放大并转换成数字信号。

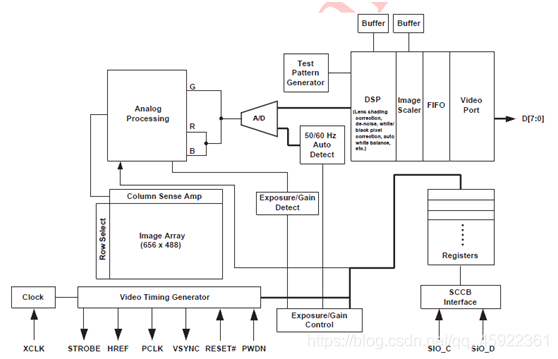

我们这个模块中所使用的CMOS Sensor的型号为OV5640,其内部功能框图如图1所示。前端有模拟感光模块,经过AD处理后将模拟信号转换为数字信号,后端经过一些处理后输出符合一定协议标准的视频数据流。FPGA器件将根据这个数据流的协议对视频数据进行采集解码,最终显示在720p (1280720)分辨率的VGA液晶显示器上。

2 视频采集系统设计概述

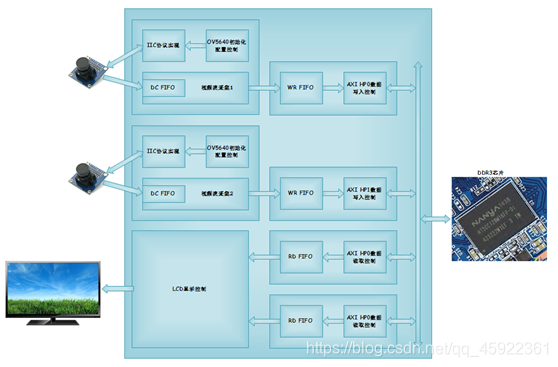

如图2所示,这是整个视频采集系统的原理框图。上电初始,FPGA需要通过IIC接口对CMOS Sensor进行寄存器初始化配置。这些初始化的基本参数,即初始化地址对应的初始化数据都存储在一个预先配置好的FPGA片内ROM中。在初始化配置完成后,CMOS Sensor就能够持续输出标准RGB的视频数据流,FPGA通过对其同步信号,如时钟、行频和场频进行检测,从而从数据总线上实时的采集图像数据。

在FPGA内部,采集到的视频数据先通过一个FIFO,将原本25MHz频率下同步的数据流转换到50MHz的频率下。接着将这个数据再送入写DDR3缓存的异步FIFO中,这个FIFO中的数据一旦达到一定数量,就会被写入DDR3中。与此同时,使用另一个异步FIFO将DDR3缓存的图像数据读出,并依此送往LCD驱动模块进行显示。LCD驱动模块不断的发出读图像数据的请求,并驱动液晶显示器显示视频图像。

本实例的双目,即2个OV5640摄像头的图像采集,实际上是两个完全一样的图像采集模块,它们采集到的数据分别通过Zynq的AXI HP总线HP1和HP2通道写入到DDR3中。然后LCD显示控制端则分别通过AXI HP总线的HP1和HP2读出两个摄像头的视频图像,最终驱动显示器左右两侧分别显示两个摄像头的图像。

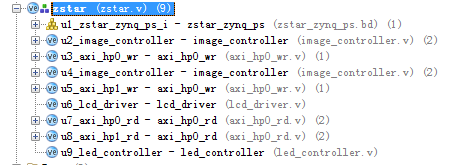

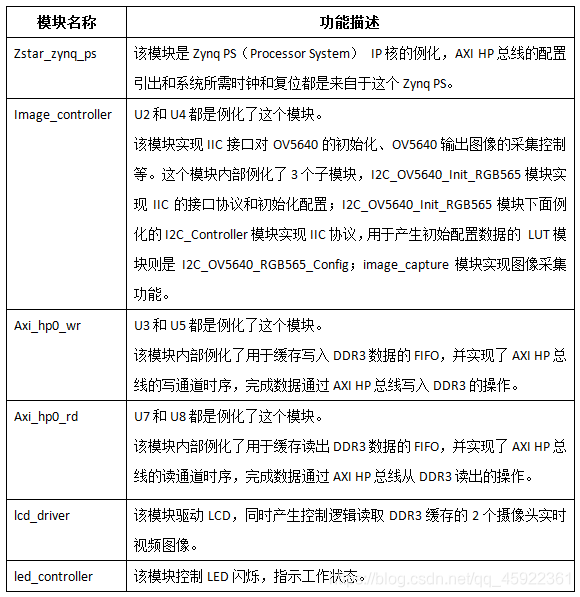

如图3所示,这里显示了整个工程的各个模块层次结构。在顶层模块at7.v下面有9个子模块。这9个子模块的功能以及他们所包含的子模块或例化功能描述如表1所示。

表1 工程模块描述

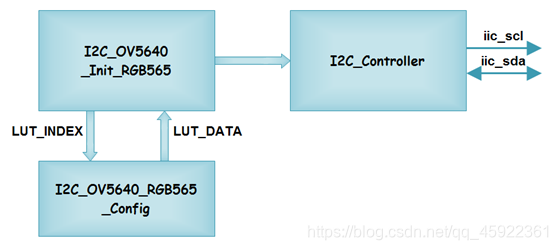

3 IIC接口配置模块设计

如图4所示,Iic_ctrl模块和iic_gene模块是用于产生IIC配置的逻辑。Iic_ctrl模块主要是最底层的IIC协议实现,而iic_gene模块则使用状态机产生一串的CMOS Sensor寄存器配置操作,该模块的配置地址和数据是存储在事先设定好的LUT模块I2C_OV5640_RGB565_Config中。

4 视频流采集设计

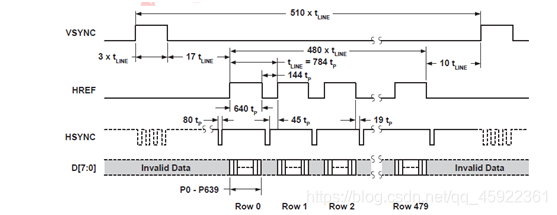

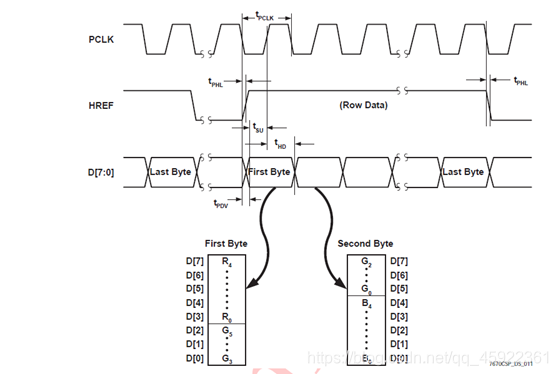

在对CMOS Sensor进行了寄存器的初始化配置后,并行数据总线上便开始持续的输出视频数据流。如图8所示,这是CMOS Sensor输出VGA(640480分辨率)并行数据视频流协议的时序波形。我们可以看到,场同步信号VSYNC的每一个高脉冲表示新的一场图像(或者说是新的一帧图像)马上要开始传输;行同步信号HREF为高电平时,表示目前的数据总线D[7:0]上的数据是有效的视频流。

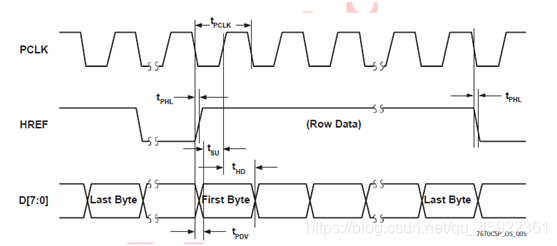

如图9所示,视频时钟PCLK的每个上升沿,有效数据D[7:0]、行同步信号HREF和场同步信号VSYNC被锁存到FPGA中。

一个有效的行将传输6402Bytes的数据,也就是说,一个像素点会有2Bytes即16bits的有效色彩值。对应R、G、B的位数分别为5bits、6bits、5bits。传输的数据总线是8bits,那么一个像素点对应就有2个8bits需要传输。每两个字节中的R、G、B格式定义如图10所示。

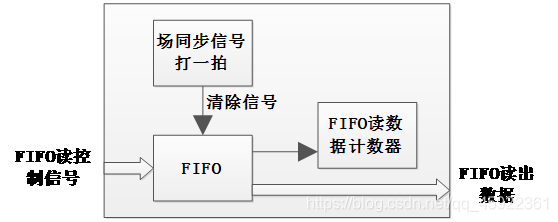

理解了时序波形,我们再来看看代码中是如何对CMOS Sensor送来的这组源同步信号进行采集的。如图11所示,这里通过一个异步FIFO来同步CMOS Sensor和FPGA内部逻辑。我们只要把vpclk、vdb、vhref分别作为FIFO的写入时钟、写入数据和写入使能信号。此外,vvsync作为这个FIFO的复位信号,每一帧新图像前FIFO进行一次清空,实际操作中,为了得到稳定有效的复位信号,我们使用内部时钟对这个复位信号打了一拍。这样,我们便把持续不断的视频流有效数据缓存到了FIFO中。在FIFO的读端,判定数据大等于1616bit时,就连续读出这16个数据,送到ddr_cache模块的DDR3写缓存FIFO中。

5 LCD控制器设计

LCD显示控制部分比较简单,用x_cnt和y_cnt两个计数器,产生一个二维图像的有效显示区域。有效显示区域的图像数据从DDR3中读取,对应的图像就是OV5640采集到的VGA图像。控制接口上,这个模块输出lcd_rfclr信号作为每个图像帧的同步信号,或者称之为复位信号,在每个有效显示图像开始前,这个信号都会拉高一段时间,axi_hp0_rd.v模块可以用这个信号实现FIFO的复位,以及对应的控制信号的复位。读数据请求信号lcd_rfreq1和lcd_rfreq2会产生连续的640*480个时钟周期的高电平,用于读取DDR3中缓存的两个摄像头的图像数据。16位数据总线lcd_rfdb1和lcd_rfdb2则分别在每个读数据请求信号lcd_rfreq1和lcd_rfreq2拉高后有效,对应数据送到显示器进行显示。lcd_rfreq1和lcd_rfreq2信号的拉高则分别在液晶屏的左边半屏和右边半屏。

6 装配说明

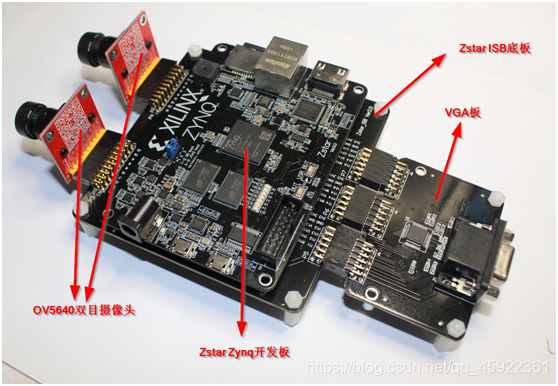

2个OV5640摄像头模块通过Zstar ISB底板与Zstar Zynq开发板连接,VGA也是通过Zstar ISB底板与Zstar Zynq开发板连接,VGA板同时需要连接到VGA显示器。连接示意如图12所示。

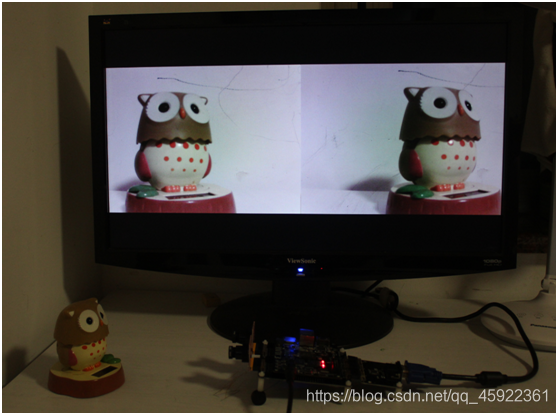

7板级调试

本实例对应ex59实例工程,已经制作好的BOOT.bin放置在工程路径“zstar_ex59\zstar.sdk\BOOT”下。也可以参考文档《玩转Zynq-实例篇:[ex51] 制作裸跑程序的启动文件BOOT.bin.pdf》制作包含.bit文件的BOOT.bin文件,将其拷贝到TF卡中,插入Zstar开发板的卡槽中,做好装配连接,上电。视频显示如图所示。