(1)发送端支持TLP poisoning功能是可选的

(2)数据中毒功能仅仅适应于写请求(posted或non-posted),message with data,原子操作请求,读完成包,原子操作完成包的数据。

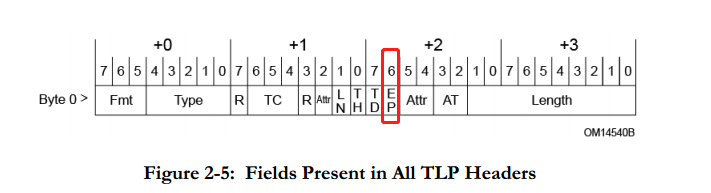

a。中毒TLP中毒是通过TLP中的EP比特来显示。

b。只有TLP是with data时,才允许发送端设置EP bit为1。如果TLP没有数据,但是EP比特为1,接收端的行为是不明确的

(3)如果发送端支持数据中毒功能,从发送端发送的带bad data的TLP需要使用上面的中毒机制。(这句话相当于屁话,没啥信息含量)

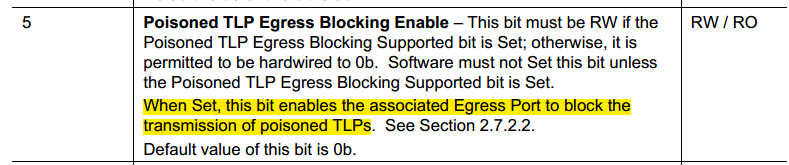

(4)如果DP口支持Poisoned TLP Egress Blocking功能,需要使能Poisoned TLP Egress Blocking enable比特,当中毒TLP从egress port发出时,该port要把这个TLP当做Poisoned TLP Egress Blocking error,除非有更高优先级的错误。

并且DP口要进行下面的操作:

a. DP口不能发送这个TLP

b. 如果Poisoned TLP Egress Blocked error被mask,并且DPC是enable的,DPC必须触发 。

c. 如果DPC没有被触发,且TLP是non-posted请求,DP口必须返回一个completion包,这个completion包和DPC触发时一样(CA或者UR状态的completion)

下面是intel的CPU手册的关于poisoned TLP的描述,forward poisoned TLP到destination可能导致MCE(之前使用intel和AMD的CPU确实遇到poisoned TLP导致的MCE)。由于poisoned TLP是从switch下面穿过来的,当时使用了switch的drop poisoned TLP功能来规避了这个问题。其实Intel的CPU也有drop poisoned TLP的功能,AMD的CPU也有类似功能

AMD CPU drop poisoned TLP的reg

PCIEPORT0F0x000001C0 (PCIE_RX_CNTL)

6 RX_IGNORE_EP_ERR. Read-write. 0=Report error normally. 1=Ignore error. Controls ignoring Poisoned TLP

Errors. When set, ignores EP bit on received TLP, treating it as if the TLP did not have it set. Poisoned TLP

Received error is not logged and TLP is passed to Slave Client with EP=0. AER header log (if a different error is

present) may report EP=0.

intel CPU drop poisoned TLP的reg

PLX switch drop poisoned TLP的reg