1.ARM对于异常(中断)的使用过程

(1)初始化:设置中断源让它产生中断;设置中断控制器(屏蔽,优先级);设置CPU总开关(使能中断)

(2)执行程序

(3)产生中断

(4)CPU每执行完一条指令,都会检查有无中断/异常产生。

(5)发现有中断/异常产生,开始处理。对于不同的异常,会跳去不同的地址执行程序。这些地址上,只是一条跳转指令,跳去执行某个函数。

(6)这些函数做:保存现场(各类寄存器);处理异常,再调用不同的函数;恢复现场

PS:中断程序怎么被调用?CPU强制跳转到某个地方,在该地方放置跳转指令跳转到其他函数,其他函数来做(6)中的事情。

2.CPU模式(mode)状态(state)与寄存器

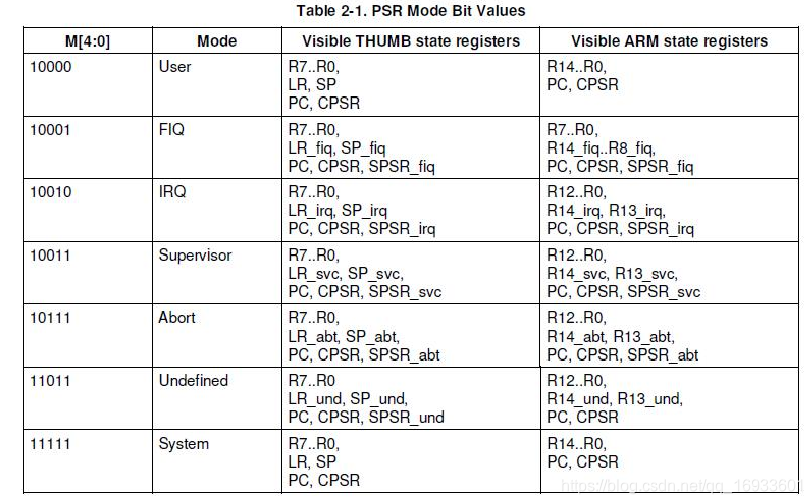

(1)ARM CPU七种模式:USR(用户模式),SYS(系统模式),异常模式。其中,异常模式又分为UND(未定义模式),SVC(管理模式),ABT(中止模式),IRQ(中断模式),FIQ(快中断模式)。除了USR模式外,其他模式之间都可以随意切换,被称为特权模式,可以直接操作CPSR寄存器进入其他模式。

(2)CPU有两种state:ARM STATE下用ARM指令集,每个指令占据4字节。THUMB STATE下用thumb指令集,每个指令2字节。同样的代码编译成ARM指令集和THUMB指令集占据的字节不同,因此,THUMB指令集更加高效。

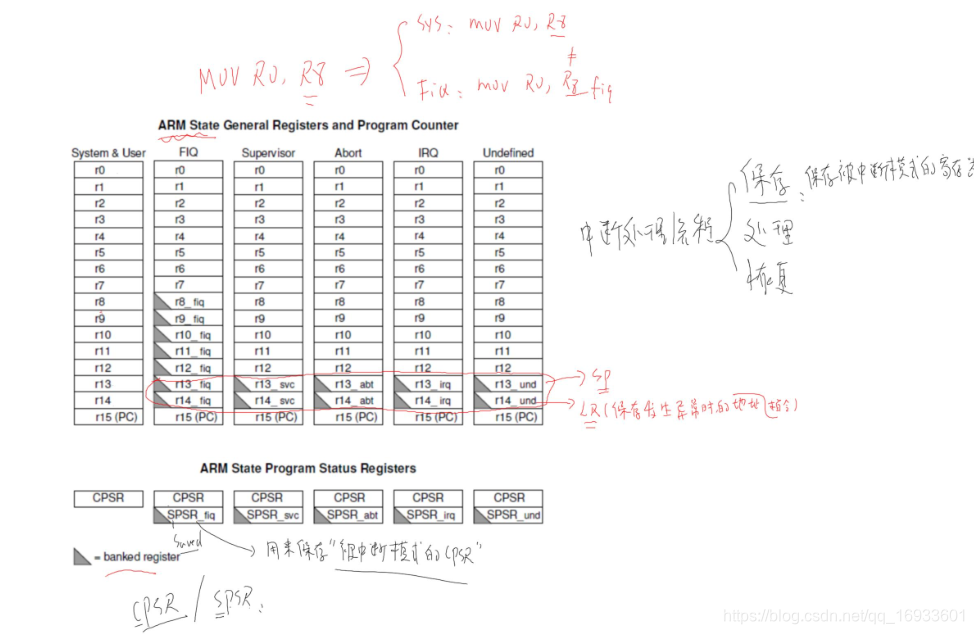

(3)在七种模式下,都可以访问到r0到r15寄存器。灰色的三角形表示这个模式下专属的寄存器,同样的代码在不同模式下访问的寄存器可能不同。五个模式下,都最少有r13和r14两个专属寄存器,r13用作栈,r14为lr寄存器,用作保存发生异常时指令地址。

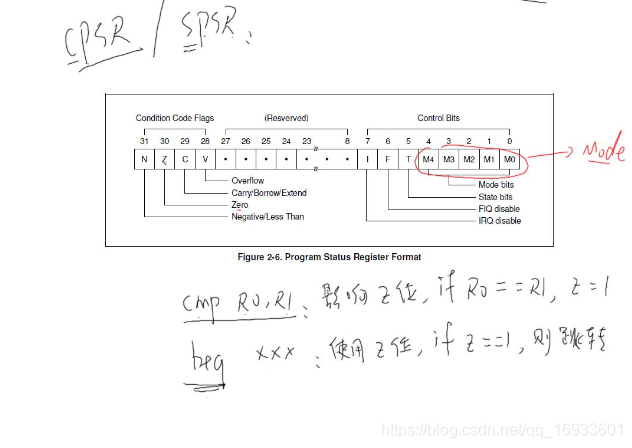

(4)CPSR(Current Program Status Register)/SPSR(Saved Program Status Register)寄存器如上图。CPSR在任何处理器模式下被访问。它包含了条件标志位、中断禁止位、当前处理器模式标志以及其他的一些控制和状态位。每一种处理器模式下都有一个专用的物理状态寄存器,称为SPSR(备份程序状态寄存器)。当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断退出时,可以用SPSR来恢复CPSR。由于用户模式和系统模式不是异常中断模式,所以他没有SPSR。当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。SPSR用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。

(5)M4-M0表示当前CPU处于哪一种模式,M4-M0值所对应的含义如下表。BIT5 表示CPU工作于ARM STATE还是THUMB STATE。BIT6为1所有的FIQ禁止。BIT7为1禁止所有IRQ.BIT27-28保留位。BIT31-BIT28为状态位。

(6)进入异常处理

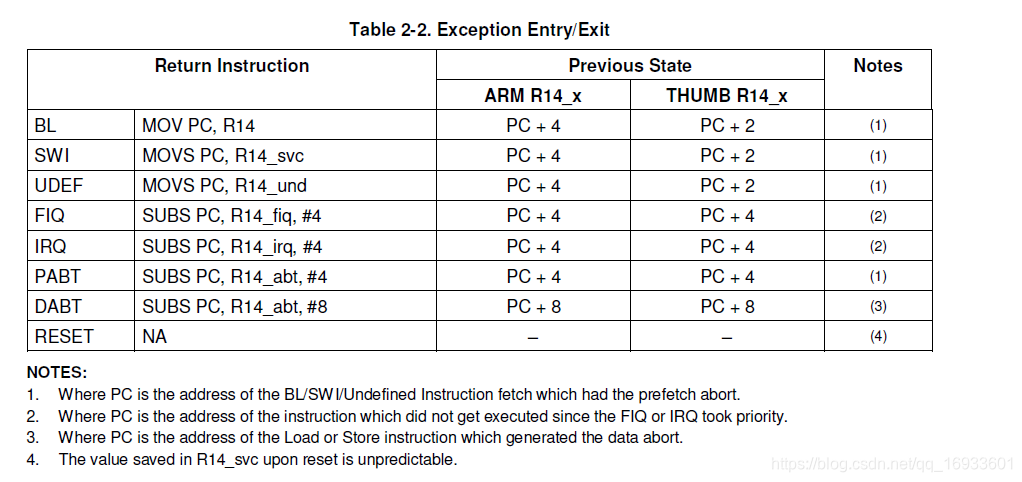

a.相应链接寄存器(LR寄存器)保存下条指令的地址。如果在ARM 状态进入异常,下条指令的地址将会复制到链接寄存器(当前PC+4 或PC+8,由异常决定。详情见表2-2)中。如果在Thumb 状态进入异常,写入链接寄存器的值则为当前PC 偏移一个值,这样异常返回后程序能从正确的位置恢复。这意味着异常处理不需要确定异常是从什么状态进入的。例如,在SWI 的情况,无论是在ARM 状态还是Thumb 状态执行SWI,MOVS PC,R14_svc 语句都将返回到下一条指令。

b.复制CPSR 的内容到相应SPSR 中。

c.根据异常类型强制将CPSR 模式位设为某一个值。

d. 强制PC 从相关异常向量处取下条指令。通常也会置位中断禁止标志位,以防止不同的难处理的异常嵌套。如果一个异常发生时处理器处于Thumb 状态,当装载异常向量地址到PC 时会自动切换到ARM 状态。

(7)离开异常处理

当异常结束,异常处理程序将会:

a. 将链接寄存器(LR寄存器)适当减去一个偏移量并放入到PC 中。(偏移量由异常类型决定)

b. 复制SPSR 的内容返回给CPSR 中。

c. 如果在异常进入时置位了中断禁止标志位异常,清除中断禁止标志位。

注意:不需要在异常结束时切换回Thumb 状态,因为在异常前会立刻保存CPSR 中T 位的值到SPSR 中,并在退出异常时从SPSR 恢复到CPSR 中。